引言

近年来,宽带接入技术得到了飞速的发展,其中非对称用户数字线路技术(ADSL)能利 用现有的电话网络资源,具有投资少见效快等优点,成为向B - ISDN 的最佳过渡形式之一。 在ADSL系统中,由数字用户接入复用器(DSLAM)完成ATM的终结和路由,该模型分为4 层,自上而下分为高层、AAL层、ATM层和物理层,这里高层是指RFC1483及其以上各层, AAL层又分为拆分与组装子层(SAR)和汇聚子层(CS)两个子层,ATM层主要完成信元 复用/解复用、有关信元头的操作以及流控等功能,UTOPIA(ATM的通用测试和操作物理接 口)位于ATM层和物理层之间,规范ATM层和物理层之间的信号电平和时序定义,物理层 的主要任务是物理线路编码和信息传输。当前,ATM SAR功能和UTOPIA接口由专用通信处 理芯片MPC866处理器来完成,成本较高功能固定,灵活性较差。针对特定的AAL5业务采 用FPGA芯片来实现AAL层中SAR子层功能和ATM层功能,,即在通用微处理器的环境中实 现ATM接口,增强产品的灵活性,同时降低成本,对替代专用通信芯片具有较强的实际意义。

1 ATM 协议概述

ATM 是一个分组协议,利用异步传输模式规程,来自不同信源的数据经由相同的物理 信道发送,所设计的协议满足不同用户应用的需要。

ATM 协议栈,为了有效地处理不同的业务,协议被构造为层次体系结构,每层实现特 定的功能,图1-1 显示了通用的协议栈。高层协议包括应用层、表示层、传输层和网络层。 应用层的例子有用于传送文件传输协议、简单邮件传送协议(SMTP)、提供虚拟终端服务 的Telnet 协议等,传输控制协议(TCP)和Internet 协议(IP)则分别是传输层协议和网络 层协议。

ATM 传送信息的基本载体是ATM 信元,信元长度为53 字节,分为信头和净荷两部分, 信头为5 字节,净荷为48 字节。ATM 层主要完成信元复用/解复用,有关信头的操作,以 及流量控制。信元复用/解复用在ATM 层和物理层的TC 子层接口处完成,发送端ATM 层 将具有不同VPI/VCI 的信元复用在一起交给物理层;接收端ATM 层识别物理层送来的信元 的VPI/VCI,并将各信元送到不同的模块处理,如识别出信令信元就交控制面处理,若为 OAM 等管理信元则交管理面处理。信头操作指VPI/VCI 翻译,翻译的依据是连接建立时所 分配的VPI、VCI 的值。

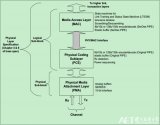

一对一模式下,如何实现物理层-ATM 层-AAL 层间简单的ATM 协议,如何满足备 用链路或多种类型的物理层共享一个ATM层的需求,如何在同一ATM层上同时支持AAL1、 无连接数据服务(AAL3/4)和面向连接数据服务?为此,提出了UTOPIA,即ATM 的通用 测试和操作物理接口(Universal Test and Operations PHY Interface for ATM)。 UTOPIA 是连接ATM 层和物理层的接口,允许物理层以不同的速度在不同的媒质上进 行数据传输,它包括收发数据端口、控制信号和地址信号。

UTOPIA LEVEL1 和LEVEL2 主 要在地址信号的定义上有所不同,其中LEVEL1 未定义地址信号,主要针对单个物理通道 (Single-PHY)的情况,最大工作频率25MHz,支持物理层传输速率达到155Mbps,能够 很好地支持OC-1、OC-3 等同步数字网的典型传输速率;LEVEL2 针对多个物理通道 (Multi-PHY)的情况,比LEVEL1 多了两组地址信号,最多支持31 个PHY 端口(地址0~ 30,地址31 起端口分隔作用),最大工作频率50MHz,支持物理层传输速率达到622Mbps, 能够很好地支持OC-12、OC-12c 等同步数字网的典型传输速率。

2 ATM SAR 及UTOPIA 实现

针对 AAL5 业务类型,方案设计内容包括用FPGA 芯片实现UTOPIA 接口的读、写时 序控制、实现ATM SAR 功能及完成FPGA 与ARM 处理器上连通信。该设计实现的全部功 能都包括发送和接收两个方向,其中UTOPIA 接口需满足ATM Forum 提出的Level1 和 Level2 标准。根据数据发送与接收的流程来划分功能模块,分为CS 子层数据存储模块、ATM SAR 模块和UTOPIA 接口模块,发送和接收过程均为独立的模块。

2.1 总体方案概述

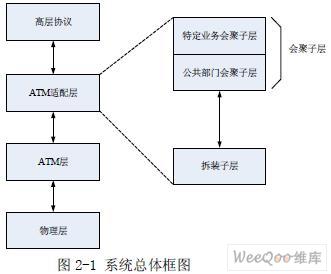

如图 2-1 系统总体框图可知,FPGA 完成的工作包括对UTOPIA 总线的读写时序控制、 实现ATM SAR 功能和与ARM 处理连接。设计实现的全部功能都包括发送和接收两个方向, 详细流程如下。

(1)发送流程:FPGA 存储器接收CS 子层发送来的CPCS-PDU 包,将数据拆分成48 字节的SAR-PDU,然后加上5 个字节的信元头,得到53 字节的信元存入发送存储器中,由 FPGA 控制UTOPIA 接口发送时序发送到物理层去。

(2)接收流程:由FPGA 控制UTOPIA 接口接收时序接收来自物理层的53 字节信元 存入接收存储器中,剥去信元头,由信元头的PT 域指示数据的开始、中间和结束,将接收 到的信元还原成完整的一个CPCS-PDU 包存入FPGA 存储器后发送给CS 子层。

2.2 发送流程模块设计

根据数据发送的流程来划分功能模块,分为 CS 子层数据的存储模块、ATM SAR 模块 和UTOPIA 接口发送模块三个主要功能模块。

CPCS-PDU 存储模块:实现:CPCS-PDU 存储模块输入数据宽度为16 位,输出数据宽度 为8 位,有可读/写、片选信号和地址总线。上层先查询RAM 的可写(WR)信号有效时, 将CPCS-PDU 包发送到16 位数据总线上,一个包发完后置RAM 的片选(CS)信号为无效; RAM 将数据线上的数据顺序存入,并对PDU 包的字节数计数,用RAM 的头两个字节存放 包的长度,3~6 字节存入VPI/VCI 值。一个PDU 包存入后置可写(WR)信号无效,置可 读(RD)信号有效。

SAR 拆分和ATM 模块实现:首先在ATM 层创建一发送FIFO,用来存放ATM 层生成的 信元。在发送双口RAM 可读的状态下,从CPCS-PDU 存储器读出头2 个字节(即数据包的 长度)与48 比较,大于48,生成中间信元;等于48 生成末尾信元,存入FIFO,准备发送。

UTOPIA 发送模块实现:UTOPIA 接口实现采用信元级握手传输方式,它是以信元为单 位进行传输,传输中的控制信号是以信元为基础的。设计一个发送控制模块,通过地址信号 轮询PHY 层状态,接收来自ATM 层的UTOPIA 控制信号、物理层的控制信号以及发送FIFO 的状态信号,控制信元一个一个地从ATM 层发送到物理层,时序要求满足ATM 论坛关于 UTOPIA 接口Level1 和Level2 标准。

2.3 接收模块流程设计

根据数据接收的流程来划分功能模块,分为UTOPIA 接口接收模块、ATM SAR 组装模 块和接收SAR-PDU 存储模块三个主要功能模块。

UTOPIA 接收模块模块实现:首先在ATM 层创建一个接收FIFO,再设计一个接收控制 模块,通过地址信号轮询PHY 层状态,接收来自ATM 层的UTOPIA 控制信号、物理层的 控制信号以及接收FIFO 的状态信号,控制信元一个一个地从物理层传送到ATM的FIFO 中。

ATM和SAR 组装模块实现:在SAR-PDU存储器可写的状态下,不断读入信元接收FIFO 的53 字节数据,剥去信元头还原为SAR-PDU,由信元标识PT 来判断SAR-PDU 是中间还 是末尾数据包,并计算CPCS-PDU 包长度,最后在SAR-PDU 存储器中存入一个完整的 CPCS-PDU 包,包的长度存入存储器的头两个字节中。

接收 SAR-PDU 存储模块实现:接收SAR-PDU 存储模块输入数据宽度为8 位,输出数据 宽度为16 位,有可读/写、片选信号和地址总线,如图4-8。可写(WR)信号有效时,RAM从第六个字节开始顺序存入SAR-PDU(头2 个字节放包长,后4 个字节存放VPI/VCI 值), 直到存入最后一个SAR-PDU,RAM 头两个字节存入CPCS-PDU 包的长度,置可写(WR) 信号无效,置可读(RD)信号有效,此时一个完整的CPCS-PDU 包已经存好,供CS 子层 读取。

3 软、硬件调试

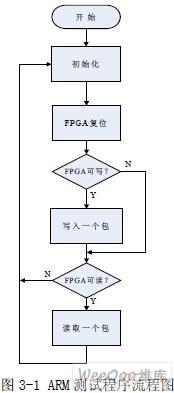

编写基于ARM7处理器μcLinux 系统下的CPCS-PDU 数据包的收发程序,在Red Hat9.0 系统中(ARM 工具链已建立好)编译通过后,下载到在ECPB 板上运行。程序主要完成ARM 处理器对外设FPGA 的复位、读、写等操作,流程图如图3-1 所示。

QuartusⅡ软件的SignalTapⅡ逻辑分析仪可以用来采集FPGA 内部节点和I/O 引脚信号, 通过JTAG 端口送往逻辑分析仪显示。调试过程中主要利用SignalTapⅡ逻辑分析仪和示波 器,通过收、发数据包来验证FPGA 中数据处理的正确性。

调试步骤如下:

(1)ARM 测试程序和FPGA 程序下载;

(2)ECPB 板ARM 初始化配置、CMTC 板UTOPIA 接口初始化等;

(3)程序运行; 按照上述步骤验证 FPGA 芯片设计是否满足任务需求。经过发送和接受数据包测试后得 出,经反复数据测试比对,FPGA 工作正常,满足任务要求。

4 结束语

本文的创新点在于对 ATM 技术和UTOPIA 接口时序进行了深入、系统的分析与研究, 以替代现有专用通信处理器为目标,提出了一种采用FPGA 来实现ATM SAR 和UTOPIA 接 口的解决方法。设计好的FPGA 芯片与上层ARM 处理器和物理层CMTC 板对接后应用于 ADSL 测试系统中,在数据接收和发送两个方向,FPGA 均正确完成上述功能,且工作稳定, 具备了专用通信处理器MPC866 同样的功效。作者相信,本文的研究成果,即采用FPGA 在基于ARM 处理器的环境中实现了ATM 接口,对于ATM 应用领域的成本降低和灵活性有 着较大的实际意义,也为替代专用通信芯片迈出了成功的一步。

-

处理器

+关注

关注

68文章

19156浏览量

229075 -

FPGA

+关注

关注

1625文章

21664浏览量

601727 -

芯片

+关注

关注

453文章

50378浏览量

421700 -

ARM

+关注

关注

134文章

9043浏览量

366757

发布评论请先 登录

相关推荐

软件通信体系结构规范下如何实现FPGA的硬件抽象层设计

如何采用FPGA来实现UTOPIA LEVEL2主接口的发送和接收模块?

ATM技术资料

AAL2/AAL5等ATM连接的区别

PCIe物理层接口定义了物理层中的,媒介层和物理编码子层之间的统一接口

采用FPGA芯片实现AAL中SAR层和ATM层功能与接口设计

采用FPGA芯片实现AAL中SAR层和ATM层功能与接口设计

评论