引言

雷达目标检测与信息录取是雷达系统与雷达信号处理系统的重要组成部分,超大规模集 成电路的发展,特别是高性能的信号处理器(DSP)架构的提升和大规模可编程逻辑器件的 出现,为雷达信号数字化处理带来了新的突破。在高速数据采集方面,目前流行的方式是采 用高速A/D 转换器件,主要的优点是信号精确度高,但高精度的同时不可避免的带来了大 量实时数据流,对后端的信号处理系统将提出严格的要求,本系统采用了目标信号前言采集 的方式,与A/D 采集相比本方法虽然存在一定的采集精度差异,但该方法的数据采集量相 较前者有非常显著减少。本文利用现代最新发展的大规模集成电路技术和数字处理技术,将 FPGA 和PC/104 相结合实现对原雷达原始信号的采集与处理。

1 系统总体设计方案

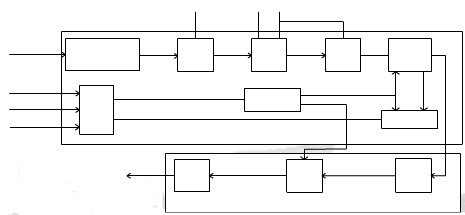

本文设计了一种基于船载导航雷达的船舶防碰撞系统。通过对原雷达的适应性改装,为 雷达增加目标威胁度*判单元,提高雷达对目标的自动识别能力,系统通过实时监视全方位 的目标并计算运动参数以确定目标威胁等级,当检测到危险目标时,输出报警信号。该系统 实现了对原雷达的功能的延伸与扩展。系统的组成框图如图1 所示。

图1 系统组成框图

系统主要由数据实时采集模拟电路单元模块、信息采集数字电路单元、RAM 存储单元、 目标航迹处理分系统等组成。数据采集模块通过引入探测雷达的船首信号、角度信号与距离 探测信号,对雷达视频回波信号进行同步采集,在本系统中采用了目标前言采集;FPGA 内 部通过软件设计主要完成对采集到的信号进行门限检测角度、距离坐标定位形成雷达点迹数据;存储模块主要完成对录取的目标坐标信息的实时存储,由于该系统数据采集部分的数据 量并不大,故该存储模块则可以直接在FPGA 内部实现,不需要外接存储设备。数据处理 分系统通过对点迹数据进行目标识别、目标跟踪处理获得目标航迹,并计算目标航迹参数, 根据所设定的参数对目标威胁度进行动态*判,并输出报警信号。

2 系统主要工作过程

系统的基本处理过程如下图2 所示 视频信号展宽、放大:输入视频信号为未经任何处理的雷达信号,由于发射脉冲宽度为 0.8μs,实际回波的脉冲宽度在1~2μs 水平(由于接收机的通带特性和目标纵深引起),为 保证抽样不会漏信号,可考虑展宽到2μs 以上,输入视频信号的幅度在0.5V 左右的水平, 可通过放大使之便于信号处理(3V 左右)。

图2 系统主要工作过程

同步整形:对输入的探测信号和船首信号进行整形,使其幅度、宽度、脉冲形状符合信 号处理要求;门限电路:根据输入的门限设定值(预设可调量),在输入视频信号(前言) 超过门限而且满足一定宽度(预设可调量)时,输出一个计数控制信号到计数器1;计数器 1 将计数控制信号输出到计数器2,同时开始计数,计数频率为5MHZ。在计到宽度限定值(预 设可调量)之前,如果有新的计数控制信号输入,重新开始计数,但不向计数器2 输出;计 数器2 在距离起始脉冲到达时开始计数,计数的频率为5MHZ,每输入一个计数控制信号, 它输出当前计数值作为目标距离数据到缓存器;计数器3 用于角度信号计数,开始标志为探 测雷达船首信号,每到达一个角度信号脉冲,计数一次,并将数据写入RAM 存储器,作为方 位计数值。

距离起始脉冲是由同步器根据探测信号产生的,同步器还产生一个距离结束信号,距 离起始与结束信号分别标志距离测量的开始与结束,初步考虑开始距离设定为2 海里(可设 定),结束距离设定为36 海里,间隔34 海里(可设定)。其中起始距离的设定主要基于减小 近距离强杂波对处理系统的影响。RAM 存储器对目标距离数据和方位计数值进行存储,每个 距离周期,在距离计数信号的触发下,向PC 机输出并清除存储数据。如果存储器内没有目 标距离数据,则不输出。

3 系统硬件实现

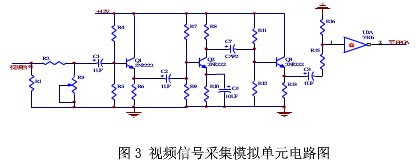

系统硬件部分有PC/104CPU板、数据采集板数字单元、数据采集板模拟单元三部分组组 成。PC/104CPU板采用主频200M、内存64M、集成显卡的基本硬件配置;数据采集数字单 元采用ALTERA公司的Cyclone系列FPGA 芯片EP1C6 ,其配置芯片为ALTERA公司的 4Mbits 容量PROM 芯片EPCS4,以主动串行方式对FPGA 进行上电配置;数据采集的模拟 单元主要由ULN2803、DM7406、2N2222等集成芯片。视频信号处理部分硬件设计如图3所 示。

图3 视频信号采集模拟单元电路图

图中C1、C2、C3 实现对信号的耦合作用。可调电阻R3 实现对信号放大幅度的调节。 经该电路转换后的视频信号为适合于数字处理的单个数字脉冲信号。实现了对回波信号的实 时采集。

4 系统软件实现

4.1 FPGA 程序的设计

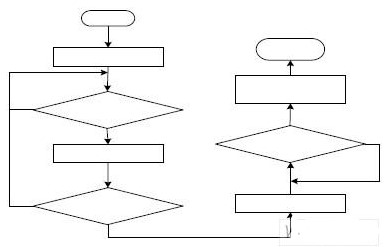

在FPGA 内部主要完成目标坐标信息的提取,实时存储与传输控制模块工作流程图如图 4 所示。

图4 FPGA 工作流程图

采集系统与PC104 之间的数据交换采用PCI 总线实现。具体方法为:在FPGA 内部配 置一片2K×16bits 的双口RAM。当检测到回波目标时,将此时刻的距离、方位计数值存入 RAM 存储器,作为该目标的坐标信息。当检测到距离结束信号时则将该段时间内所有目标 的信息数据打包发送至PC104 进行后续的信号处理,如果再探测周期内没有回波目标则不 传送数据。

4.2 用户程序设计

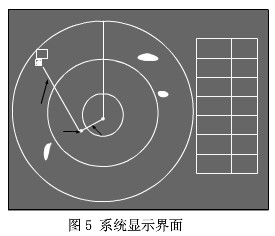

用户程序主要完成雷达采集信号的航迹处理、参数计算、实时显示和实时存盘。本系统 的用户程序采用VC++作为开发工具,在WINDOWS操作系统下完成。工作过程如下:首先 通过PC机通过PCI总线接口,将信号采集的参数进行设置并存入FPGA内的存储单元,FPGA 则根据这些设定的参数对目标信号进行采集;PC机在接收到中断信号后,对RAM存储器内的 距离、方位数据进行读取并处理。然后用户可以通过显示器观察目标回波信号,同时将目标 数据以二进制格式实时保存在PC机上的磁盘阵列上,供Matlab等软件进一步分析和对交通事 故重现使用。系统的显示界面如图5所示。

图5 系统显示界面

5 总结

本文通过FPGA+PC/104 相结合,对来自雷达接收机的原始视频信号进行采集、与数字 化处理,使雷达具备了目标威胁等级*判功能,且全程无需人工干预。实现了原雷达功能的 功能扩展与延伸。大规模可编程逻辑器件与工控PC机相结合的方案,整个系统具有体积小、 实时数据处理、以及方便的进行在线系统的改进与升级的特点。 作者的创新点:该系统运用FPGA+PC/104及其扩展模块实现数据采集、处理。系统克服了 传统PC机的缺点,具有体积小、功耗低、可靠性高等特点。

-

dsp

+关注

关注

553文章

8019浏览量

349245 -

FPGA

+关注

关注

1629文章

21752浏览量

604118 -

报警系统

+关注

关注

5文章

647浏览量

75213

发布评论请先 登录

相关推荐

基于FPGA+PC104实现新型防碰撞报警系统的数据处理功能

基于FPGA+PC104实现新型防碰撞报警系统的数据处理功能

评论