FPGA技术、低成本光学器件以及无源架构都为无源光网络(PON)以及这些网络的演进做出了巨大贡献。系统级OEM厂商不断发现,FPGA能够提供技术性设计和经济方面的优势,特别是在网络侧的中心局(CO)基础设施端。

2002年之前,低性能的FPGA主要用于原型创建工具。而如今的FPGA具有强大的性能和丰富的功能,能更好地满足日益提高的PON设计需求。另外,更低设计成本、灵活和可扩展的FPGA对于竞争激烈的无源光网络市场来说也是关键。

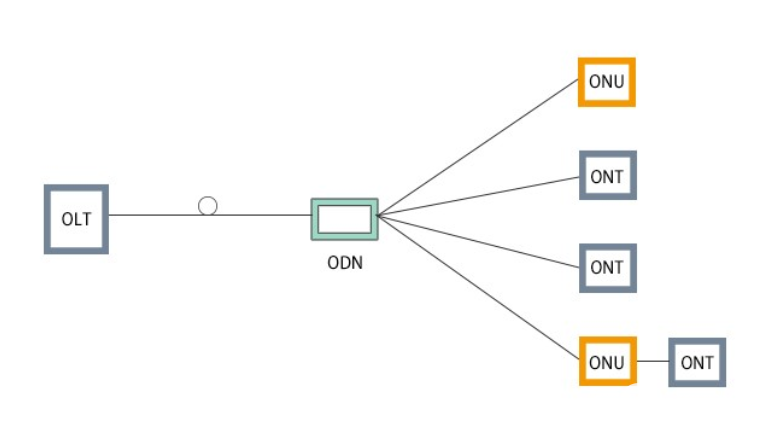

PON是点到多点(P2MP)光纤到驻地(FTTP)的网络拓扑技术,也常被定义为光纤到路边(FTTC)和光纤到家庭(FTTH)。在PON定义中采用了FTTP或CPE(用户驻地设备)。通过无需供电或无源的光分离器,单路光纤可以服务于多个驻地。分离器通常为32路,不过有时会多达64路。一个PON网络包括一个位于业务提供商中心局的光线路终端(OLT)和众多的光网络终端(ONT),后者也被称为进入驻地的光网络单元(ONU)。

下行的OLT信号以广播方式送到共享一根光纤的各个ONT。目前的PON标准规定下行的数据率高达2.5Gb/s(Gbps)。上行信号则利用时分多路(TDM)技术组合在一起。与数字用户线(DSL)或电缆相比,PON具有无可比拟的带宽优势,可以提供高速三重播放业务(语音,视频和数据)。

根据Infonetics的预测,到2010年,北美和亚太地区PON用户的年度复合增长率可高达150%。吉比特PON(GPON)在北美正在取得强劲的增长,而以太网PON (EPON)主要用在日本。日本政府的津贴政策正在推动PON市场的逐年增长,而中国正在仔细权衡EPON和GPON的优劣。

宽带PON(BPON)或者国际通信联盟(ITU-T) G.983x是流行的美国PON标准。其最大下行数据速率为622Mb(Mbps),上行数据率为155 Mbps。安装在光纤链路中的无源分离器允许一根光纤最多连接64个家庭。今年,GPON或ITU-T G.984,即BPON的演进版本,有望进入更多的美国家庭。它支持TDM和分组数据,下行和上行数据率最高分别可达2.5 Gbps和1.24Gbps。GPON的关键优点是无需增加IP就能支持交换式数字视频和原有的TDM语音。

成本敏感性

不管哪种标准,用于提供宽带接入的PON系统具有高度的成本敏感度。DSL是目前使用最为广泛的宽带接入技术。由于具有庞大的用户数量,DSL为每端口设置了极低的成本标杆。因此,DSL对PON提出了强大的挑战。不过PON系统在过去两年里在降低成本和增强功能方面也取得了长足的发展。

随着PON市场的发展,系统级OEM厂商和运营商正密切关注其成本的降低,尤其是OLT的成本。在ONT侧,数量有望增加到百万台,因为PON将为数以百万计的驻地提供服务。许多ASIC和ASSP供应商盯上了ONT,并提供各种芯片产品。由于ONT是一个量很大的市场,ASIC和ASSP芯片厂商能够帮助降低成本,从而帮助系统级OEM和运营商提供较低的价格。

另一方面,OLT系统数量为数万台而非数百万台,故成本较高。例如,PON家用调制解调器的成本为100到300美金,而PON网络中OLT系统的成本则高达10000美金。实际上,OLT的成本对运营商来说极为关键,因此大都集成了多端口线路卡,可以处理越来越多的驻地数量。

OLT线路卡的期望数量在可预见的未来将保持在中等到较低的水平,这有两个原因。首先,64个ONT只需要一个OLT,其次,每个OLT线路卡可以支持4到8个OLT端口。于是,OLT线路卡的数量和所用的元器件要远远少于大批量的ONT设备。

设计复杂性使成本问题更加严重。PON OLT和ONT拓扑结构是一个共享的媒体架构,这为系统OEM设计师提出了挑战。由于PON标准中采用了TDM技术,因此OLT和各个ONT之间的交互非常复杂。TDM用来共享不同驻地间的容量。早期的PON标准使用静态TDM,因此每个驻地接收相同的容量。

但是,最新的PON标准要求能够根据驻地的需求变化,为不同的驻地动态分配容量。这种动态带宽分配(DBA)功能需要利用ONT和OLT之间传送的信令通知OLT每个ONT所需的容量。OLT也需要将分配的容量通知给每个ONT。该协议基于从ONT到OLT的请求消息。OLT确定最佳的容量分配,并用确认消息予以响应。

另外,与较简单的点对点以太网端口不同的是,由于存在动态TDM要求,PON端口是一种更复杂的P2MP。因此OLT端口必须在多个ONT驻地之间进行连续切换。每个ONT分配得到32或64个可用时隙中的一个与OLT进行交互通信。OLT必须快速且连续地依次锁定到每个ONT数据流上,用的是众所周知的突发模式。为了支持这一极快的锁定方案,需要一个高度专用的媒体访问控制器(MAC)、串行/解串器(SerDes)以及时钟和数据恢复(CDR)功能。为了协调对每个ONT的访问,PON MAC尤其重要。

图1:DSL和PON拓扑共存。

基于FPGA的设计

针对上述背景,系统级OEM厂商在实现低成本和高效的OLT设计方面可选择性很少。一种方法是选用ASIC技术。但这种方法的投资成本极高。由于一些原因,ASSP也无法较好地实现。ASSP在支持PON演进需求方面的灵活性有限,缺乏设计可扩展性,并且功耗随着时钟速率的升高而升高。ASSP在提供可竞争的差异化产品方面的能力也很有限,还面临着器件停产的风险。另外,拥有成本也越来越高,上市时间较长。

然而,FPGA却能为OLT的设计提供低成本高效率的开发平台。当设计无缝移植到结构化ASIC进行大批量生产时成本还能进一步降低。这种方法由于省去了大型且耗时的ASIC开发,系统OEM厂商可以省去较大的成本,并缩短上市时间。

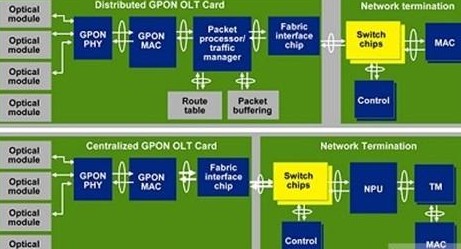

像Stratix这类FPGA器件,能够为实现和集成主要的OLT线路卡功能(见图2)提供所需的高性能逻辑。而且,FPGA也是用于实现CO OLT或者ONT用户驻地端EPON和GPON MAC的可选技术。另外,可以在一片FPGA中集成PHY和MAC,从而在一个芯片上实现虚拟线路卡。FPGA中先进的高效率内核矩阵基于的是被称为自适应逻辑模块(ALM)的创新逻辑单元。

图2:OLT线路卡采用的分布式与集中式架构的比较

-

FPGA

+关注

关注

1635文章

21840浏览量

608419 -

数据

+关注

关注

8文章

7223浏览量

90181 -

PON

+关注

关注

1文章

132浏览量

43831

发布评论请先 登录

相关推荐

RF PON:NGB网络的首选接入技术

实现FTTH网络部署有两种类型的系统介绍

什么是PON(无源光纤网络)、PON的发展及演进

无源光网络技术介绍

什么是有源(AON)和无源(PON)光网络?

采用FPGA器件实现无源光网络(PON)的设计

采用FPGA器件实现无源光网络(PON)的设计

评论