在电子设计领域中,通常要对多路宽带信号进行实时采集、处理和传输。传统的信号采集传输系统,采用专用集成电路控制A/D转换器等外围电路。由于专用集成电路时钟频率低、灵活性差、实时性低、传输速度慢、通用性差等缺点,难以满足对高速宽带信号采集和处理的要求。FPGA具有时钟频率高、速度快、采集实时性高、控制灵活等特点,与A/D转换器等外围电路结合,更适于高速数字信号处理。光纤传输与电气传输相比,具有传输频带宽、通信容量大、传输损耗低、抗电磁干扰性能强、抗辐射能力强、保密性好、重量轻等特点,在通信领域被广泛应用。

文中提出基于FPGA和光纤传输的高速数字信号传输方案。以带有收发器的高性能FPGA为控制核心,控制外围A/D转换器和数据处理,通过光纤媒介进行数据传输,满足高速数字信号实时处理和传输的要求。

1 系统总体设计方案

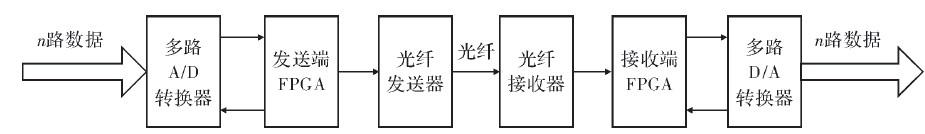

光纤传输系统是以光波为信息载体、光纤为传输媒介,用光来传输信息的传输系统。光纤传输系统总体框图如图1所示,发送端主要由A/D采集、FPGA数据预处理、光纤发送模块组成;接收端主要由光纤接收模块、FPGA数据后处理、D/A转换模块组成。两者通过光纤进行通讯。

图1 光纤传输系统总体框图

在发送端,先将外部输入的模拟信号进行预处理,再通过A/D转换器转化为数字信号送入FPGA进行处理。根据数据传输以及通信协议的要求,FPGA将预处理后的A/D数据进行编码、成帧。然后由FPGA内部的IP核进行并串转换,最后由光收发模块完成电光转换后,通过光纤发送出去。

在接收端,光收发器模块将接收到的光信号转化为电信号,完成高速串行数据到并行数据的转换;然后,将转换后的并行数据送入FPG A,FPGA完成信号的解帧、解码,并进行后处理,该过程是发送端的逆过程。最后,经D/A转换器将接收到的数据恢复成模拟信号。

2 硬件电路设计

2.1 发送端硬件电路设计

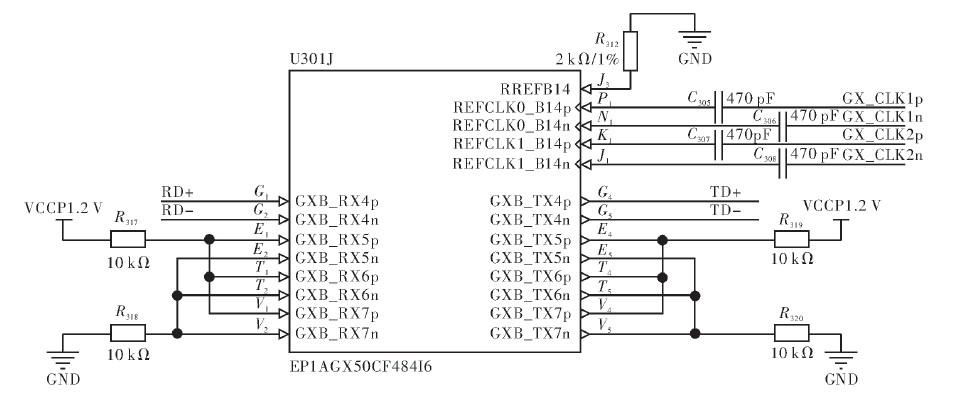

可编程逻辑器件FPGA是主控芯片,是系统的核心,设计选用Altera公司带有收发器的Arria GX系列芯片EP1AGX50CF48416.芯片内部集成了4个收发器通道,传输数据率从600 Mbit·s-1到3.152Gbit·s-1,收发器每通道在2.5 Gbit·s-1时消耗功率仅为125 mW;收发器可利用固定均衡设置来均衡串行通道,实现发送预加重和接收均衡;收发器支持串行环回、反向串行环回以及伪随机二进制序列(PRBS)产生器和校验器。专用收发器接口电路如图2所示。RREFB14接一个2kΩ/1%的参考电阻,其他未使用的收发管脚通过10kΩ电阻到电源或地。

图2 收发器接口电路

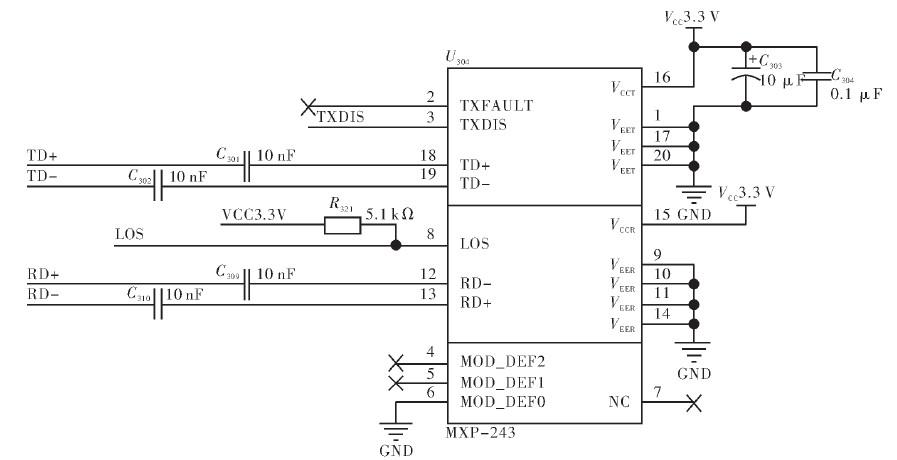

光收发模块选用MXP-243S-X型光收发器,其可处理的数据率为1.25 Gbit·s-1,单电源3.3 V供电,差分LVPECL电平输入和输出,发射和接收部分相互独立。发射部分差分输入阻抗100 Ω,传输光信号波长1310nm.光发射器电路图如图3所示。发射的差分数据接到FPGA的专用收发器的发射管脚G4和G5上,控制引脚直接接到普通L/O管脚,并通过上拉电阻接到电源。

2.2 接收端电路设计

接收端FPGA也选用Altera公司的Arria GX系列芯片EP1AGX20CF48416.光收发模块仍选用MXP-243S-X型光收发器。电路连接只需将图3中的RD+、RD-端口直接接到光收发器TLK1501.

图3 光发射器电路图

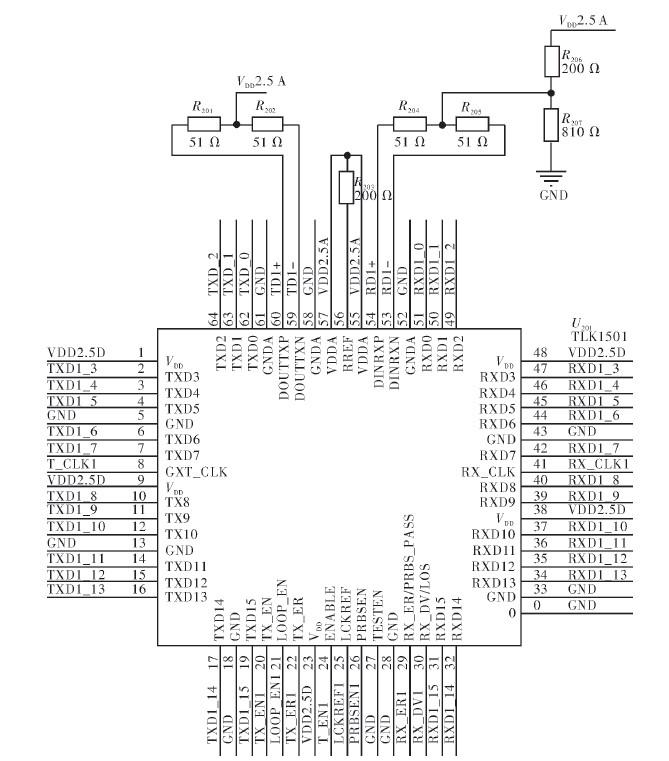

为了与下级系统匹配,设计串行收发器选用TI公司的TLK1501,支持最高1.2 Gbit·s-1的数据带宽。其内部集成有8 B/10 B编码器、并串转换器、差分输入输出接口、8 B/10 B解码器、串并转换器、时钟管理模块等。内部有自检环路,可方便地进行自检,并集成信号丢失检测,支持热拔插,其电路如图4所示。

图4 光接收器电路图

R201,R202,R204,R205为50Ω匹配电阻,R203为参考电阻200Ω,R206和R207提供终端匹配所需要的偏置电压。

3 软件设计

设计采用自顶向下的模块化设计方法,用Verilog硬件语言编程,实现FPGA对光纤接口处芯片、A/D和 D/A转换器等外围电路的控制。

3.1 发送端FPGA程序设计

发送端FPGA逻辑设计主要包括采样存储逻辑、校验、成帧及编码逻辑和光发送器接口逻辑。

3.1.1 采样存储逻辑

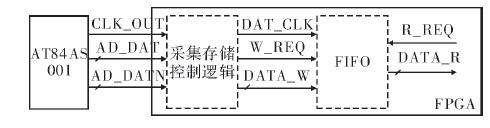

采样存储逻辑完成数据的采集以及实时存储。其逻辑形式及原理框图如图5所示。

图5 采集存储逻辑框图

AT84AS001是ADC芯片。输入的差分数据直接接到FPGA的专用差分引脚。采集存储控制逻辑包括LVDS接收以及数据重组等模块,通过LVDS接收器将双沿时钟变为单沿,数据重组模块进行数据重新排序,还原原始数据流。最后在FIFO中进行缓存。

3.1.2 校验、成帧及编码逻辑

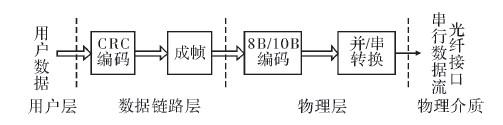

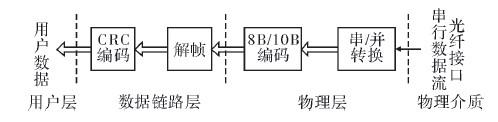

校验、成帧及编码逻辑完成数据格式转换,将处理后的数据进行CRC编码、成帧、8B/10B编码和并串转换。算法流程如图6所示。

图6 校验、成帧及编码算法流程图

3.1.3 光发送器接口逻辑

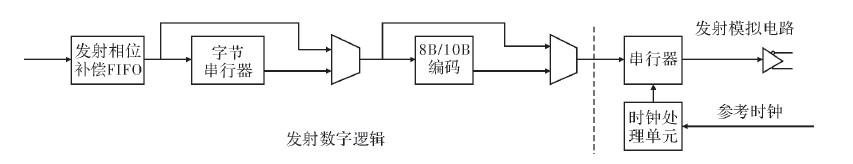

光发送器接口逻辑完成帧数据到高速串行数据流的转换。直接利用FPGA内部的专用收发器,其结构如图7所示。

图7 光发送器接口逻辑

帧数据首先南发射相位补偿FIFO模块进行相位补偿,抵消时钟相位差,然后通过字节串行器将数据转换为8位,接着进行8B/10B编码,并由串行器转换为高速数据流,由专用差分输出口输出。

3.2 接收端FPGA程序设计

发送端FPGA逻辑设计主要包括光接收器接口逻辑和解码、解帧及校验逻辑。

3.2.1 光接收器接口逻辑

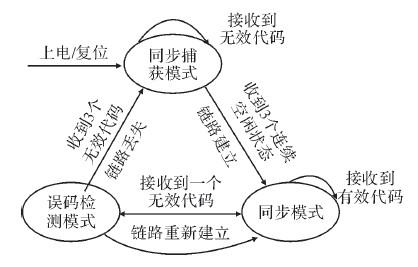

TLK1501有一个状态机,负责监测不同的工作状态,即同步捕获模式、同步模式和误码检测模式。上电或复位后,状态机进入同步捕获模式,当接收到3个连续的IDLE码或载波扩展码或1个有效数据或错误延时,即进入同步模式。在同步模式下进行数据的正常接收与发送。在这个模式下,TLK1501接收到一个无效代码,状态机立即进入误码检测模式。检测模式收到4个连续无效代码时,TLK1501立即重新进入捕获模式。TLK1501同步状态机如图8所示。

图8 TLK1501同步状态机

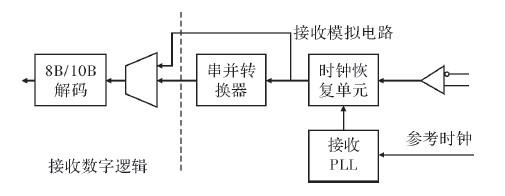

光接收器接口逻辑完成高速串行数据流到低速并行数据的转换。使用串行收发器TLK1501,其结构框图如图9所示。

图9 光接收器接口逻辑

由专用差分端口输入的高速数据经时钟恢复单元进行时钟恢复,串并转换后进行10B/8B解码,最后传给FPGA进行解帧操作。

3.2.2 解码、解帧及校验逻辑

解码、解帧及校验逻辑完成数据格式转换,将接收到的数据进行10B/8B解码、解帧和CRC校验,获得有效数据。算法流程如图10所示。

图10 解码、解帧及校验算法流程图

4 实验仿真及波形

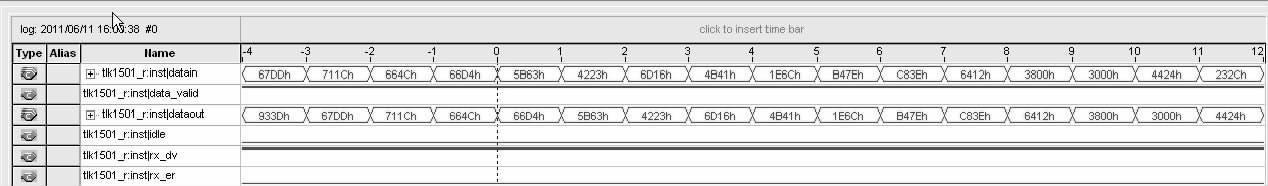

图11是TLK1501稳定传输数据效果。由图可以看出,TLK1501实现了实时稳定传输数据。

图11 TLK1501稳定传输数据效果图

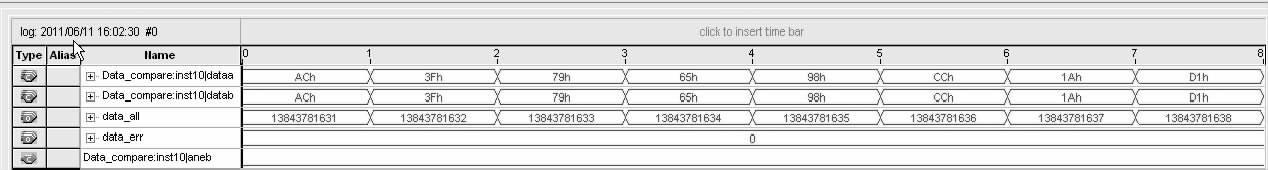

图12是数据收发误码测试的仿真波形图。data_all是到当前时钟为止已测试的数据总量,data_err是到当前时钟为止传输错误的数据总量,可以看出,在传输了百亿个数据后,误码仍为零。

图12 数据收发误码测试的仿真波形图

5 结束语

研究设计了一种基于FPGA和光纤通讯的高速数字信号传输方案。实验结果表明,该方案实现了高速数字信号的实时传输,具有信号传输误码率低、系统工作性能稳定、抗干扰性强的优点,由于实际需要,系统在接收端采用TLK1501,这就限制了光纤传输的速率,若采用FPGA内部的光纤收发模块,则可进一步提高传输速率。

-

FPGA

+关注

关注

1638文章

21857浏览量

609730 -

芯片

+关注

关注

459文章

51726浏览量

430962 -

转换器

+关注

关注

27文章

8809浏览量

149326

发布评论请先 登录

相关推荐

数字光端机传输的是数字信号

怎么利用FPGA和光纤传输设计高速数字信号传输系统?

利用FPGA怎么实现数字信号处理?

数字信号处理的FPGA实现

基于FPGA技术的光纤传输系统的设计与实现

采用FPGA和光纤媒介共同实现高速数字信号传输系统的设计

采用FPGA和光纤媒介共同实现高速数字信号传输系统的设计

评论