引 言

近些年来,随着电子元器件价格的不断降低和数字信号处理器(Digital Signal Processor,DSP)性能的不断提升,以DSP为核心的嵌入式实时图像处理技术在目标跟踪、机器人导航、辅助驾驶、智能交通监控等领域获得了越来越广泛的应用。由于图像的实时处理与图像数据的实时采集、存储和传输密切相关,因而各模块间的无缝连接与高效配合是嵌入式图像处理系统设计过程中的关键问题。综合考虑系统的实现成本、实时性以及实际应用,在嵌入式图像处理技术的许多应用领域中,如视频监控以及视觉客流检测等,由于对图像质量要求不是很高,处理算法相对简单,采用低端DSP(如Ti公司的C5000系列等)就可以完成相应的图像处理任务,面向这些实际应用领域的嵌入式图像处理系统完全可以采用低端DSP作为系统的处理核心,因此将以低端DSP为核心构建面向客流检测实际应用的嵌入式图像处理系统。另外,与其他图像数据传输方式(如串口、并口和USB等)相比,以太网接口具有传输速度快,成本低廉,开发简便以及可以实现远程控制等一系列优点,因而提出的嵌入式图像处理系统的图像传输部分将采用基于TCP/IP协议的以太网传输技术实现系统图像数据的远程传输功能。

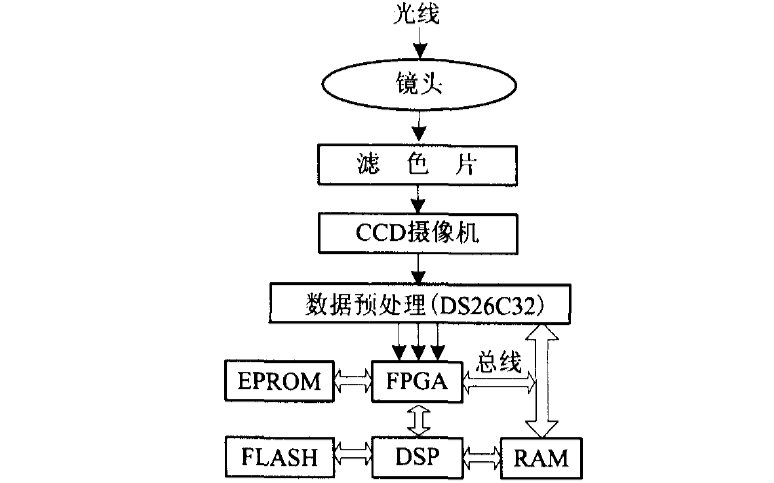

1 系统构成

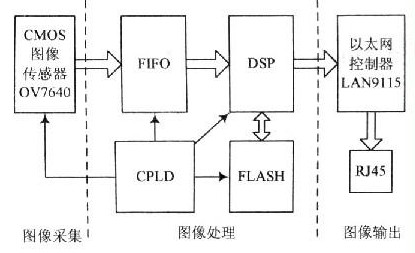

这里提出的基于DSP的嵌入式图像处理系统由图像采集与存储、图像处理和图像传输3部分组成,组成框图如图1所示。选用CMOS图像传感器OV7141完成系统的图像采集功能,选用TMS320VC5416DSP完成系统的图像处理与分析,采用FIFO存储器IDT72V04作为图像存储的缓冲区,采用10兆/lOO兆自适应网络控制器LAN9115实现图像数据的以太网传输功能,系统各模块间的逻辑控制由CPLI)EPM3064A实现。

2 系统的硬件实现

2.1 芯片介绍

考虑到视觉客流检测应用中的图像处理只涉及灰度图像,因而提出的嵌入式图像处理系统可以直接采用黑白图像传感器。这里选用Omnivision公司的黑白CMOS图像传感器OV7141作为图像采集芯片。该芯片工作电压为2.5 V,分辨率为640×480,工作频率为27 MHz,每秒钟能输出30帧(VGA模式)或者60帧(QVGA模式),内部整合模数转换(A/D),自动增益控制(AGC),SCCB总线控制端口等,可直接输出8 b图像数据。

图像处理芯片采用TI公司的TMS320VC5416定点DSP,其内部采用一种改进型的哈佛总线结构(1条程序总线、3条数据总线和4条地址总线),数据总线宽度为16 b,最大寻址空间为64 K×16 b。程序总线宽度为23 b,最大寻址空间为8 M×16 b。片内有128 M×16 b的RAM(其中包括64 M×16 b的单周期双访问DARAM和64 M×16 b的单周期单访问SARAM),6通道DMA传输控制器,3个带缓冲器的串行通信接口(McBSP)。分开的数据和指令空间使该芯片具有高度的并行操作能力,在单周期内允许指令和数据同时存取,再加上其高度优化的指令集,使得该芯片具有很高的运算速度,最高可达160 MIPSE。

FIFO采用IDT公司的IDT72V04,它是异步的先进先出缓存器,容量为4096×9 b。供电电压为3.3 V,它有3个状态输出信号可用于图像数据存储与读取控制,即全满信号/FF、半满信号/HF和空信号/EF。CPLD采用ALTERA公司的MAX3064A,可使用门数1250个;宏单元64个;逻辑阵列块(LAB)4个;最大可使用输入输出(I/O)管脚数64个;最大工作时钟频率为222.2 MHz;核供电和I/O供电都为3.3 V。LAN9115是SMSC公司的第二代10兆/100兆非PCI以太网控制器,LAN9115设计有大容量的存储器缓冲器,快速总线周期时间和内置的流控制支持,LAN9115支持高的数据速率,几乎没有包的损失,支持多种高清晰度视频。LAN9115的主要性能:功率管理;支持LAN叫醒,使网络能把消费类电子产品从睡眠状态中叫醒;多种低功耗模式;能防止接收存储器溢出;内置支持流控制;简单SRAM系统接口;能与任何的嵌入处理器接口。

2.2 DSP与FIFO存储器的无缝连接与图像采集的实现

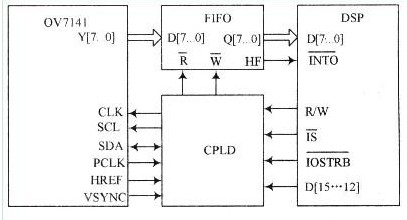

FIFO与DSP和OV7141的无缝连接如图2所示。OV7141的工作频率是27 MHz,每秒钟能输出30帧(VGA模式)或者60帧(QVGA模式)。由于DSP性能有限,而且实际上很多情况下也不需要如此高的帧率,因此并不是所有采集到的图像数据都需要DSP进行处理(例如在视觉客流检测系统的实际应用中只要求每秒钟能处理5帧即可),但是必须保证DSF进行处理的图像为一幅完整的图像。可以利用OV7141的3个输出信号来完成这个功能,分别是PCLK(像素时钟信号)、VSYNC(场同步信号)和HREF(行有效信号)。并且OV7141可通过改变片内控制寄存器的值来调整输出图像的窗口大小,窗口可在4×2到652×482像素之间任意选择。HREF、只在所选择窗口内的像素信号输出时才置高电平,这使得图像的非完整模式下的处理也变为了可能。另外,0V7141的片内控制寄存器配置功能由SCCB总线实现,由于DSP不具有SCCB总线接口,因而为了通过DSP实现对0V7141的寄存器配置,利用DSP的2根数据线DO和D1借助CPLD实现sCcB总线时钟线SCL和数据线SDA的模拟以实现虚拟SCCB总线。

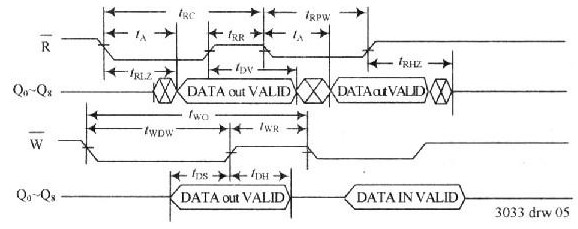

控制FIF0的信号主要是写信号和读信号,它们都由DSP根据FIF0的状态信号及DSP对图像的处理结果来控制对FIFO的读/写。读/写操作时序如图3所示。CM0s图像传感器采集获得的图像数据在CPLD控制下逐行写入FIFO,当FIFO的存储容量达到半满时,FIFO的半满标志位以外部中断方式通知DSP,DSP,检测到外部中断后开启DMA,利用DMA通道将FIFo中的图像数据搬移到DSP的片内图像缓冲区中。需要注意的是,在DMA从FIFO搬运图像数据的过程中CMOS图像传感器并没有停止向FIFO写入图像数据,由于CMOS写入FIFO速度Vw。比DMA从FIFO中读出数据的速度Vr慢(Vw=(1/2)Vr),使得CMOS和DMA在对FIFO进行双向访问时FIFO的实际存储容量始终保持在0和最大存储量之间,既不会上溢也不会下溢;从而保证一帧完整的图像可以被DMA控制器顺利的转移至DSP的片内图像缓冲区中。当一帧完整的图像搬运完成后,DMA会开启处理使能标志,当DSP发现处理使能标志开启后将从片内图像缓冲区中获得图像数据以完成图像处理算法,在DSP进行图像处理的同时,DMA控制器可以同时进行下一帧图像数据的搬移工作以提升系统的并行处理能力。DSP对于当前帧图像处理完成后将等待处理使能标志的再次开启以继续下一帧图像的处理。DSP对于当前帧图像的处理结果将在当前帧处理完成后采用以太网传输至接收终端。

此外,DMA在执行图像数据搬移功能时,为了保证数据搬移过程与DSP图像处理的并行性,通常需要在DSP片内开辟2块图像数据缓冲区。由于5416DSP片内DARAM在速度上优于SARAM,因而通常重要的程序代码以及算法的堆栈都放在DARAM中,为了节省DARAM资源并充分利用SARAM,在DSP程序空间所在的SARAM和数据空间所在的DARAM中各开辟1块作为图像数据缓冲区。SARAM中的缓冲区用于DMA通道0从FIF0中读取当前帧图像数据,DMA通道1从SARAM缓冲区中读取上一帧图像数据,两个DMA通道的数据搬移功能都可以在DSP完成某个子算法的过程中并行实现。

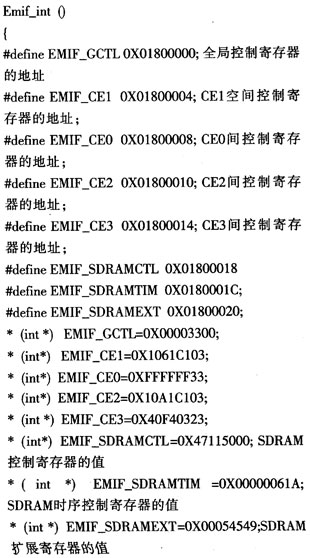

2.3 基于TCP/IP协议的以太网传输的实现与图像的实时传输

考虑到实际情况中通常采用图像处理系统与接收终端采用双绞线直连的方式传输图像数据,因而直接采取TCP/IP协议族中传输效率更高的用户数据包协议(UDP)完成系统与接收终端的数据交互。接收终端可采用套接字(Socket)获取UDP数据包,并从UDP数据包中还原出图像数据或其他系统参数。而在图像处理系统中,UDP数据包的发送主要通过DSP读写LAN9115的片内寄存器以及FIF0的方式实现,具体有以下几个步骤:

(1)初始化。完成LAN9115的唤醒工作,判别其工作状态,通过读写指定内部寄存器,激活他的各项功能。

(2)设置MAC地址。初始化时DSP通过更改LAN9115内部寄存器ADDRH和ADDRL的值,完成对网络MAC地址的设置。

(3)发送ARP数据包。根据UDP协议,发送数据时要获取对方机器的IP地址和MAC地址。该程序根据ARP协议,发送ARP数据,再接收图像接收端发回的RARP数据包,分析里面的数据,即可生成符合要求的UDP数据。

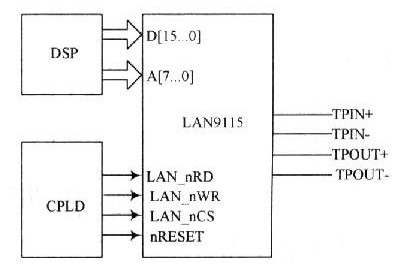

(4)发送图像数据。在发送数据包(Packet)过程中,DSP先更改LAN9115的寄存器TX_CMD_A和Tx_CMD_B的值,其中包含了要发送的数据大小,数据包(Packet)长度等信息,该系统目前采取的图像大小为320×240像素。在实际传输中,每帧图像分20块(1 Frame=20 Block),每块又分6个数据报传输(1 Block=6 Slice),每个数据包中图像数据为1 280 B(1 Slice=1 280 B)。这样做是因为以太网协议里规定每个数据包大小不能超过1 514 B,Windows系统中Socket套接字的缓冲区是8 KB。然后DSP利用I/0端口访问模式将数据依次写入LAN9115中。要中断当前传输过程,可设置寄存器TX—CFG中sTOP—Tx比特为1。这个传输过程就将立即结束。LAN9115与DSP的接口如图4所示。

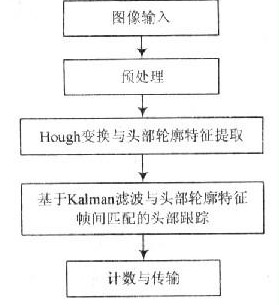

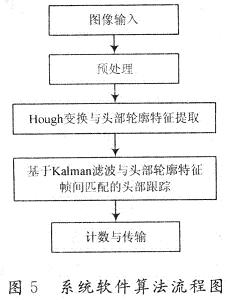

3 系统软件设计

针对客流检测的实际应用,提出的嵌入式客流检测系统依据人体头部在俯视图像中近似为圆形的特点采用基于Hough变换的头部轮廓特征提取和识别方法定位图像中的行人头部,并利用基于Kalman滤波和头部轮廓特征帧间匹配的跟踪方法实现人体头部的跟踪以防止重复计数情况的出现,系统的软件设计流程图如图5所示。

4 实验结果

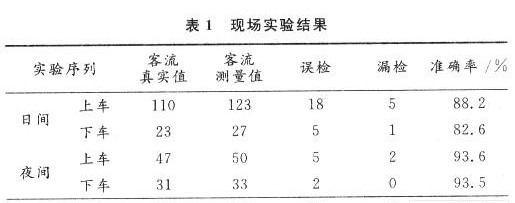

系统软件算法目前已完全移植入系统硬件平台并可以进行现场实验。在某公交公司的配合下,系统平台在一条实际运营的公交线路上进行了公交客流检测的现场实验。为了对系统应付客流高峰的能力进行*估,现场实验特意挑选了一条终点站为火车站,且包含大量客流高峰情况的公交线路。另外,考虑到公交客流检测全天候工作的特性,系统平台在夜间带有红外照明的情况下也进行了现场实验。实验结果可见表l。

5 结语

实践证明,该图像处理系统可以很好地进行图像采集、实时数据处理以及输出。在客流检测时,准确率较高。作为基于DSP嵌入式系统和以太网传输的网络测试平台,有远程传输和控制的能力,有广泛的应用范围和推广价值。该项目的完成,非常感谢浙江大学信息学院刘济林教授的大力支持和指导。

-

处理器

+关注

关注

68文章

20368浏览量

255533 -

dsp

+关注

关注

561文章

8287浏览量

368884 -

嵌入式

+关注

关注

5211文章

20737浏览量

338338

发布评论请先 登录

基于DSP的图像处理系统的应用研究

基于FPGA控制的多DSP并行处理系统

基于DSP和DSP/BIOS的实时雷达信号采集与处理系统

基于DSP的图象采集与处理系统的设计

基于DSP的嵌入式视觉客流检测系统

信号处理器(DSP),信号处理器(DSP)是什么意思

一种基于DSP+FPGA视频图像采集处理系统的设计与实现

如何使用FPGA和DSP实现CCD图像相关处理系统

基于OMAP5910双核处理器实现实时图像处理系统的应用设计

采用DSP处理器实现客流检测处理系统的设计

采用DSP处理器实现客流检测处理系统的设计

评论