“有些同学反馈,胡老师介绍的是很多PCB设计知识。是的,这些不仅仅是PCB设计师需要掌握的知识,也是硬件设计者必须要了解和掌握的经验知识。

硬件工程师设计作品的具体展现方式之一就是PCB。不论PCB板子具体由谁设计,是要交付到用户手中的实物。在这上面如果暴露有任何问题或缺陷,硬件设计者都是直接相关人,而且通常是第一责任人。”

一个硬件设计工程师,只有熟知这些基本经验知识和PCB设计规则,运用到设计过程中,才能够成为真正的硬件设计大咖。同时,真正的PCB设计大咖也要是硬件设计高手。

了解基本的设计经验知识,成为“设计达人”。

1、电气间隙和爬电距离–安全规范中的两个基本概念和规则

正规的电子产品需要满足各种不同的标准和规范要求,有些需要通过特别机构认证才允许销售。最常见的有EMC/EMI规范和安全规范。

没有标准要求、没有规范特性、没有质量保证的产品是比较容易做出来的,因为可能连基本设计都没有,就是模仿copy他人的产品。这样的产品说实话是没有客户的。

电子设备的安全距离包括电气间隙(空间距离)、爬电距离(沿面距离)和绝缘穿透距离。

电气间隙Cl(Clearance):

在两个导电零部件之间或导电零部件与设备防护界面之间测得的最短空间距离。即在保证电气性能稳定和安全的情况下,通过空气能实现绝缘的最短距离。这个电气间隙之间承受有较高电压,与老化现象无关。

爬电距离Cr(Creepage Distance):

沿绝缘表面测得的两个导电零部件之间或导电零部件与设备防护界面之间的最短路径。如果是圆形带电区,其半径即为爬电距离。电子设备总会处于有灰尘,甚至潮湿等工作环境中。这个爬电距离要求,有时候也被称作防污要求。

爬电距离:爬的意思,可以看做一个蚂蚁从一个带电体沿着绝缘体表面爬行到另一个带电体必须经过的最短路程。电气间隙可以看成是一个带翅膀的蚂蚁飞过去的最短距离。

电气间隙的大小决定了电气间隙能承受的过电压。当过电压值超过某一临界值后,此电压很快就引起电击穿。因此,确认电气间隙大小必须以设备可能会出现的最大的内部和外部过电压(脉冲耐受电压为依据)。

在不同场合使用同一电气设备或运用过电压保护器时所出现的过电压大小各不相同。需要查阅标准/规范来确定设计规则,以保证产品满足标准要求。

实际设计中要考虑最糟情况来决定确定设计规则。因为测试的时候会对内部零件施加10N力,外壳也施加30N力,以减少其距离,模拟最糟的情况,来验证空间距离是否符合标准规定。

设计时要同时考虑电气空间距离和表面距离,必须满足电气间隙和爬电距离这两者的要求。

一般来说,爬电距离要求数值比电气间隙的数值要大。爬电距离和绝缘形式(基本绝缘、辅助绝缘、加强绝缘、双重绝缘、或各绝缘组合)、电压的大小、污染等级、材料CTI特性以及表面形状有关。根据这些条件来查表确定出设计规则。通常可以采用开槽的方式(槽宽要大于1mm)来增加爬电距离。

左表是基本绝缘最小爬电距离,右表是功能绝缘的最小爬电距离,基于IEC60335-1:2001

PCB常见的FR-4材料漏电起痕指数CTI(Comparative Tracking Index)在175-225之间,属于Ⅲa类材料。消费类和通讯类产品通常工作电压小于50V,所以FR-4材料常常大量应用在这些产品场合。超过50V电压的电路部分,可用下面参考值来设计(详见GB4706.1-1998 第29节)。

工作电压大于250V至440V的电控部分与不带电的金属部件之间的电气间隙>3mm,爬电距离>4mm。

工作电压大于130V至250V的电控部分与不带电的金属部件之间的电气间隙>2.5mm,爬电距离>3mm。

工作电压小于或等于130V的电控部分与不带电的金属部件之间的电气间隙>1.5mm,爬电距离>2mm。

如不能够确定材料组别,要假定材料为Ⅲb组。

一般地,PCB设计中外层需要严格按照标准来设计。经验参考:弱电距离应大于15mil,强电应大于100mil;在内层15mil间距能满足1500Vac隔离;如果距离不够可以开槽来增加爬电距离(开槽要大于1mm)。

实际场合远比上面内容还要复杂,一定要分析具体的应用场合和电路要求。在具体设计时一定要去仔细分析,查阅相关标准规范,或询问专家,确保设计规则正确,避免后期多次返工,费时费力,还不一定找到问题症结。

2、PCB布线trace的长度Length、宽度Width和厚度Thickness

对印制电路板PCB而言,铜是大多数电路板的原料。PCB板的铜箔厚度1oz,意味着走线厚度为35um。

PCB上的走线要走多宽才合适呢?基于时下工艺制造条件,一般规则下低频小电流PCB走线宽度选用10mil;特殊密集区选择6mil线宽。有时会用4mil甚至更细的线宽来布线。

若要精细选择布线线宽,首先要考虑阻抗匹配设计。注意要考虑工艺补偿:图形补偿和表面处理补偿。因为导线横截面不是一个理想的矩形,实际上是一个梯形。以TOP层为例,当铜箔厚度为1oz时,梯形的上底边比下底边短1mil。比如线宽5mil,制造工艺上会引入系统误差,其上底边W2约4mil,下底边W1为5mil。上下底边的差异和铜厚有关。下表是不同情况下截面梯形上下底W2/W1之间的关系。

另外,经过表面处理,如绿油涂敷后,设计的阻抗值会变小。

还要考虑到PCB线的过流能力。PCB线通过电流的能力与线宽和铜箔厚度、布线在内层和外层以及容忍的温升等参数紧密有关。参考美军标MIL-STD-275,线宽10mil走线在允许温升10摄氏度的条件下,可通过0.5A电流(1/2oz铜厚)。

如果作高电压或大电流的强电设计,还需要考虑一定的降额如30%-50%来应用。

PCB上的走线trace要走多长?(1 inch=1000mil=25.4mm)

首先了解一个概念“曼哈顿距离”。曼哈顿距离(Manhattan Distance)是标准坐标系上两个点的绝对轴距总和。如图红线代表曼哈顿距离Manhattan Distance=

PCB板上两点之间走线trace的最短长度是欧式距离

一般来说,PCB布线的长度参考曼哈顿距离。通常实际Route走线长度在最短距离到1.1倍曼哈顿距离之间。如果Route的长度超过1.3倍曼哈顿距离,表明在板上有很多设计冗余过长的环路。有可能需要优化布局,重新布线。

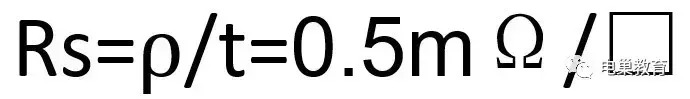

走线trace过长会影响什么呢? 计算一下走线电阻:走线厚度0.5oz,线宽6mil,线长6inch。铜的体电阻率

所以,6000inch走线直流电阻=

很长trace的走线电阻通常可以忽略(如24in的走线电阻仅为2欧姆)。但是需要占据更多的PCB空间来布线。

PCB走线过长导致最为关键的影响是信号传播时延变长,信号对器件的驱动能力(带负载能力)有要求,信号可能会发生畸变。这个内容后面再详细讨论。

-

pcb

+关注

关注

4319文章

23111浏览量

398347 -

电气

+关注

关注

18文章

1167浏览量

53158

原文标题:老胡谈设计——硬件设计常用经验知识(二)

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

了解基本的设计经验知识,成为“设计达人”

了解基本的设计经验知识,成为“设计达人”

评论