小伙伴们了解了 ESD的基本概念以及系统高效ESD设计(SEED)的必要性(告警!您的RF设备需要系统级ESD保护),这次Qorvo将为您介绍SEED工具箱中所有必要的部分,Let's go!

板载ESD保护器件

作为一个总体战略,您可以在PC电路板上使用许多保护元件,以保护终端产品免受ESD事件的影响。这些保护元件包括:

无源和有源元件,如:

串联电阻

去耦电容

铁氧体磁珠

抑制装置,如电磁干扰(EMI)/ESD滤波器

瞬态电压抑制器(TVS)

TVS元件:

聚合物变阻器

陶瓷变阻器

火花隙s

硅二极管

然而,使用这些元件时应谨记以下几点:

电阻、电容、电感-电容(LC)滤波器和铁氧体磁珠在系统中衰减间接或二级ESD应力方面表现良好。一个有效的方法就是,需要将这些元件尽可能置于ESD应力对象(模块引脚)附近。

您可以将串联电阻与去耦电容(电阻-电容[RC]滤波器)或电压箝位一起使用。

电容提供去耦性。选择的电容最好具有高额定电压、高共振频率、低电阻和低电感。确保在连接电容时实现轨迹长度的最短化。

LC滤波器可阻隔瞬变电压和EMI。

串联铁氧体磁珠可衰减电源线上的EMI和ESD。

变阻器可从高待机值变为极低导电值,从而吸收ESD能量,并限制ESD诱发性电压。它们通常具有较高的触发电压(几百伏)和高达100 V的箝位电压,同时具有非常低的电容,但能够在长时间的ESD应力之后显示明显的漏电流。

根据待保护的接口类型,硅基TVS二极管也可以具有较低的电容和比其他TVS元件更低的动态电阻值。它们具有较高的ESD吸附能力(即一旦ESD触电被吸附,保护装置就会非常快速地返回到高阻抗状态)。适合高速/RF应用的TVS二极管可提供非常低的触发电压(低于100 V)和箝位电压(低于20 V),同时具有出色的响应时间。

但请注意:片外保护器件的电容将导致RF通道中的不匹配性。为弥补这些不匹配性,设计人员需要调整其RF和天线路径中的匹配网络。

更多关于瞬态电压抑制器(TVS)的信息

TVS二极管是实现ESD保护的首选元件之一。当诱发性电压超过雪崩击穿电压时,它们通过分流过电流的方式运行。它们是一种箝位装置,抑制所有高于击穿电压的过电压。当不存在过电压时,它们会自动重置至关闭状态,但会吸收更多内部的瞬态能量。

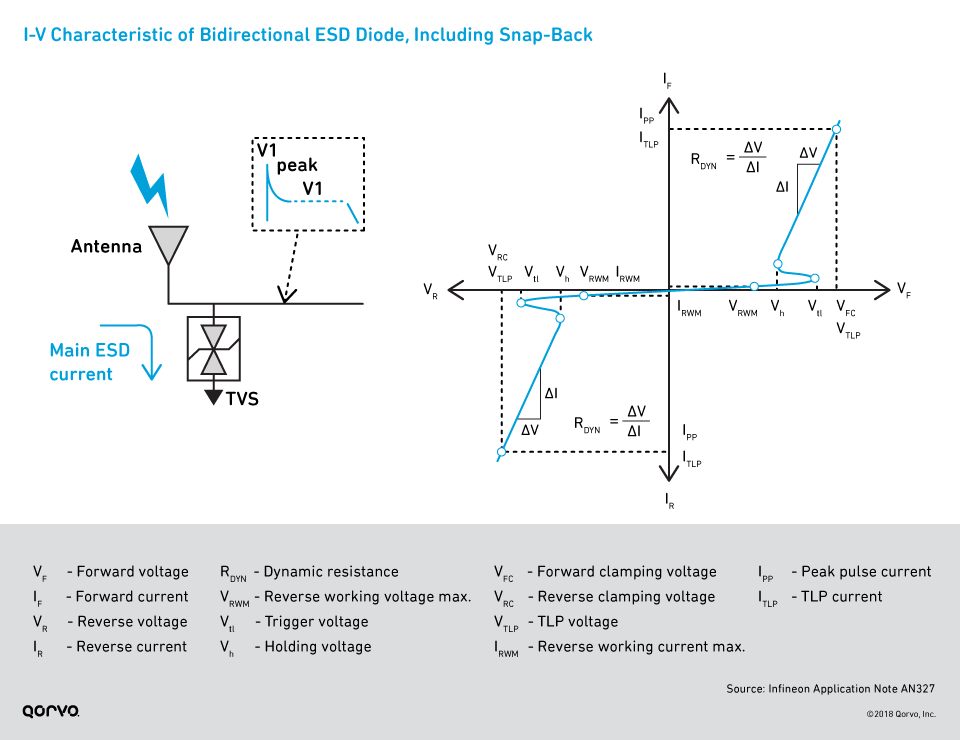

TVS二极管可以是单向二极管,也可以是双向二极管。双向二极管可使用两个相互对立的雪崩二极管以串联的方式表示,如下所示,并连接至相对于被保护引脚的并联配置。这些设备均制造为单个封装元件。

对于RF应用中的ESD保护,必须保持尽可能小的TVS二极管电容。这可避免输入匹配的失谐,从而使保护设备产生较少的谐波失真。

下图显示了双向TVS二极管的电流-电压(I-V)曲线。您可以看到,TVS相对于原点呈对称状,且可针对正极和负极ESD触电进行ESD保护。

下图比较了变阻器、聚合物和TVS二极管响应ESD触电的残留电压。大家可以看到,当今的硅基TVS二极管是针对ESD触电最有效的方法。

板载TVS二极管位置的重要性

然而,TVS的位置具有重要影响。如果电路设计不当,则ESD保护就不会那么有效。请记住,这些一般原则:

在开发PC电路板时,请注意轨迹不要太长,因为这会产生不必要的电感。

记住:与TVS设备串联的电容会使一级ESD电流路径断开,而添加至一级ESD电流路径的任何RF电感都会提高残留路径中的总阻抗。

如果将TVS置于合适的位置,就不需要其他ESD元件。

那么什么是合适的位置?如下图所示,您应该:

只使用TVS。

切勿将TVS置于电容或电感器的前面或后面。

确保没有轨迹。应将TVS置于RF路径和接地之间。

接地:机械因素

为缓解ESD事件,必须对成品的每一方面进行正确的接地——PC电路板、所有IC芯片和元件、外壳、盖子等。确保在终端产品接地时考虑了以下所有方面:

所有金属件必须通过低阻抗路径连接至系统接地。

浮动金属部件都有ESD危险。

所有金属部件都必须接地,或如果适用,更换为塑料件。

多个互联的PC电路板设计可能会导致高电阻电感系统接地。当一级TVS和RF模块置于不同的PC电路板上时,应特别注意保护天线。

一级和二级ESD保护

了解一级和二级ESD保护是SEED方法的基本组成部分。通常:

一级保护是在板上进行,称为主要箝位。

二级保护是在片上进行,称为辅助箝位。

一级和二级ESD保护阶段的协同设计是SEED方法的基本概念。下图显示了RF前端(RFFE)中针对ESD保护的主要和辅助箝位的高级基本视图。

注意:一些系统设计需要在IC前放置一个额外的板载辅助箝位,以减少元件引脚可能存在的任何残留ESD电荷。

我们来进一步了解一级和二级保护:

一级保护(板载):一级保护可能包含箝位元件,如并联电感器或TVS元件(二极管、变阻器和火花隙)。这些主要箝位可分流较大的ESD电流。主要箝位主要为与直接ESD能量入口接触的外部连接和其他接口。此外,它们在减少IC元件引脚处出现的残留ESD应力方面发挥着重要作用。

二级保护(片上):二级保护用于箝住设备引脚处积累的任何残留ESD应力。ESD瞬态的形状在很大程度上取决于板载主要箝位特性和PC电路板设计。

一级和二级ESD保护阶段的协同设计(即板载和片上保护)是SEED方法的基本概念。这两个阶段可在两个分支的载流能力通过串联阻抗实现平衡的位置提供必要的保护。

模拟和分析这两个保护阶段可帮助电路板设计人员选择适当的板载保护箝位电平,以确保能够有效地处理抵达IC的峰值残留脉冲。利用模拟实现的SEED保护设计要求将国际电工委员会(IEC)应力模型、基于SEED参数的TVS和IC接口引脚模型以及隔离阻抗电路(即PC电路板上的电路)整合在一起。我们将在第3部分详细介绍如何模拟和分析SEED设计。

RF前端(RFFE)的保护战略

不同的应用需要不同的ESD保护。一种方法或许能够满足您的应用需求,但可能不适用于其他应用。最终,您使用的设计必须通过FCC和IEC测试,这样您的产品才能获得认证并出售。我们来看看可用于RFFE中ESD保护的几种战略。

1基本保护——并联电感器

最基本的方法是采用一个并联电感器。如下图所示,电感器(L)是ESD电流脉冲的主要分流元件。该电感器的nH范围应比较低(<20 nH),这样才能构成有效的 ESD 保护解决方案。但它会增加插入损耗,带来一些 RF 性能挑战。并联电容通常用于实现 RF 匹配,而非 ESD 保护。

2单级高通滤波器

第二种方法采用单级高通滤波器(HPF),如下图所示。然而,这可能并不是最有效的方法。

优点:

提供良好的全带宽ESD覆盖。

可合理地减少ESD脉冲幅度,同时允许蜂窝频率范围通过。

缺点:

会产生较高的残留电压(Vpeak>100 V)。

需要较低的电感,以确保最优性能(这意味着实现RF与ESD性能权衡)。

3两级ESD保护

第三种方法使用两级ESD保护,如下图所示。该方法将TVS作为一级保护,并将HPF作为二级ESD保护,以捕获残留应力。

如下图中看到的那样:

第一级保护(TVS)箝住低于20V的电压,从而将峰值电压降至50V以下。

第二级保护中的HPF进一步降低残留电压脉冲,箝住低于10V的电压,从而将峰值电压降至20V以下。

ESD保护的最佳方法

最终,您是在试图降低IC在ESD触电中遇到的电压;目的是在其击中IC之前降低所有峰值电压。我们认为理想的ESD战略就是两级方法,第一级使用TVS元件(TVS二极管),第二级使用HPF网络。

优势:

它可以提高您的电路板级ESD保护,并为您提供通过IEC测试的最佳机会。

此外,它还可以减少ESD脉冲幅度和RF路径上的残留电压。

双向TVS二极管有助于防止正极和负极脉冲影响。

高通滤波器可箝住任何残留电压脉冲。

从而为元件引脚提供最佳保护。

-

ESD

+关注

关注

49文章

2103浏览量

173542 -

移动设备

+关注

关注

0文章

507浏览量

54856 -

SEED

+关注

关注

0文章

11浏览量

9202

原文标题:移动设备的 ESD 设计战略:您的 SEED 工具是否拥有这些部分?

文章出处:【微信号:Qorvo_Inc,微信公众号:Qorvo半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

matlab的其他工具箱及SIMULINK

如何在matlab中添加新的工具箱

MATLAB语言工具箱-ToolBox实用指南

***工具箱下载5.8最新版

调试工具箱中所包含的工具介绍

matlab的其他工具箱及SIMULINK

怎样改善塑料工具箱的铰链

普查工具箱有哪些以及植保仪器工具箱系列的汇总

MATLAB自动驾驶工具箱使用

您的SEED工具箱中所有必要的部分有哪些?

您的SEED工具箱中所有必要的部分有哪些?

评论