由于获取图像的工具或手段的影响,使获取图像无法完全体现原始图像的全部信息。因此,对图像进行预处理就显得非常重要。预处理的目的是改善图像数据,抑制不需要的变形或者增强某些对于后续处理来说比较重要的图像特征。

通常根据预处理目的的不同,把预处理技术归为图像增强技术和图像分割技术两类。图像对比度处理是空间域图像增强的一种方法。由于图像灰度范围狭窄会使图像的对比度不理想,可用对比度增强技术来调整图像灰度值的动态范围。

图像处理通常采用软件或者DSP(数字信号处理器)来实现。如果利用软件实现,运行时会耗费较多的PC资源,而且算法越复杂时耗费的资源就越多,对于需要高速处理的情况就不适用了;而如果采用DSP来实现,提高并行性的同时指令执行速度必然会提高,较高的指令速度可能导致系统设计复杂化,并增加功耗和成本。新一代的FPGA集成了CPU或DSP内核,可以在一片FPGA上进行软硬件协同设计,为实现SOPC提供了强大的硬件支持。本文介绍的是利用FPGA并行处理和计算能力,以Altera FPGA Stratix EP1S40为系统控制的核心实现的SOPC。

系统硬件平台

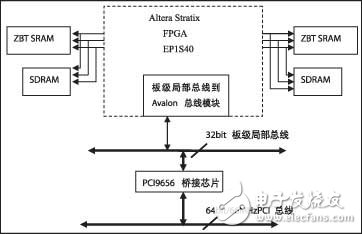

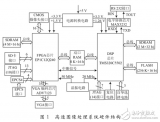

采用基于PCI总线的FPGA开发平台,结构如图1所示。板上主要硬件资源有:PCI桥、FPGA、SRAM和SDRAM等其他外设。

PCI桥采用PCI9656桥接芯片实现,用来连接PCI总线与32位/50MHz的板级局部总线;FPGA包括41 250个逻辑单元,14个DSP模块,112个嵌入式乘法器,4个增强型PLL(锁相环)和4个快速型PLL等逻辑资源;SDRAM用来存储图像数据。Avalon总线模块完成整个片上可编程系统组件之间的互连。Avalon总线是SOPC设计中连接片上处理器和其他IP模块的一种简单总线协议,规定了主、从构件之间的端口连接以及通信时序关系,SOPC Builder来完成整个系统(包括Avalon)模块的生成和集成。丰富的板级资源可以满足图像的高速预处理需求。

系统工作原理

设计采用DMA方式快速传输图像数据,这样数据的传输和处理可以并行起来,使得系统的运行效率大为提高。PC与PCI板卡之间建立软件环境,在该环境下利用DMA通道把图像数据从主机通过PCI总线、PCI桥、板级局部总线和Avalon总线传到SDRAM存储起来,然后送入算法逻辑模块进行处理,处理完成后再把图像数据存储到SDRAM中,最后再用DMA通道把图像处理结果传送回主机。

图1 基于PCI总线的FPGA开发平台

建立片上系统中的关键模块

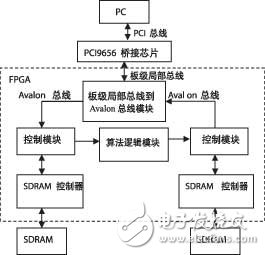

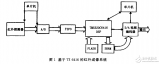

本文设计的图像对比度增强系统是建立在Stratix EP1S40基础上的SOPC。该设计在Quartus II 5.0中利用SOPC Builder将系统的工作频率设为50MHz,器件系列设为Stratix,调用已经建立的IP模块和算法逻辑模块,并设置各个模块的时钟和基地址,配置生成片上系统。根据任务要求,SOPC结构框图如图2所示。

图2 SOPC结构框图

图2中,Avalon总线接口分为主(Master)和从(Slave)两类,前者具有相接的Avalon总线的控制权,后者是被动的。自定制的Avalon从外设根据对Avalon总线操作方式的不同分为两类:一类是Avalon从(Slave)外设,只是作为Avalon总线的一个从元件来处理;另一类是Avalon流模式从(Streaming Slave)外设,需要使用Avalon总线的流传输模式,外设的设计更复杂。

● 板级局部总线与Avalon总线桥之间的通信模块

在板级局部总线与FPGA内部Avalon总线桥之间建立通信模块。由于SOPC内部各模块之间的逻辑连接是由Avalon总线完成的,所以可以从主机通过PCI总线和板级局部总线访问SOPC组件。该模块作为Avalon总线的一个主控接口,对其他Avalon从外设和Avalon流模式从外设进行访问和控制。

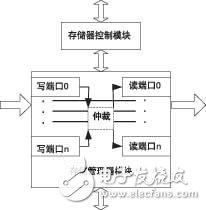

● 控制模块

控制模块的工作时钟独立于系统时钟,如图3所示。包括两个模块的设计:(1)用于对SDRAM存储资源做合理分配的流模式存储管理器模块,它作为Avalon流模式从外设,读写端口的数量可配置,这些读写端口可以以流传输模式把图像数据读出或写入SDRAM。(2)存储器控制模块,它作为Avalon总线的另一主控接口,对作为Avalon总线从控接口的SDRAM控制器进行控制。

图3 控制模块

● 图像对比度增强算法及VHDL实现

在图像对比度处理方法中,可以设计出不同的转换函数。本系统是针对锯齿形函数转换设计的,锯齿形转换可以把几段较窄灰度区间拉伸到较宽的灰度范围内,这种处理可以把灰度变化较平缓的区域也较鲜明地显示出来,从而增强图像中感兴趣的特征。

该设计对一帧3008×2000像素、数据宽度为8位的灰度图像进行处理,图像共有2000行、3008列像素点,行和列均从0开始计起。在系统时钟上升沿、行有效信号与数据有效信号均有效时,把图像数据读入进来,对其做相应处理。每个系统时钟上升沿读入一个图像数据,在第N行像素点处理完后,第N+1行有效信号与数据有效信号必须同时有效才能继续处理,在对第1999行、3007列像素点处理完毕后,行有效信号与数据有效信号置为无效,此时整帧图像处理完毕。算法逻辑模块中需要帧有效计数器和行有效计数器各一个,分别用来对帧和行进行计数,还需要一个像素计数器对某行像素做计数统计。由于该算法逻辑模块是基于SOPC技术,能够在SOPC Builder工具中作为自定制模块调用,需设置两个寄存器,分别是帧有效计数寄存器和行有效计数寄存器,它们根据Avalon总线地址的不同,同时作为Avalon总线的读或写寄存器,从而使自定义模块可以和Avalon总线进行通信。每输入一个像素点判断其灰度值满足设置的哪个区间范围并做相应转换,从而实现一帧图像的对比度增强处理。根据算法需求,采用VHDL语言对算法逻辑建模,并以Avalon总线从外设的方式在SOPC Builder 中调用。VHDL实现如下。

entity enhancement is

port (iLVAL : in std_logic;

iDVAL : in std_logic;

iFVAL : in std_logic := ‘1’;

iCLK : in std_logic;

iDATA : in std_logic_vector(7 downto 0);

oLVAL : out std_logic; oDVAL : out std_logic;

oFVAL : out std_logic;

oDATA : out std_logic_vector (7 downto 0)

);

end enhancement;

这里iFVAL被置为“1”,说明是对一帧图像进行处理;iDATA与oDATA是图像输入、输出二进制数据,宽度为8位。

图像预处理系统的实现

用标准化硬件描述语言VHDL建立FPGA模块实现。按照自顶向下的设计方法生成各设计阶层,将设计任务分解为不同的功能元件,每个元件具有专门定义的输入输出端口并执行各自的逻辑功能。该SOPC设计通过以下步骤实现。

(1)利用SOPC Builder工具编译生成用户自定制模块,调用已建立的IP模块并设置参数,配置生成片上系统;

(2)在顶层VHDL文件中调用模块并示例化,进行信号连接;

(3)对整个系统进行管脚等约束设置,全编译并进行行为和时序验证;

(4)下载和硬件调试完成。

结束语

该系统对实验室在光线较弱情况下所拍的一帧3008×2000灰度图像进行对比度增强处理,处理前后如图4、5所示。在SOPC系统时钟为50MHz时,对于输入大小为3008×2000像素点的灰度图像,每一帧的处理时间为T=(1/(50×106))×3008×2000=0.120 32s。

图4 原图像

图5 处理后图像

而在3GHz Pentium 4、256MB内存的PC上通过Matlab用代码实现则需0.9850s。该设计采用FPGA实现图像预处理系统,与利用软件处理图像的方法比较起来,可以更快速地实现对图像的预处理。同时系统构成灵活,设计中模块的可重复开发性降低了生产成本、缩短了生产周期,提高了工作效率。

-

dsp

+关注

关注

554文章

8060浏览量

350861 -

FPGA

+关注

关注

1631文章

21806浏览量

606694 -

总线

+关注

关注

10文章

2908浏览量

88489

发布评论请先 登录

相关推荐

基于FPGA+DSP的三维图像信息处理系统设计

基于FPGA的高速图像预处理系统设计

一种基于DSP+FPGA视频图像采集处理系统的设计与实现

如何使用FPGA进行图像实时处理系统的设计

利用FPGA并行处理和计算能力实现图像预处理系统的设计

利用FPGA并行处理和计算能力实现图像预处理系统的设计

评论