1 DCI技术概述

随着FPGA芯片越大而且系统时钟越高,PCB板设计以及结构设计变得越难,随着速率的提高,板间的信号完整性变的非常关键,PCB板上若有关键信号,那么需要进行阻抗匹配,从而避免信号的反射和震荡。Xilinx公司提供DCI可以在芯片内部进行阻抗匹配,匹配电阻更加接进芯片,可以减少元器件,节省PDB板面积,并且也更方便走线。

传统的阻抗匹配是在PCB板上端接一个电阻。理想情况下,源端输出阻抗认为是很小的,而接受端的输入阻抗认为是很大,在实际电路中都可以不去考虑,只考虑PCB上的走线,从接收端看过去PCB特征阻抗应该等于端接电阻,这样电流从源端流向接收端才不会导致反射。

1.1 阻抗匹配原理

阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共扼关系,即电阻成份相等,电抗成份只数值相等而符号相反。这种匹配条件称为共扼匹配。

在高速的设计中,阻抗的匹配与否关系到信号的质量优劣。阻抗匹配的技术可以说是丰富多样,但是在具体的系统中怎样才能比较合理的应用,需要衡量多个方面的因素。例如我们在系统中设计中,很多采用的都是源段的串连匹配。对于什么情况下需要匹配,采用什么方式的匹配,为什么采用这种方式。例如:差分的匹配多数采用并联终端匹配;时钟采用串联源端匹配。

1.2 串联源端匹配

串联源端匹配的理论出发点是在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

1.2.2 串联终端匹配后的信号传输具有以下特点:

1、由于串联匹配电阻的作用,驱动信号传播时以其幅度的50%向负载端传播。

2、信号在负载端的反射系数接近+1,因此反射信号的幅度接近原始信号幅度的50%.

3、反射信号与源端传播的信号叠加,使负载端接受到的信号与原始信号的幅度近似相同。

4、负载端反射信号向源端传播,到达源端后被匹配电阻吸收。

5、反射信号到达源端后,源端驱动电流降为0,直到下一次信号传输。

相对串联匹配来说,不要求信号驱动器具有很大的电流驱动能力。选择串联源端匹配电阻值的原则很简单,就是要求匹配电阻值与驱动器的输出阻抗之和与传输线的特征阻抗相等。理想的信号驱动器的输出阻抗为零,实际的驱动器总是有比较小的输出阻抗,而且在信号的电平发生变化时,输出阻抗可能不同。比如电源电压为+4.5V的CMOS驱动器,在低电平时典型的输出阻抗为37Ω,在高电平时典型的输出阻抗为45Ω[4];TTL驱动器和CMOS驱动一样,其输出阻抗会随信号的电平大小变化而变化。因此,对TTL或CMOS电路来说,不可能有十分正确的匹配电阻,只能折中考虑。链状拓扑结构的信号网路不适合使用串联终端匹配,所有的负载必须接到传输线的末端。可以看出,有一段时间负载端信号幅度为原始信号幅度的一半。显然这时候信号处在不定逻辑状态,信号的噪声容限很低。

串联匹配是最常用的终端匹配方法。它的优点是功耗小,不会给驱动器带来额外的直流负载,也不会在信号和地之间引入额外的阻抗;而且只需要一个电阻元件。

1.3 并联终端匹配

并联终端匹配的理论出发点是在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。实现形式分为单电阻和双电阻两种形式。

1.3.3 并联终端匹配后的信号传输具有以下特点:

1、 驱动信号近似以满幅度沿传输线传播;

2、 所有的反射都被匹配电阻吸收;

3、 负载端接受到的信号幅度与源端发送的信号幅度近似相同。

在实际的电路系统中,芯片的输入阻抗很高,因此对单电阻形式来说,负载端的并联电阻值必须与传输线的特征阻抗相近或相等。假定传输线的特征阻抗为50Ω,则 R值为50Ω。如果信号的高电平为5V,则信号的静态电流将达到100mA.由于典型的TTL或CMOS电路的驱动能力很小,这种单电阻的并联匹配方式很少出现在这些电路中。

双电阻形式的并联匹配,也被称作戴维南终端匹配,要求的电流驱动能力比单电阻形式小。这是因为两电阻的并联值与传输线的特征阻抗相匹配,每个电阻都比传输线的特征阻抗大。考虑到芯片的驱动能力,两个电阻值的选择必须遵循三个原则:

⑴两电阻的并联值与传输线的特征阻抗相等;

⑵与电源连接的电阻值不能太小,以免信号为低电平时驱动电流过大;

⑶与地连接的电阻值不能太小,以免信号为高电平时驱动电流过大。

传统的终端匹配要求电阻尽量靠近芯片管脚,不但增加了PCB的布线的难度,而且还增加了元器件的数量。

2 DCI技术的应用分析

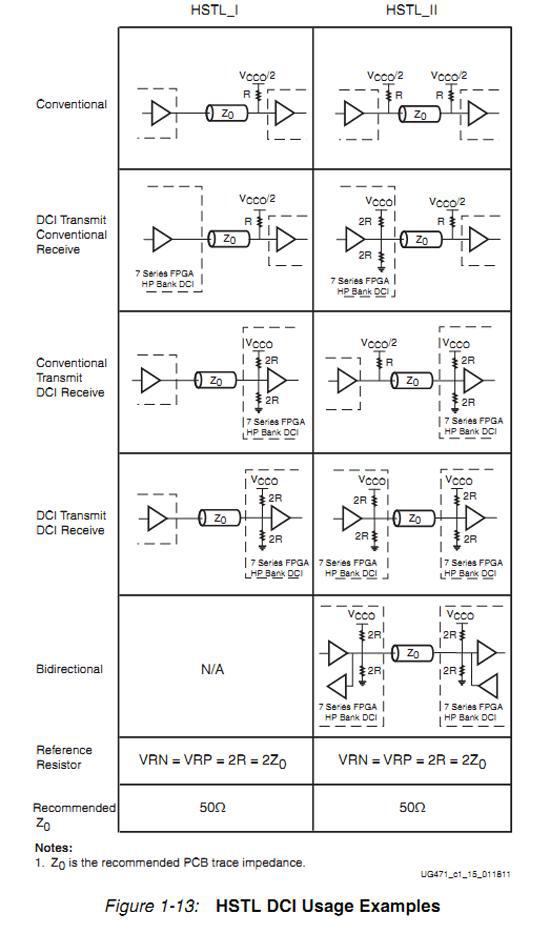

根据I/O的电平标准,DCI技术可以控制驱动器的输出阻抗,也可以在驱动器或者接收器上添加并行终端。目的都是精确的匹配传输线上的特征阻抗。DCI技术根据VRP和VRN上的高精度参考电阻计算I/O内部的阻抗。并且可以持续补偿因为温度和电压变化引起的阻抗变化。

对于阻抗控制驱动器,DCI使阻抗匹配外部的两个参考电阻,或者匹配这两个参考电阻的一半。

对于并行终端,包括发送器和接收器,DCI技术让终端电阻更加接近输出驱动器或者输入buffer. 对于7系列FPGA,DCI技术只用在HP I/O bank,对HR I/O bank 并不适用。Xilinx DCI使用两个复用管脚来调整驱动器的阻抗或者并联终端电阻。这两个管脚分别是VRN 和VRP.VRN必须通过一个参考电阻Rref上拉到VCCO,而VRP则必须通过一个参考电阻Rref下拉到地。这个Rref的阻值一般等于PCB走线的特征阻抗或者是这个阻抗的2倍。

2.1 要在设计中使用DCI技术,需要满足以下条件:

(1)该信号管脚是在HP I/O BANK,并且在约束中声明该管脚的标准是带有DCI的。

(2)在VRN上接一个高精度的参考电阻上拉到Vcco.

(3)在VRP上接一个高精度的参考电阻下拉到地。

(4)VRN和VRP都在同一个HP BANK,除非使用了DCI叠代,DCI迭代只需要HP master BANK的。

DCI计算可以通过DCIRESET原语进行复位。通过发送RST高脉冲给DCIRESET,DCI开始计算阻抗值并且此时所有使用了DCI的I/O都不工作,直到LOCKED信号拉高为止。

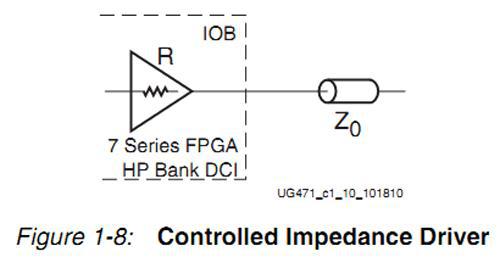

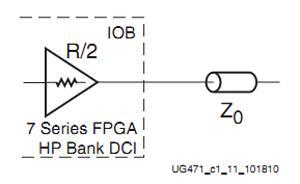

2.2 阻抗控制驱动器

对于阻抗控制驱动器,DCI提供两种阻抗匹配类型:

1、和参考电阻相等

2、等于参考电阻的一半

这种的话,R必须等于2Z0,电平标准要选择DCI_DV2,如LVDCI_DV2_15、LVDCI_DV2_18的原语,使用这种方式主要是为了降低静态功耗。

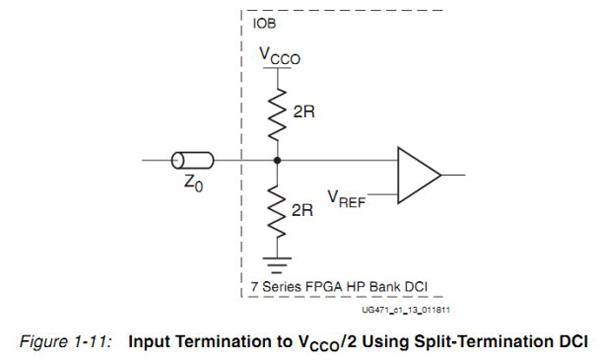

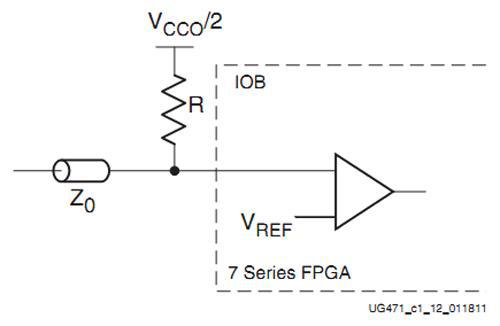

2.3 并联终端(分立电阻)

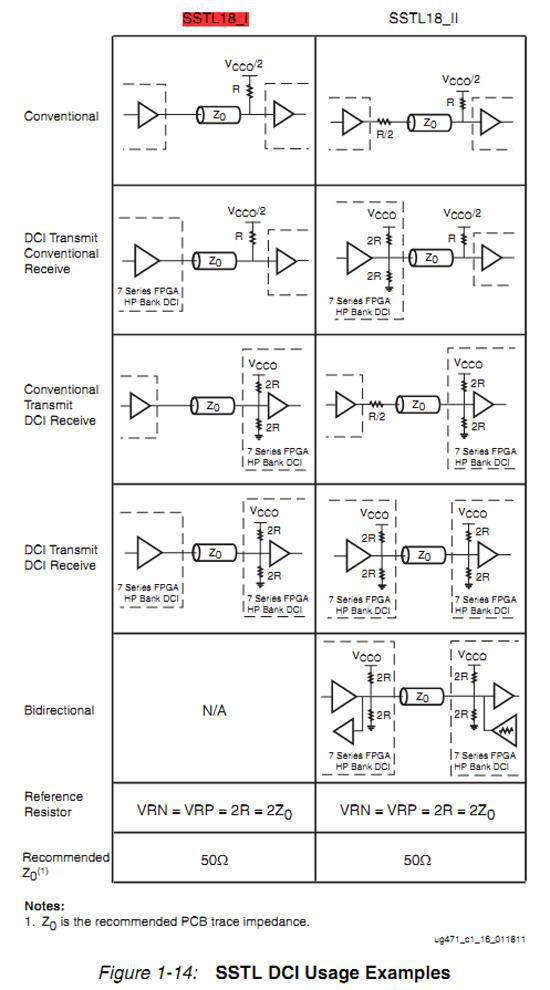

对于并联终端,DCI使用一种戴维南等效电路或者分立电阻,使用Vcco/2的电平。

其戴维南等效电路是如下图:

适合于分立电阻的DCI电平标准如下表:

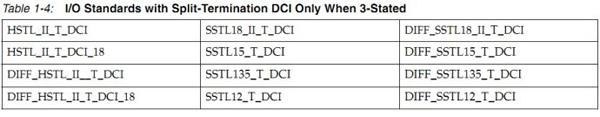

3 三态DCI分析

对于有些电平标准,如SSTL和HSTL的一级标准仅仅支持单向信号,而二级标准既支持单向也支持双向信号,当分立终端在使用时,DCI只控制分立终端的阻抗而不是驱动器的阻抗,所以对于双向信号来说,当它作为驱动器时,需要关闭分立终端的应用。XILINX提供了一个DCI-T的标准来满足这一要求,只需要将相应的电平标准改成这种带有DCI-T的就行。三态DCI只适合于双向信号。适用三态DCI的电平标准如下表:

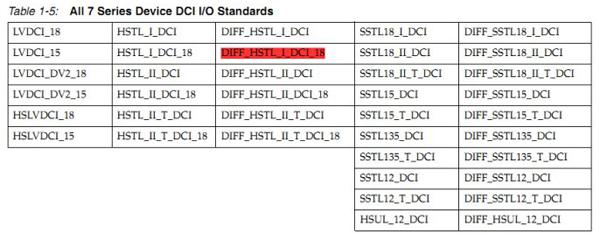

DCI所有的电平标准如下表。

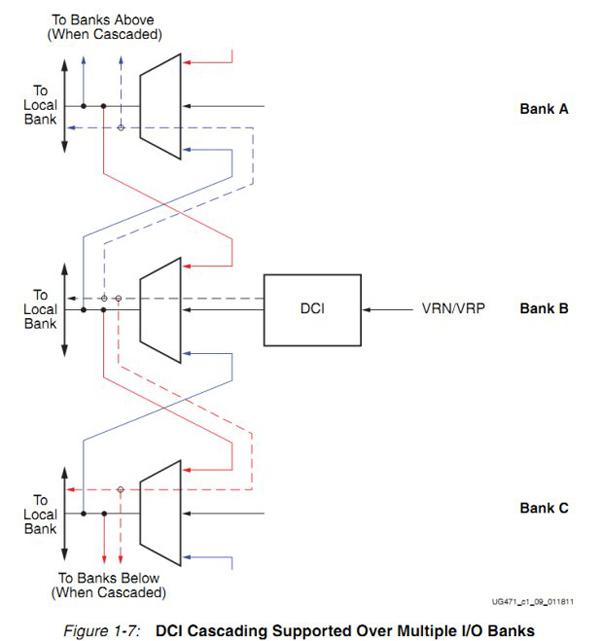

3.1 DCI迭代

7系列FPGA可以使用DCI迭代,DCI迭代就是同在一列的 I/O BANK可以共享一对参考电阻,即只要这一列的I/O BANK中的master BANK的RFN和RFP接了相应的电阻后,其他的slave BANK的RFN和RFP都不需要再接参考电阻了。这样大大减少了元器件数量同时也减少了功耗。

3.1.1DCI迭代需要遵循如下规则:

(1)需要DCI迭代的管脚必须在同一列BANK上。

(2)同一列BANK需要分成MASTER和SLAVE BANK,他们应该有共同的Vcco和Vref.

(3)在同一列BANK上,但是没有使用DCI技术的BANK可以不遵循第二条规则。

(4)为了实现这个DCI迭代,需要使用DCI_CASCADE Constraint.

3.1.2 约束语法规则:

CONFIG DCI_CASCADE = “ …”;

例如:

CONFIG DCI_CASCADE = “11 13 15 17”;

总之,对于7系列FPGA要正确使用DCI技术的话,要做如下:

第一、Vcco必须是基于合适的电平标准。

第二、使用正确的DCI I/O BUFFER通过电平标准属性或者在HDL中例化的代码中。

第三、DCI技术要求相应的BANK中VRN和VRP管脚用来连接正确的参考电阻,对于DCI迭代技术则只要master bank中的VRN和VRP管脚用来连接正确的参考电阻。有一种情况就是当DCI(带阻抗控制驱动器)只作为输入时,并且这些管脚又是仅有的使用了DCI电平的管脚,那么该BANK不需要将VRN和VRP接参考电阻。这些电平标准有以下这些。

3.1.3 遵守DCI I/O BANKING规则

(1)同一BANK的输入管脚或者使用了DCI迭代的同一组的BANK的输入管脚 ,其参考电压Vref必须是一致的。

(2)在同一个BANK中Vcco必须兼容所有的输入或输出管脚。

(3)分立终端、阻抗控制驱动器、以及半阻抗控制驱动器,可以在同一BANK中同时存在。

4 DCI使用案例

4.1 注意

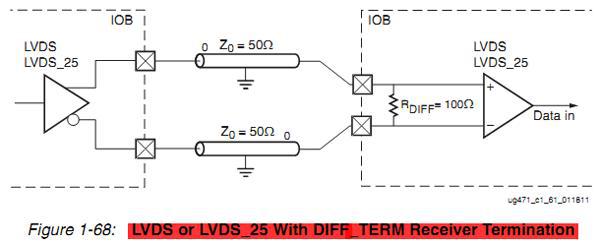

LVDS和LVDS25是不能使用DCI技术来进行终端匹配的,它只能通过内部终端电阻来进行匹配如下图所示。

-

FPGA

+关注

关注

1630文章

21763浏览量

604556 -

芯片

+关注

关注

456文章

50984浏览量

425166 -

pcb

+关注

关注

4323文章

23129浏览量

398779

发布评论请先 登录

相关推荐

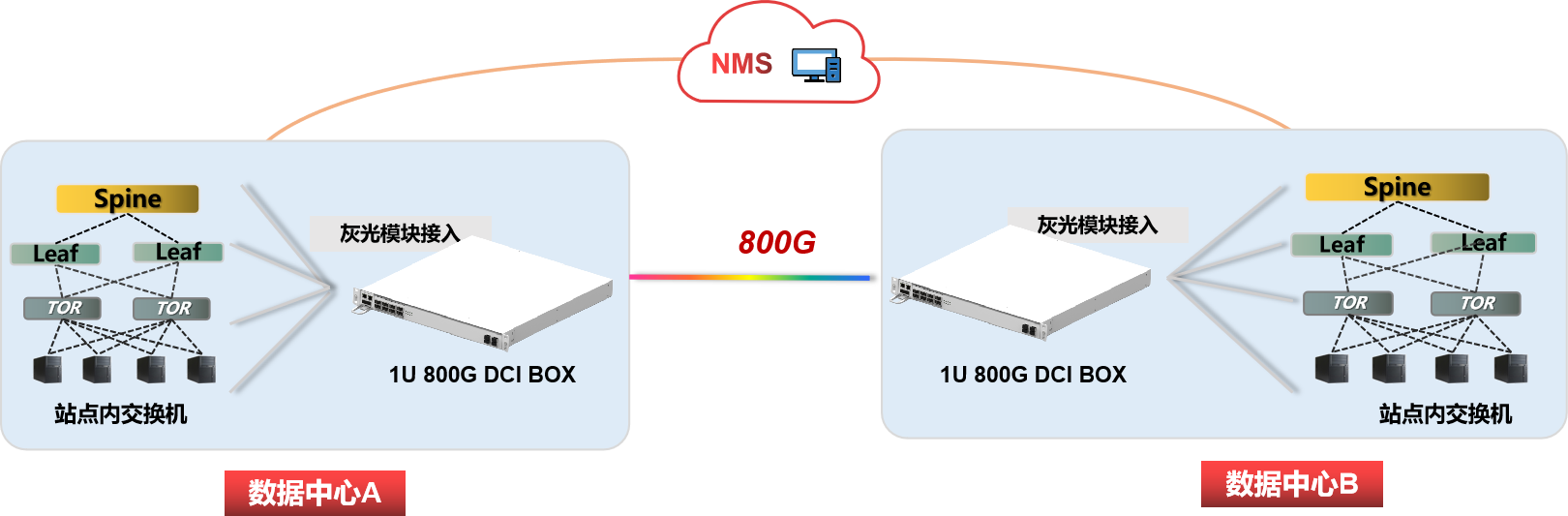

DCI 颠覆光器件产业?

Xilinx FPGA DCI使用方法

Vivado的DCI与内部参考电压设置步骤

为什么银行也没有DCI匹配?

可以使用具有3.3V LVTTL输入的DCI吗?

如何在IBIS文件中配置SSTL135 DCI阻抗

最全面的7系列FPGA的DCI技术分析

DCI是什么?Xilinx 7系列FPGA的HP bank都支持DCI

DCI BOX与传统WDM/OTN设备有什么区别?

易飞扬非相干DCI BOX的DCI传输方案介绍

非相干DCI BOX,提供更经济的DCI传输方案

非相干DCI BOX,提供更经济的DCI传输方案

DCI技术应用分析及DCI迭代需要遵循的规则介绍

DCI技术应用分析及DCI迭代需要遵循的规则介绍

评论