引言

近年来,我国广播电视数字化发展的进程明显加快,从而直接引发了对机顶盒(Set-top Box)的巨大市场需求,凸显了其重要性。在机顶盒的研发过程中,信源解码器的研制是整个开发工作的基础和核心。随着机卡分离政策的出台,信源解码器的通用性和复杂性,使其在机顶盒终端的开发过程中变得更加重要。本文论述的即为符合DVB-C标准的数字有线电视机顶盒信源解码器的设计与实现。

总体方案

机顶盒大体可以分成两个功能部分:信道解调解码部分和信源解码部分。信道部分即前端,负责对数字电视信号进行解调接收和信道解码。由于前端的不同,机顶盒可分为数字卫星机顶盒、数字地面机顶盒和数字有线机顶盒三种。

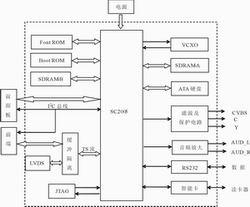

该信源解码器是针对数字有线电视机顶盒研制的,将配接L64768前端,组成符合DVB-C标准的完整机顶盒方案。本文采用LSI Logic公司的基于SC2005的第二代单片信源解码方案来实现解码功能。该解码器的结构框图如图1所示,按功能可分为4个部分:以SC2005为核心的CPU及存储控制子系统;传输流解复用和音视频解码子系统;图形处理和屏幕菜单显示及输出子系统;外围接口子系统。

图1 机顶盒信源解码器

硬件实现

该信源解码器的启动代码存储在Flash Boot ROM中,所用字体则存储在Flash Font ROM中。SC2005的两个SDRAM存储器接口分别与SDRAM-A和SDRAM-B相接。系统加电后,保存在Flash Boot ROM中的启动代码被调到SDRAM-B中执行。时钟由27MHz压控振荡器经倍频后提供。压控振荡器产生的时钟信号经过74LVC14整形后送到SC2005的VCXO引脚,并通过SDET引脚的输出进行同步恢复。传输流复用、音视频解码、图形处理等功能均由SC2005内部相应的集成模块配合外部相关电路来实现。

CPU及存储控制子系统

SC2005集传输解复用器 L641x8和MPEG-2音视频解码器L64105的功能于一体,内含EZ4102内核、16KB指令Cache和8KB数据Cache,这是SC2005的核心组成部分。

该信源解码器所用的两片1M×16bit Flash ROM均为AM29LV160DT-70,使用单一电源供电,读写和编程均使用3.3V电压,高速70ns读写时间。它们通过E-Bus与SC2005相连,地址总线A[6:0]和SC2005的ADDR[7:1]相连,A[19:7]和SC2005的AD[28:16]相连,数据总线DQ[15:0]和SC2005的AD[15:0]相连。芯片内部共有35个扇区,其中4个作为引导扇区,大小为4k字~16k字,其余31个扇区为32k字;有一个字节/字模式选择引脚BYTE#,本设计中该引脚接高电平,选择字模式。

81MHz/1M×16bit的SDRAM-A和108MHz/2M×16bit的SDRAM-B通过S-BUS 与CPU的SDRAM存储器接口相连。其中SDRAM-A专门用于MPEG解码时存储视频帧和相关信息,SDRAM-B存储解复用、OSG和外围设备接口子系统的信息。SDRAM-A与SDRAM-B之间可通过一个DMA引擎直接传送数据。

传输流解复用和音视频解码子系统

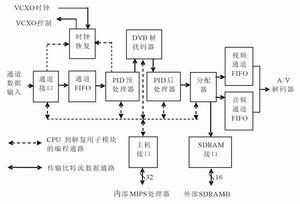

SC2005首先接收来自信道解码器或码流发生器的TS流,然后自动进行传输包同步检测。一旦同步建立,就会将传输包发送到PID预处理器中。PID预处理器分析输入的传输包,检查它们的PID值,只有和PID表匹配的PID值才能通过第一步滤波,不匹配的包被丢弃。通过PID滤波器的传输包被送到DVB解扰码器中,经过解扰的包进入PID后处理器,在经过滤波后,音视频PES数据直接进入A/V解码器中,而其它数据被送到外部SDRAM-B的循环缓冲器中,CPU能直接从存储器中读数据。传输流解复用子系统的结构框图如图2所示。

图2 传输流解复用子系统

解复用后的音视频PES流通过A/V接口进入L64105 MPEG-2解码器进行分组解码。L64105输出数字视频和数字音频信号各两组。一组数字视频和一组数字音频信号直接输出。另一组的数字视频信号送到视频编码器中,被转换成全电视信号(CVBS)或S端子信号(Y/C),经过外部低通滤波后,直接送到电视机中;数字音频信号送到音频DAC中,转换成立体声模拟信号,经外部低通滤波后输出。

图形处理和屏幕菜单显示输出子系统

SC2005集成了高性能的OSG(On-Screen Graphics)子系统,该子系统可产生文本和图形并叠加到解码的视频上。OSG子系统产生静止层、OSD层和光标层;解码子系统提供视频层;混合器/编码器子系统产生背景颜色层,并在视频输出之前将上述5层进行编码复合,从而根据需要显示所要输出的复合视频。这个子系统将来自OSG子系统的图形和解码视频数据进行混合编码,然后输出NTSC/PAL/SECAM制式的RGB/YPbPr、CVBS或S视频信号给电视机或监视器。

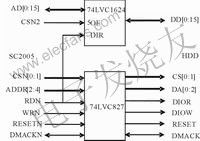

图3 ATA硬盘接口

外围接口子系统

该信源解码器集成了一个ATA硬盘接口,如图3所示。用户可以通过此接口实现个人数字录像机PVR(Personal Video Recorder)功能;还可在硬盘中开设海量缓存区,在播放数字电视的同时,对节目进行长达数小时的实时存储。依赖这种缓存技术,用户可以进行时移播放。

该解码器拥有一个TDA8004T智能卡接口和符合IEEE 1149.1标准的JTAG模块,提供了基本的调试功能,还提供了LVDS接口,用来接收码流发生器输出的TS流。由DB-25接口输入的LVDS信号通过3片DS90C032进行电平变换后,进入解码器。此外,该系统还使用了一个UART,用于机顶盒的调试和软件升级。

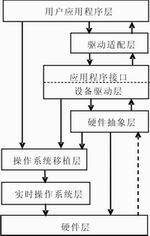

图4 机顶盒软件分层框架

软件设计

软件系统基于一个分层的框架,其中,部分由LSI Logic在其参考软件中提供,其它部分需要由用户自行开发。软件的整体结构如图4所示。

实时操作系统层(RTOS)是所有上层程序代码运行的基础,主要负责多任务调度、系统资源管理、中断处理、通信操作和同步处理等。本文使用的是WindRiver公司专门为嵌入式系统设计和开发的一个模块化、高性能的实时操作系统pSOSystem。RTOS层用板级支持包(BSP) 来实现与硬件层接口。

操作系统移植层(OSP)实现两个主要功能:一个是动态配置任务的属性,如上下文的切换,优先级等;另一个是管理任务之间的通信,如数据传输与同步。硬件抽象层(HAL)负责直接对硬件寄存器编程;设备驱动层(DDL)是硬件抽象层的一个明了、方便的备份和封装,主要针对各硬件模块提供相应的驱动程序,如SC2005异常处理的驱动、时钟服务模块的驱动和OSG图形库的驱动等。应用程序接口层(API)为上层的应用程序提供API函数。

驱动适配层(DAL)是对设备驱动层功能的进一步集合,通过功能组合可以直接应用到应用程序层,它起到了接口的作用。例如对Flash的操作,可以用这样的一个驱动适配层进行功能的进一步封装,以利于上层应用程序的调用。

用户应用程序层是机顶盒用户应用软件的主体部分,也是软件开发的重点。与机顶盒有关的所有上层功能的实现都在这层完成,如关于用户界面功能的实现、EPG的实现、节目数据库的管理、用户信息输入/输出控制和软件升级等。

-

机顶盒

+关注

关注

4文章

392浏览量

54553 -

芯片

+关注

关注

458文章

51539浏览量

429640 -

解码器

+关注

关注

9文章

1157浏览量

41148

发布评论请先 登录

相关推荐

立足UHD机顶盒SoC视讯解码效能 IC商蓄势待发

机顶盒芯片解决方案群英荟萃

[原创]有线数字电视系统用户接收解码器(机顶盒)技术要求和测量方法 GD/J 12-2007

机顶盒小知识

数字机顶盒的结构和原理

意法半导体推出支持3D的机顶盒芯片STi7108

ST推出最新标清机顶盒解码器芯片STi5206

基于SC2005的DVB-C机顶盒信源解码器

采用SC2005做主芯片的机顶盒信源解码器的设计与实现

采用SC2005做主芯片的机顶盒信源解码器的设计与实现

评论