FIR(finite impulse response)滤波器是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位冲激响应是有限的,没有输入到输出的反馈,是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

目前FIR滤波器的硬件实现有以下几种方式:

一种是使用单片通用数字滤波器集成电路,这种电路使用简单,但是由于字长和阶数的规格较少,不易完全满足实际需要。虽然可采用多片扩展来满足要求,但会增加体积和功耗,因而在实际应用中受到限制。

另一种是使用DSP芯片。DSP芯片有专用的数字信号处理函数可调用,实现FIR滤波器相对简单,但是由于程序顺序执行,速度受到限制。而且,就是同一公司的不同系统的DSP芯片,其编程指令也会有所不同,开发周期较长。

还有一种是使用可编程逻辑器件,FPGA/CPLD。FPGA有着规整的内部逻辑块整列和丰富的连线资源,特别适合用于细粒度和高并行度结构的FIR滤波器的实现,相对于串行运算主导的通用DSP芯片来说,并行性和可扩展性都更好。

FIR滤波器的主要组成模块是乘累加单元(MAC),如果按照直观结构构造乘法器和系数寄存器来实现会占用大量的逻辑资源,显然不可取。本文采用基于分布式算法思想的方法来设计FIR滤波器,并在FPGA上实现。

1 分布式算法原理

分布式算法(distributed arithmetic,DA)最初是在1973年由Croisier提出的,但直到Xilinx发明FPGA的查找表以后,DA算法才在上世纪90年代初重新受到重视,并有效地应用在FIR滤波器的设计中。DA算法的原理如下。

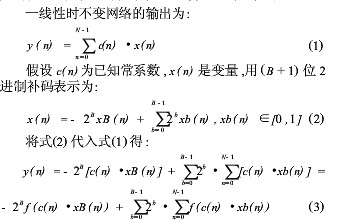

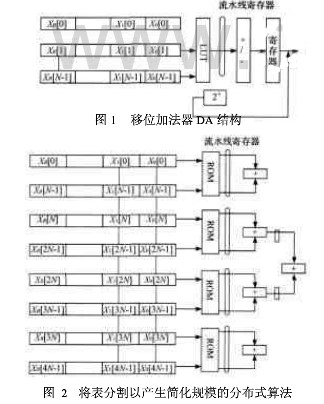

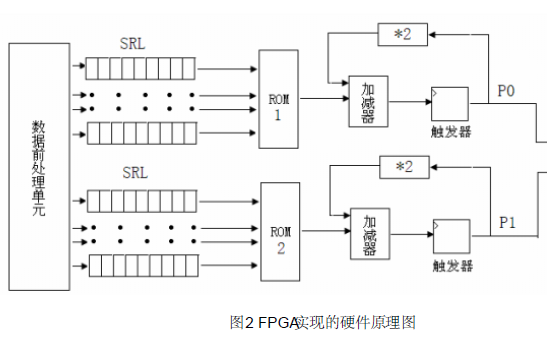

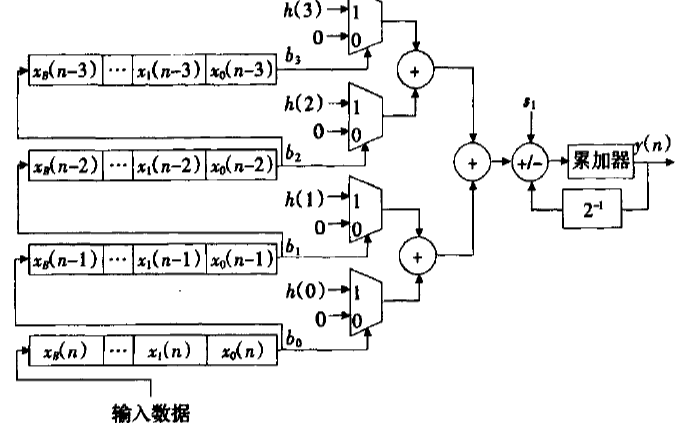

函数f(c(n),xb(n))的实现方法是利用一个LUT(查找表)实现影射f(c(n),xb(n)),也就是说2N字宽、预先设定程序的LUT接收一个N位输入向量xb=[xb[0],xb…xb[N-1]],输出为f(c(n),xb(n)),个个影射,f(c(n),xb(n))都由相应的二次幂加权并累加。对于固定系数,整数乘以2b即左移6位,可以通过硬连线实现,不占用逻辑资源,利用图1所示的移位加法器就能有效地实现累加。DA算法的主要特点是巧妙利用SRAM查找表将固定系数的MAC运算转化为查表操作,其运算速度不随系数和输入数据精度的增加而降低,而且相对直接实现乘法器和系数寄存器在逻辑资源占用上得到了极大的改善。缺点是查找表的大小随滤波器的阶数的增加呈指数增长,这时可以采用将大查找表分解为小查找表的方法来降低逻辑资源的消耗,如图2所示。

2 FIR滤波器的网络结构

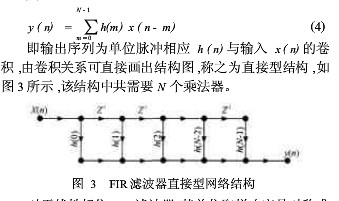

N阶FIR滤波器相对于输入时间序列x(n)的输出表达式为:

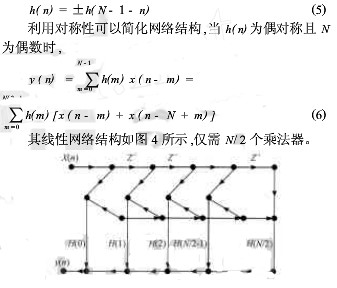

对于线性相位FIR滤波器,其单位取样响应是对称或反对称的,即:

3 FIR滤波器的硬件电路设计

下面以一个32阶FIR带通滤波器为例说明硬件电路设计的方法和过程。

3.1 设计指标

采用频率:200 Hz 类型:带通

上限截止频率:54.3 Hz 下限截止频率:46 Hz

阶数:32阶 系数数据宽度:16位

输入数据宽度:16位 输出数据宽度:16位

3.2 滤波器的设计

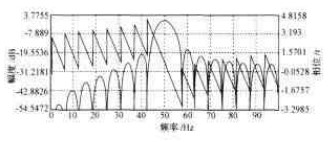

使用MATLAB 7.1软件中Filter Design&AnalysisTool,选取带通滤波器,Kaiser窗设计方法,设计出符合设计指标的32阶线性相位FIR滤波器,其幅频特性和相频特性如图5所示。

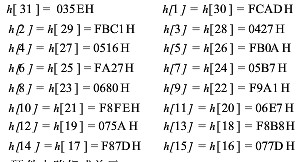

滤波器的特征参数用16位二进制补码表示如下:

(1) 数据位扩展:由于输入数据要进行预相加,为了防止溢出,保证电路正常工作,采用符号位扩展,使输入数据由16位增加到17位。

(2) 并串转换器:由于电路以串行方式工作,须将并行输入的数据转换为串行数据输入,且顺序是先输入低位(LSB),后输入高位(MSB)。

(3) 移位寄存器组:其主要功能是用寄存器组存储输入序列,实现输入数据的延时输出,存储的级数等于FIR滤波器的阶数减1,即31。移位寄存器组输出的数据和并串转换器输出的数据一起形成如图1中所示的输入数据阵列形式。

(4) 预相加单元:利用FIR滤波器系数的对称性,按照图4所示的FIR滤波器线性网络结构,将相同滤波器系数相乘两个输入数据预先相加,这样相当于将滤波器的阶数减半,减小了硬件规模。预相加单元采用在位串行电路中广泛应用的串行加法器来实现。

(5) 查找表单元:如前所述,LUT的规模随滤波器阶数的增加呈指数增长,当滤波器的阶数很大时,查找表的规模过于庞大。为了减小规模,可以将1个有16位地址总线的LUT分割,产生4个4位地址总线部分LUT,先分别对4个部分表查表,再将结果相加。为防止相加时产生溢出,将16位查表输出经过1位符号扩展变为17位。

(6) 查表结果相加单元:加法器是影响FIR滤波器性能的主要部件,其工作速度决定了FIR滤波器的效率,因此采用具有超前进位功能的流水线加法器。

(7) 移位累加单元:得到的查表结果相当于一个部分积,移位累加单元将其与寄存器中的部分积相加,结果右移1位还放入寄存器中,直到所有的位数都查表结束。特别应注意,最高位查表得到的结果不是与上一个右移1位的部分积相加,而是相减。这里的加法器仍是采用具有超前进位功能的流水线加法器,作减法时,只需将被减数取补即可。

(8) 锁存输出单元:加法器的输出不稳定,将其结果经过一锁存器得到稳定的输出。

(9) 控制单元:产生复位,时序等控制信号,控制电路的总体运行。

3.4 电路仿真

在ALTERA公司的MAX+PLUS2软件环境下,用硬件描述语言VHDL对上述FIR滤波器的模块进行编程描述,并仿真各模块的波形,最后将各模块综合起来下载到器件FLEX10KE中形成FIR滤波器。

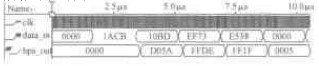

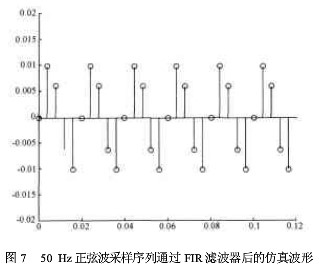

用MATLAB设计了一幅度为0.22的50 Hz的正弦波,用250 Hz的采样器对其采样,得到周期序列[0,0.209 2,0.129 3,—0.129 3,—0.209 2],用16位二进制补码表示为:[0000H,1ACBH,108DH,EF73H,E538H],将其输入到FIR滤波器的输入端,滤波器的输出如图6所示,实验结果与理论计算一致。并取32位以后的输出结果,在MATLAB里绘制波形,如图7所示,可见,FPGA仿真结果正确,50 Hz的正弦波通过了FIR滤波器。

4 结 论

本文所介绍的基于FPGA、采用分布式算法实现FIR滤波器的方法,在提高系统运行速度和节省硬件资源方面具有很大的优势。而且,通过改变阶数和查找表中的系数,还可以将此设计灵活地运用于实现高通、低通和带阻滤波器,可移植性较好。因此,这种方法在高速数字信号处理中将有很好的应用前景。

-

FPGA

+关注

关注

1629文章

21735浏览量

603189 -

cpld

+关注

关注

32文章

1248浏览量

169349 -

滤波器

+关注

关注

161文章

7805浏览量

178070

发布评论请先 登录

相关推荐

FIR数字滤波器分布式算法的原理及FPGA实现

一种基于分布式算法的低通FIR滤波器

如何使用FPGA和分布式算法实现FIR低通滤波器的设计

基于FPGA器件采用分布式算法实现FIR滤波器及仿真研究分析

基于FPGA器件采用分布式算法实现FIR滤波器及仿真研究分析

评论