1 引 言

通信技术的发展,对于系统可靠性的要求不断提高,特别在移动通信领域,数字信号的传输过程常会伴随有各类的干扰源,从而使得信号产生失真,影响通信质量。纠错编码技术可以纠正信道中的随机干扰产生的数字信息序列的随机错误。但是,仅利用纠错编码技术,对于传输过程中的突发性干扰,需要借助于很长的码字,这样会增加编译码器的复杂性,同时也会产生较大的时延。

交织技术作为一项改善通信系统性能的方式,将数据按照一定的规则打乱,把原先聚集成片的误码分散,使得突发性错误转化为随机性错误,这样,纠错后的误码个数则在纠错码的纠错范围内,接收端就可以用较短的码字进行纠错。

2 交织器的性能分析

2.1 交织器类型的选择原则

常用的交织器主要有3种:矩阵分组式、伪随机式和半伪随机式。

矩阵分组式交织器,由于序列较短的伪随机数之间的相关特性较大,对于实时性要求高、信息帧较短的通信系统,性能优于伪随机和半伪随机式交织器。

随着信息帧长度的增加,交织长度也相应增长,此时若采用矩阵分组交织器,交织前后信息序列的不动点增多,伪随机数产生更加均匀,交织前后的序列相关性减小,所以对于译码精度要求较高的通信系统,应采用随机交织器。半伪随机交织方式则为折衷的方案。

2.2 矩阵分组交织原理

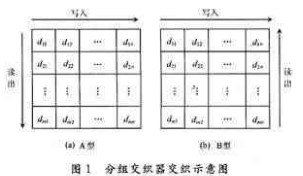

分组交织器的结构较为简单,他是一个m×n的矩阵。他按行的顺序写入存储器,再按列的顺序读出。根据读出方式的不同,分组交织器可分为两种不同的类型:A型分组交织器和B型分组交织器。按行写入,按列的先后顺序逐列读出,称为A型交织器;按行写入,按列的倒序读出,即从最后一列向第一列读出,而对于每一列则是按照从最后一行向第一行的顺序读出,称为B型交织器。

如图1所示,假设信息比特的输入顺序是:d11,d12,…,d1n,d21,d22,…,d2n,…,dm1,dm2,…,dmn。对于A型分组交织器,读出顺序为:d11,d21,…,dm1,d12,d22,…,dm2,…,d1n,d2n,…,dmn;对于B型分组交织器,读出顺序为:dmn,…,d2n,d1n,…,dm2,…,d22,d12,dm1,…,d2l,d11。

对于任何长度l≤m的突发错误经交织后成为至少被n-1位隔开的一些单个独立差错。

3 交织器的设计

本节针对CDMA2000的话音标准速率为9.6 kb/s,相应每帧数据长度为192 b。给出了用可编程逻辑器件来实现A型分组比特交织器。采用的软件开发环境是Max+PlusⅡ,采用自顶向下(Top-Down)的设计方法。

3.1 交织形式的选择

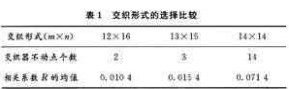

交织形式的选择应保证传输的数字序列在交织前后不动点最少,并且相关性最小。CDMA2000中每帧的数据长度分别为192 b,每帧大约为20 ms。那么可选用的交织长度只能与此大致相当。文献计算比较了12×16,13×15,14×14三种交织型式,如表1所示。分析可知,我们的设计应采用12组码字进行交织,每组16 b码长,交织长度为192 b。

3.2 整体设计

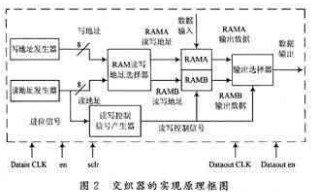

本设计以RAM块作为主体模块,交织器的实现主要由3部分组成:地址产生模块、控制模块和作为交织数据存储的交织寄存器模块。

为了保证对于传输数据序列交织的连续性,选取了2片RAM块用来进行交织存储。采用乒乓的工作方式,如此反复循环,在保证传输实时性的条件下,就完成了数据的交织。

图2示出了具体的交织器的实现原理框图。该系统有6个输入信号,分别为输入数据时钟信号(DatainCLK),系统工作允许信号(en),系统清零信号(sclr),输出数据时钟信号(Dataout CLK),输出数据允许信号(Dataout en)和待交织信息序列。该系统有一个输出信号,为交织后的信息序列。

3.3 读写地址产生模块

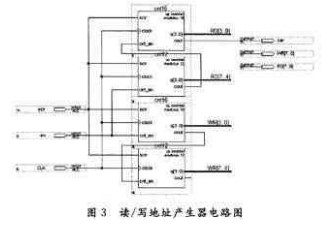

图3给出了应用Max+PlusⅡ软件对交织器读/写地址产生器进行设计的具体的电路连接图。

图4给出了选用Max+PlusⅡ软件菜单命令File/Create Default Symbol,生成的读/写地址产生器的逻辑符号。这样该读/写地址产生器就可以像其他逻辑符号一样,在图形设计文件中任意调用。该逻辑符号的输出除了8位读/写地址外,还有一个进位信号CAR。该进位信号供控制模块产生控制信号使用。

3.4 交织器的整体电路

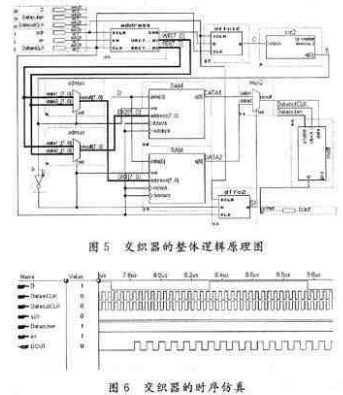

图5给出了应用Max+PlusⅡ软件实现的交织器设计的整体逻辑原理图。

3个二选一的选择器。其中有2个选择器在控制信号的作用下分别完成对2片RAM读/写地址的选择,因为2片RAM的读写顺序正好相反,所以应对控制信号进行相应的取非操作。另一个选择器完成对2片RAM输出数据进行选择,选择器的最终输出数据作为交织后的数据。由于数据在存入和读出RAM时引入了一个半周期的延时,所以应用了2个D触发器dffc2来消除使能信号与时钟之间的延时。数据输出端的D触发器mdff是为了消除输出信号的毛刺而设计的。

根据系统的工作原理,设计出控制时序,进行仿真的结果如图6所示。

系统仿真时输入交织器的串行码组为0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1交替序列,由A型分组交织器的工作原理可知,得到的交织后的输出数据为O,1交替的序列。该波形仿真结果表明交织器正常工作。从图6中可以看出,该交织器从待交织数据输入到交织后输出有7.79μs的延时存在。图中在7.79μs以前,输出的数据为0是因为RAM块中的初始数据为O。

3.5 解交织器的设计

解交织是交织的逆过程,这决定了解交织器和交织器对于交织数据在交织矩阵中的读/写顺序正好相反。在解交织器的设计中.改动的部分只是在2片RAM的读/写选择信号前分别加了一个非门。从而可以完成解交织数据按交织地址写入,按顺序地址读出,进而完成解交织过程,恢复出原始数字信息序列。

4 结 语

短帧数字通信系统适合采用矩阵式分组交织,本文以CDMA2000语音传输标准下短帧为例,给出了具体的12×16的A型分组比特交织器和解交织器。在实际中,该设计方案在不增加系统复杂度的情况下,只需对相应的模块进行修改,很容易实现交织深度和形式的改动,具有重要的参考价值。

-

FPGA

+关注

关注

1630文章

21759浏览量

604289 -

ARM

+关注

关注

134文章

9107浏览量

367986 -

移动通信

+关注

关注

10文章

2614浏览量

69935

发布评论请先 登录

相关推荐

怎么在Matlab中实现数字通信FPGA硬件设计?

基于CPLD的短帧交织器设计实现

基于CPLD FPGA的数字通信系统建模与设计

采用RAM模块与FPGA器件实现短帧数字通信系统设计

采用RAM模块与FPGA器件实现短帧数字通信系统设计

评论