引言

对于IO互联体系架构的复杂要求是系统工程化应用需要直接面对的挑战。DSP互联技术的研究已经成为新兴的热点问题。

DSP之间互联的方式有很多种,高带宽的片间、板间互联技术成为需要重点突破的关键技术。

1 高速互联点对点交换技术

无论是单分段共享总线互联系统,还是级联的多分段共享总线互联系统,在这类基于共享的总线体系结构中,所有通信无不是在争用总线带宽,由此造成外设越多可用带宽就越少,从而带来严重的传输瓶颈。不仅如此,在基于共享的并行总线上,大量的引脚数目也带来一定的电气特性和机械特性等问题,使得信号频率以及信号可传输距离都受到很大程度的制约。

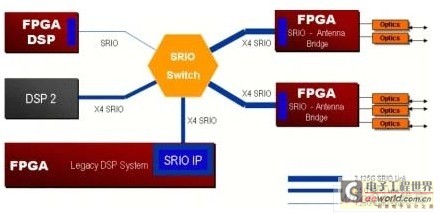

因此,需要一种可升级的新型高性能系统体系结构,于是出现了点对点交换式总线,典型的新型总线有PCI-Express、InfiniBand、Hyp erTransport、RapidIO等。

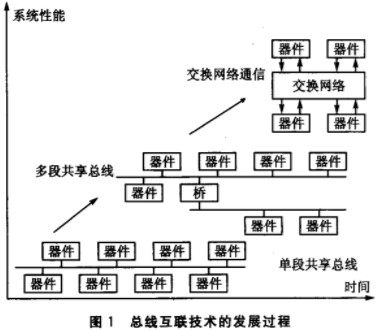

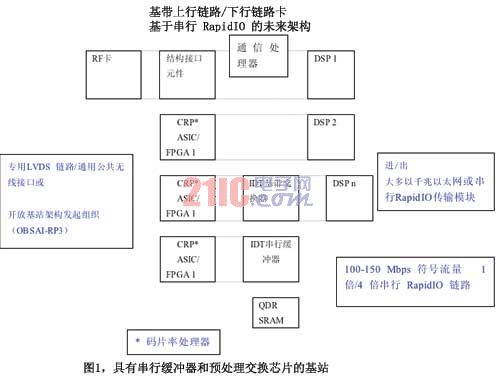

总线互联技术的发展过程如图1所示。其中,Infiniband的目标应用是系统域(SAN)互联,系统域网络用于构建集群系统以得到更大的系统。RapidIO互联架构是一个开放的标准,可以满足嵌入式基础设施在应用方面的广泛需求。HyperTransport和PCI-Express虽然具有某些与RapidIO相同的特征,但把它们视为PCI总线的点到点版本更为恰当。

在这几种新型总线技术中,RapidIO主要面向高性能嵌入式系统互联通信,是一个开放的点对点分组交换标准,可连接多处理器、存储器、网络设备中的存储器映射I/O器件、存储子系统等。这一互联技术可以实现1~60Gbps的性能水平,可以在8对LVDS差分线上实现全双工的10 Gbps数据传输。RapidIO以其高带宽、低延时及具备硬件保证达99.999%的高可靠性(即系统处于出错状态的时间仅为0.001%)为多核DSP系统的互联提供了良好的解决方案。

2 基于RapidIO多核DSP系统高速互联的设计

2.1 RapidIO IP核的设计

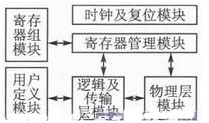

RapidIO IP核可以分为6大部分:逻辑及传输层协议实现。包括负责事务组包、拆包等功能的逻辑及传输层模块;物理层协议实现,包括包的控制符号传送、流量控制、错误管理等功能的物理层模块;负责对寄存器进行读写操作的寄存器管理模块;集中实现各层寄存器的寄存器组模块;时钟及复位模块;用户定义模块。其结构如图2所示。

2.2 多核DSP互联接口总体方案

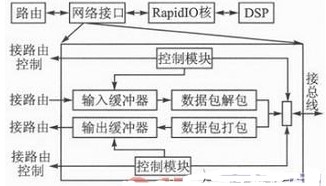

越来越多的高速信号处理系统采用多DSP核进行数据运算,用可扩展的RapidIO构建互联结构是非常有效的一种方式。例如一个可扩展的4核DSP系统,网络采用4×4的mesh拓扑结构,在4块芯片上实现,芯片内部互联采用并行总线,芯片之间互连采用基于RapidIO物理层协议的高速串行总线,结构如图3所示。

这样的设计并非把RapidIO应用集中,把单个芯片作为RapidIO拓扑结构的一个节点,而是把整个片上网络作为RapidIO拓扑结构的一个节点。网络内部的协议完全自定义,不仅能利用RapidIO接口对基于片上网络架构的多核DSP系统作片外扩展,又能使片上网络的拓扑结构不依赖于RapidIO独立设计。因为在RapidIO的拓扑结构中,数据交换的单元是交换开关,而本设计中数据交换由独立于RapidIO协议的路由器来完成。如果需要兼容其他的总线协议,只需要更改网络接口的设计,极大地简化了工作。

2.3 4核DSP网络接口的结构

为了实现多核DSP之间的数据通信,互联接口必须能够解析来自片上网络的数据包并转换成RapidIO IP核所需要的数据格式,或者接收来自RapidIO IP核的数据,并按照网络协议组装成数据包在网络上发送,实现片上网络同片外DSP核的通信。互联接口要支持不同时钟域的数据传输,满足片上网络全局异步、局部同步的时钟要求,还需要能够检测来自网络数据包的错误,保证可靠传输,并使用基于信用量的流控机制,防止缓冲器溢出造成数据丢失。网络接口使用多个虚通道技术缓解网络死锁,提高网络的吞吐率。根据这些要求设计的多核DSP互联接口结构如图4所示。

4个DSP通过串行RapidIO互相连接起来,在几个DSP内部利用串行RapidIO协议,数据在几个DSP之间高速运转。另外,还可以通过一个外部的控制处理器来实现控制这几个DSP的一些功能,可根据需要给每个DSP分配不同的算法模块,对多个DSP进行负载均衡,从而实现更高的运算效率。

3 RapidIO专用电路中核心IP模块设计

RapidIO协议可以用大规模集成电路来实现,通过协议本身的控制作用完成对数据通路的控制作用。因此RapidIO专用集成电路就是基于这个协议的框架结构,从根本上解决嵌入式系统互连的通信问题,从而提高系统的整体性能。

3.1 发送和接收IP模块设计

发送和接收模块主要围绕采用的双端口存储器进行复杂的控制逻辑设计。根据协议的要求,可在RapidIO专用电路的双口SRAM中规定一个口写数据,一个口读数据,从而降低控制逻辑设计的复杂性。在本设计中规定A口是只写的,而B口是只读的,它们的数据宽度为32位,深度为1024。

3.1.1 发送缓冲IP模块设计

在双口SRAM的外围设计了较复杂的控制逻辑构成发送缓冲区,A口和B口的地址计数器的地址由两部分组成:ID号和地址递加计数逻辑。A口的输入数据来自于RapidIO封装的数据帧,而B口的输出数据又被送到了RapidIO发送状态机内,只不过B口的数据是需要重发的数据。

因为RapidIO数据帧最大为68个双字,发送窗口数被设计成7,所以已经发送的数据在这个双口SRAM中是分段保存的。当RapidIO发送状态机开始发送数据,同时对数据进行封装时,A口的写信号有效,并且A口的计数器进行递增计数,递增计数器和段地址构成了A口的有效地址。这样已发送的数据就被保存在这个以双口SRAM为核的缓冲区队列中(最多为476个双字数据)。在这个双口SRAM的外围设计了段指示变量用来指示在该段中保存字数据的个数(因为发送的数据可能有不够256个字节,即64个双字的情况)。

相邻节点返回的数据响应帧内,包含相邻节点希望接收的下一个数据帧的序号ID,当数据响应帧类型为datanot accept或data retry类型时,激活了发送状态机内的重发机制,B口当前地址和A口的段指示变量进行比较,当B口的当前地址和A口相应的段指示变量相等时,通知发送状态机该数据已经被重新发送完毕,结束帧的发送。只有该帧数据的正确的响应帧被接收到时,A口才能继续发送新的数据,并且发送缓冲区的窗口向前滑动。通过使用这种方法,已发送的数据就源源不断地保存在这个缓冲区队列中,而且不会丢失。

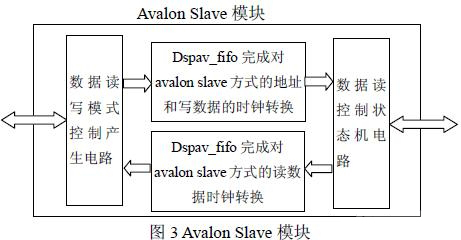

3.1.2 接收缓冲IP模块设计

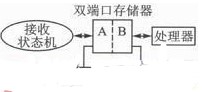

在双口SRAM的周围加入了一些外围的控制电路构成了接收缓冲区。双口SRAM的A口和接收状态机相连,双口SRAM的B口和处理器接口相连。A口和B口分别使用了地址计数逻辑。接收缓冲IP模块如图5所示。

由于RapidIO的一个数据帧是以272字节封装的,并且在数据帧的第80个字节处插入了一个CRC校验序列,这样就增加了判断的难度。当接收机开始接收数据帧内嵌入的第一个CRC校验序列时,通过接收状态机进行判断:当接收到的第一个CRC校验序列和接收状态机本地产生的CRC一样时,A口的地址计数电路继续计数;当接收到的第一个CRC校验序列和接收状态机本地产生的CRC不一样时,说明前面接收到的数据是无效的,此时地址计数电路停止计数,并且地址指示变量减去20。

当接收完一个数据帧内的所有有效数据时(不包括数据帧末尾的CRC校验码),地址计数电路停止计数,同时在接收状态机内进行判断:当接收到的数据帧末尾的CRC校验序列和接收状态机本地产生的CRC校验序列一致时,地址指示变量的值不变;当接收到的数据帧末尾的CRC校验序列和接收状态机本地产生的CRC校验序列不一致时,地址指示变量减63(标准的数据帧内的有效数据是64个字)。通过这样的方法在由这个双口SRAM构造的接收数据缓冲区内保存了一个完整有效的数据帧。

3.2 发送/接收状态机

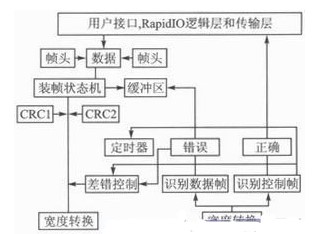

发送状态机和接收状态机模块包含了RapidIO协议的差错控制和流量控制的功能。差错控制功能主要是通过使用CRC校验机制和定时器机制来完成的。发送状态机和接收状态机是通过相互交换内部信息来实现对数据进行差错控制和流量控制的,如图6所示。

3.2.1 发送状态机模块设计

如图6所示,来自处理器接口的原始数据依次传送到RapidIO的逻辑层和物理层时,在数据的头部封装了地址、序号和长度等头部信息,同时发送状态机得到每个数据的CRC码;当数据大于80个字节时,在第80个字节的后面插入1个CRC码,然后在该数据帧的尾部插入1个CRC码,这样就将一个原始的数据转换成了1个RapidIO数据帧,然后将这个封装的数据帧传到串行化数据模块进行发送。

如果数据帧被对方节点正确的接收,则发送端口可以继续发送数据;如果数据帧被对方拒绝接收,则停止数据的继续发送,并且接收端口和发送端口通过同步控制帧重新进行端口同步,当这种同步重新建立后发送端口才可以继续发送数据;在发送状态机模块中采用了滑动窗口技术,一方面可大大提高数据的吞吐量;另一方面可以尽量避免由于接收方缓冲区资源不足而导致的多次发送失败。

3.2.2 接收状态机模块设计

当接收到数据帧后,对接收到的数据帧通过CRC校验机制进行错误检查,同时得到帧的序号和设备号等信息,并且将数据帧的接收状态通知本地发送端口,由本地发送端口根据接收数据的状态作出判断,然后向对方节点设备发送响应帧信号。

当接收状态机接收到一个完整的消息后,则由接收状态机向本地处理器接口发出中断信号,通知处理器将接收缓冲区内的数据取出;当接收状态机接收到控制帧后,根据控制帧的类型作出判断,如果是错误数据的响应帧,则本地发送端口和接收端口同时处于停止发送和接收数据状态,并且通知本地发送端口发送link请求帧和link相应帧,使得接收和发送链路重新建立连接;如果是用于链路控制的控制帧,则本地发送端口根据接收到的控制帧类型向相邻节点发送相应的响应控制帧。

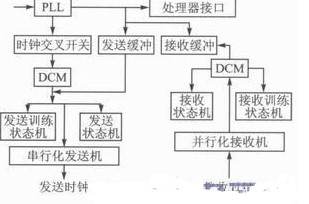

3.3 时钟信号设计

RapidIO协议规定使用双数据时钟发送和接收数据。

在专用电路内的时钟布局分为发送时钟模块和接收时钟模块两大子模块。对时钟的分频和倍频是通过专用集成电路内的数字时钟管理器DCM完成的。来自处理器的输出时钟要驱动专用电路芯片和其他外设,所以在专用电路的内部加入PLL,保证输出时钟能提供足够的时钟频率、驱动能力和较陡的时钟边沿。时钟资源在专用电路内的布局如图7所示。

发送时钟模块的主要功能包括:

①使用DCM的相移功能,提供RapidIO发送数据合适的采样时钟相位,包括从发送缓冲区将数据提取出来,以及在发送数据前提供的较好的冗余时钟相位,保证时钟能正确地采集发送的数据和帧同步信号。

②在进行数据串行化的时候,通过DCM的倍频功能将上层模块的数据发送变成双数据进行发送,即时钟的上沿和下沿同时发送数据。

③通过差分引脚将LVTTL发送时钟变为LVDS差分时钟进行发送。

接收时钟模块中的主要功能包括:

①接收到的差分LVDS时钟转换为LVTTL时钟。

②对接收到的时钟信号通过DCM对其进行分频,以便能够正确地将接收到的DDR数据转化为SDR数据。

③对接收到的时钟通过DCM进行相位移动,以便为接收缓冲区正确地接收数据提供正确的采样时钟相位。

除了此处提到的模块,RapidIO协议专用集成电路内部还有串行和并行模块,接口模块等,在此就不一一介绍了。

结语

适用于多核DSP系统的高速互联接口对于研究多核的体系结构具有实际意义。研制满足RapidIO协议的专用集成电路不仅可以快速实现网络结构,而且可以降低系统的功耗,提高可靠性,具有很好的应用价值。

-

dsp

+关注

关注

552文章

7964浏览量

348334 -

嵌入式

+关注

关注

5073文章

19038浏览量

303579 -

IP

+关注

关注

5文章

1668浏览量

149356

发布评论请先 登录

相关推荐

怎么利用FPGA实现DSP与RapidIO网络互联?

如何实现DSP与RapidIO网络互联?

怎么实现基于RapidIO的双主机节点嵌入式系统互联的设计?

看看在SpinalHDL中AXI4总线互联IP的设计

基于FPGA的串行RapidIO-PCI转接桥设计

基于Wishbone片上总线的IP核的互联

基于FPGA实现DSP与RapidIO网络互联

基于RapidIO和存储映射的高速互连网络

首款串行RapidIO 2.1 IP 解决方案(Altera

基于FPGA实现DSP与RapidIO网络互联

串行RapidIO提升模块化基站设计

利用串行RapidIO实现FPGA协处理

基于AXI总线的RapidIO端口控制器IP核的设计方法

基于串行RapidIO总线互联的核心IP设计

基于串行RapidIO总线互联的核心IP设计

评论