随着EDA技术的发展,由于其在电子系统设计领域中的明显优势,FPGA已经在许多方面得到了广泛应用,特别是在无线通信领域,FPGA以其极强的实时性,指令软件编程的极大灵活性赢得了巨大的市场。本文采用FPGA来设计一款广泛应用于计算机、Modem、数据终端以及许多其他数字设备之间的数据传输的专用异步并行通信接口芯片,实现了某一时钟域(如66 MHz)的8位并行数据到另一低时钟域(如40 MHz)16位并行数据的异步转换,并且客户可以根据自己的要求进行数据定义。完成数据在不同时钟域间的正确传递的同时防止亚稳态的出现,保持系统的稳定,是电路设计的关键。

1 时钟域转换中亚稳态的产生

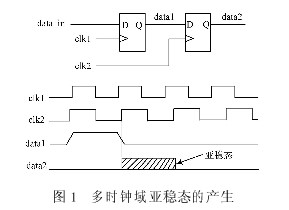

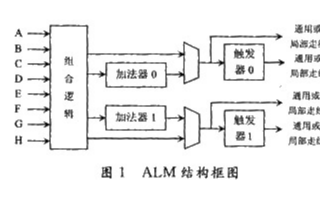

触发器是数字电路设计中的一个重要元件,而触发器工作过程中存在数据建立与保持时间的约束,如果这种约束得不到满足,触发器就会进入某个不确定状态——亚稳态。亚稳态的存在可能导致连锁反应,以致引起整个系统功能混乱。在单时钟域电路设计中由于不存在时钟之间的延迟和错位,所以建立条件和保持条件的时间约束容易满足。而在多时钟域里由于各个模块的异步性,则必须考虑亚稳态的发生,如图1所示。

2 多时钟域数据传递方案

多时钟域传递的信号有两种,其一为控制信号,其二为数据流信号。针对这两种不同的信号,分别采取不同方案遏制系统堕入亚稳态。对控制信号采用同步器装置,即在2个不同的时钟域之间插入同步器;而对于不同独立时钟域之间的数据流传递,为了避免异步时钟域产生错误的采样电平,采用FIFO存储器作为其转换接口,在输入端口使用写时钟写数据,在输出端口使用读时钟读数据,这样就完成了异步时钟域之间的数据交换。

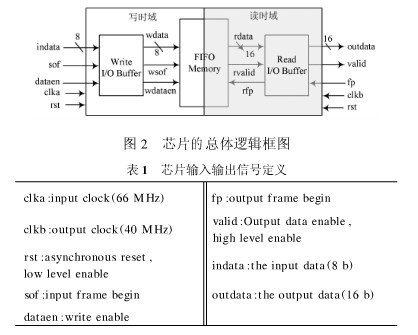

芯片的总体逻辑框图如图2所示,图中输入输出信号定义如表1所示。

从逻辑结构上将芯片划分为3块:写时钟域I/OBUFFER、读时钟域I/O BUFFER及FIFO存储器。I/O BUFFER的主要作用是对外部信号进行预处理,消除外部信号的毛刺,保证信号可靠并使外部的信号与时钟信号同步,消除不稳定的因素。根据信号的数目,BUFFER由相应数目的多个D触发器构成。

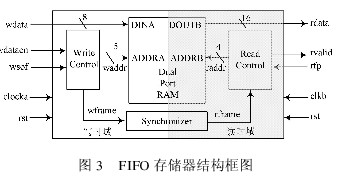

FIFO存储器结构框图如图3所示,他由双端口存储器(Dual Port RAM)、写控制单元(Writc Control)和读控制单元(Read Control)构成。其中DUAL PORT RAM是由ISE6.0的一个编辑软件CORE GENERATER自动生成,使用者只需设定RAM的端口数、内存大小和渎写控制便可以生成一个适合程序的子模块。由于读写时钟属于不同的时钟域,满帧信号Frame从写控制单元向读控制单元传递时必须采取同步器(Synchronizer)同步。

2.1 写控制单元设计

写控制单元主要的功能是根据写数据有效信号wdataen判断输入数据是否正确,在检测到写入数据帧的开始标志位wsof后开始计数控制写指针waddr的移动,将正确的数据写入DUAL PORT RAM中,并在一帧数据写满后向读控制单元发出写数据满帧信号wframe。为防止亚稳态的出现,设计中采取了两个措施:一是采用锁存器将帧头信号wsof拉长,确保其被稳定的采集;二是采用Gray编码计数器替代普通二进制编码计数器来控制写指针waddr的移动,因为Gray码相邻两个编码之间有且只有1位发生变化从而抑制了竞争冒险的出现。

2.2 同步器设计

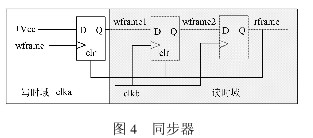

写控制单元发出的写数据满帧信号wframe属于控制信号,他从写时域进入读时域必须采用同步器实现信号同步,将写时域的满帧信号wframe变换为读时域的满帧信号rframe。由于信号是从高时钟域(66 MHz)流向低时钟域(40 MHz),因此采用如图4所示的同步器。

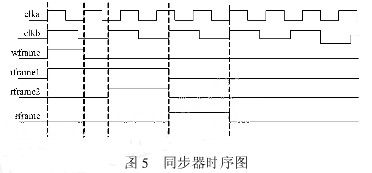

同步器时序图如图5所示,可见在写时域的满帧信号wframe经过3个clka周期延后跨越到读时钟域。

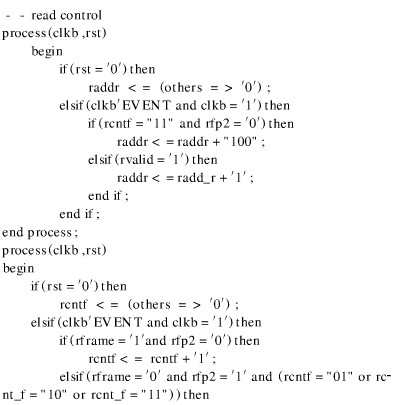

2.3 读控制单元设计

数据从写时域传递到读时域,时钟发生了变化,而且读控制单元的行为受到写控制单元及Dual Port RAM中数据的存储情况的双重制约,因此他的设计是整个芯片设计成功的关键。

由于当Dual Port RAM中写入一帧完整的正确数据后才能输出,所以读控制首先必须判断Dual Port RAM一帧是否写满。榆测到满帧信号rframe后,在等待输出数据帧头信号rfp到来后控制读指针waddr移动读出数据,并置位rvalid表征输出数据的可靠性。

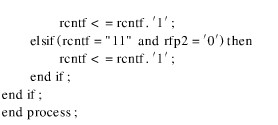

部分程序没计如下:

3 多时钟域数据传递的FPGA实现

设计方案完成后选用Xilinx Spartan.II FPGA实现电路,并在XilinxISE6.0集成环境下用Modelsim5.7进行了电路仿真。

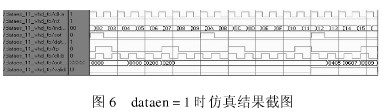

图6为写使能信号dataen恒为有效值“1”的仿真结果截图。

可见,在写使能信号dataen恒为有效值“1”的情况下,在写时钟clka控制下当写数据帧头信号sof有效时,写控制器开始写入数据,接收到连续8个数据后,写控制器发出一个帧满信号wframe。wframe信号经过异步转换后转换成clkb时钟域的信号。在读控制器的控制下,当clkb时钟处于上升沿,并且检测到读出数据帧头fp时,开始从outdata向外发送数据,并将valid置为有效。

图7为当写使能信号dataen变化时的仿真结果截图。

可见,将dataen置低后,系统不再接受写入数据,所以也不再输出数据,valid被置为低电平,输出数据无效。写控制的使能端控制达到要求。

4 结 语

针对异步并行通信接口芯片设计中涉及的多时钟域的数据传递问题,本文采用FIFO存储器来完成不同时钟域之间数据流传递、同步器来完成控制信号传递的方案。仿真验证结果表明,数据传递准确、稳定、可靠,没有出现竞争冒险和亚稳态,完全达到了设计要求。

-

FPGA

+关注

关注

1634文章

21830浏览量

608037 -

存储器

+关注

关注

38文章

7552浏览量

164808 -

触发器

+关注

关注

14文章

2024浏览量

61469

发布评论请先 登录

相关推荐

基于FPGA的异步FIFO的实现

基于FPGA器件实现异步FIFO读写系统的设计

多时钟域数据传递的Spartan-II FPGA实现

【FPGA参赛作品】生理电信号同步多通道数据采集系统的设...

采用FPGA的数字视频接口转换设备设计

采用FPGA的数字视频接口转换设备

采用FPGA实现数字视频转换接口设计

采用FPGA的数字视频接口转换设备设计

等效时间采样技术的原理作用及采用FPGA器件实现系统的设计

采用StratixⅡ FPGA器件提高加法树性能并实现设计

采用FPGA器件实现低时域数据异步转换

采用FPGA器件实现低时域数据异步转换

评论