智能电表的设计,由于微控制器的引入,对设计者提出了更高的要求。这是因为由于电源等引入的干扰可能导致程序指针跳飞,从而引起不可预测的后果,诸如电量数据的丢失、改变或死机等。像家用电脑和普通仪器仪表对死机等现象是允许的,可以通过人工复位,重新设置等手段来恢复,求长年连续的挂网运行,如果运行中出现任何异常现象,均要求能自动恢复正常工作。然而,在工程实际中,噪声和干扰是不可避免的。目前,大多数智能电表都应保证在干扰较强的现场运行,因此如何提高智能电表的抗干扰能力,保证其在规定条件下正常运行,以及防止仪表内部产生的噪声对外部的辐射,是智能仪表设计中必须考虑的问题,也是关键问题。

二、硬件抗干扰设计

在智能电表研制的初期,我们发现这样一种现象,电表带上电感性负载(比如电扇)时,在电扇快速插拔的瞬间,容易导致智能电表中单片机数据的丢失或死机。如果从设计上不能把智能电表的抗干扰问题解决好,后果将会非常严重。

(1)电源的抗干扰措施

实践证明,系统失效和硬件损坏大都是由各种干扰引起的,而90%以上的干扰来自于电源。可见这种来自电源的干扰对系统的影响相当大,因此应充分考虑电源对单片机的影响。电源做得好坏,直接影响整个电路的抗干扰能力的好坏。目前有以下几种电源可供选择:第一种阻容分压式,它采用简单的电阻电容分压、滤波。但这种电源稳压性能差、电源波动大、带负载能力小、电网干扰极易串入,一般不采用这种方式。第二种开关电源,这种电源稳压性能好、纹波小,但成本较高且对外界电网干扰比较严重,也不宜采用。第三种线性电源,这种电源由220V经交流变压、整流、滤波及稳压得到,稳压性能好、隔离特性好,价格适中,在目前应用广泛的多用户电表设计中大都采用这种方式。对这种电源的抗干扰措施有以下几个方面。

1. 对于电源变压器的设计,要使其空载电流尽可能小,以降低整表功耗。增加变压器的容量,能使干扰脉冲的数量和幅度有所减少,而变压器的容量受电表空间的限制,变压器又不能太大。

2. 在电源变压器的初级串联一个电源滤波器,比如采用“双绕组扼流圈”的滤波线路,它对高频干扰信号阻抗很大,使整个电子系统与供电网之间得到一定程度的高频隔离,对于外界空间电磁场的干扰,也起一定的抑制作用。

3. 在各相交流电源的进线端,并联一个压敏电阻(MOV),其电阻随电压的增加而减小。在过压时形成一个低阻的分流器,从而可以防止被保护电路两端的电压进一步上升;当浪涌电压过后,电路电压恢复到正常工作电压,压敏电阻又恢复到高阻状态。

4. 在为主处理器提供电源之前的三端稳压器前,并接一个瞬变电压抑制二极管(TVS),对后面的电路起到保护作用。当TVS两端经受瞬间高能量冲击时,它能以极高的速度成为低阻抗器件,吸收大电流,从而把它两端的电压钳位在一个预定的数值上,保护后面的电路元件不因瞬态高电压的冲击而损坏。

5. 在变压器一次侧采取磁珠和电容组成的丌型滤波方法,对高频干扰起作用,但对几百赫兹以内的低频干扰作用却很小。综上所述,设计人员应根据具体的工作环境,选择不同的抗干扰措施。

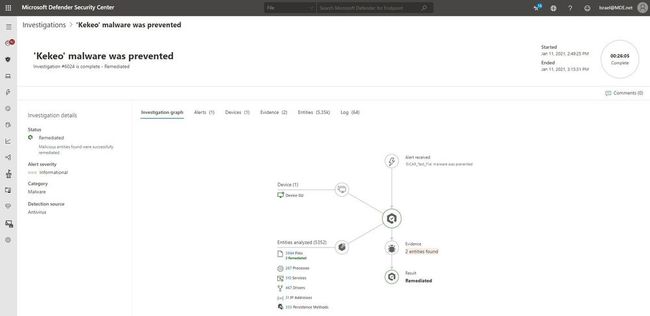

(2)电源检测及看门狗电路

分析及实践表明,对来自电网的干扰不仅要采取硬堵的办法,还要采取容错措施。使用电源检测及看门狗电路的目的,就是当电源电压出现干扰脉冲或单片机受干扰程序运行异常时,产生一复位信号使单片机复位。看门狗电路实质上是一个单稳电路。当程序运行正常时,单片机定时给单稳电路输入触发信号,使单片机输出保持暂稳态:当干扰异常时,单片机不能给触发信号,单稳输出回到稳态引起单片机硬件夏位:看门狗不仅对来自电网方面的干扰起作用,而且对来自空间等其他方面的干扰也起作用。然而如果没有电源检测电路,只有看门狗电路,在电网干扰下,即使不带电感性负载,当电源快速合闸时,也有可能导致死机。实践证明,采用电源检测及看门狗电路之后,死机观象得到了有效地克服。

(3)串行E2PROM的选择

因为电表数据存储的可靠性至关重要,为了保证在掉电时以及在因干扰导致单片机复位时,智能电表中的主要数据和参数不丢夫,存储器的选择上要有所考虑。使用并行存储器.虽然有速度快的特点,但读写信号容易受到干扰从而造成错误。而采用串行E2PROM存储器时,其读写时序相当严格,受到干扰出错的几率就小得多。

(4)布线布局上的抗干扰设计

在用电负荷很小时,220V的电压与几个μV的小信号会共集于一块电路板上,如果电源布局不当,有用信号会被噪声所淹没,以多用户电表为例,在布线布局上的抗干扰措施有:

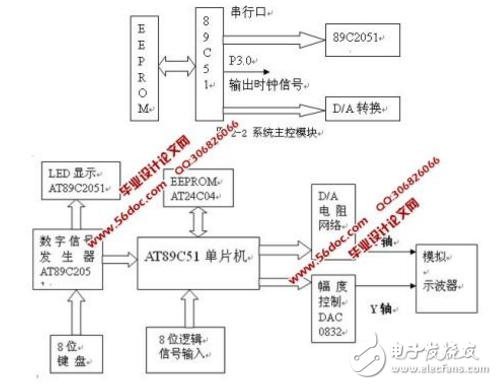

1. 电源与控制分两块板。在多用户智能电表中分三部分:电源板,主机控制板和电能采集传感器板。电源板包括变压器、整流、滤波、稳压等。控制板包括微处理器、显示驱动、看门狗电路、串行E2PROM、电能脉冲采集等。电能采集传感器板包括A、B、C三相上各用户的电能采集模块及其外围电路。对变压器的设计要求其漏磁要小,一般其空载电流不大于10mA,若仍不能满足要求,可变换变压器位置改变磁场方向,减小漏磁对小信号的影响。

2. 印刷电路板应有良好的绝缘性,绝缘电阻大于1011ΩV。在电路设计中,必须严格保证强电与弱电的隔离,除了电路有直接连接外,100V以上的强电印刷布线与弱电印刷布线距离应大于4—5mm。数字地与模拟地应通过一点方式连接来提高抗干扰性能。

3. 在每个印刷电路扳入口处的电源线与地线之间并接退耦电容。并接的电容应为一个大容量的电解电容(10~100μF)和一个0.01~0.1μF的非电解电窖,电路板上的大中规模IC要并接一个0.0lμF一0.1μF高频电容,以减小IC对电源的影响。注意高频电容的布线,连线应靠近电源端并尽量粗短,否则,等于增大了电容的等效串联电阻,会影响滤波效果。

4. 印刷线走线要科学,高压走线尽量短,尽量远离小信号走线。对于电能采集传感器板的印刷板布线要求一面走线.另一面铜铂既作电磁屏蔽用、又作地线用,以减少干扰信号。除了要根据电流大小,尽量加大导线宽度外,采取使电源线、地线走向与数据信息传送方向一致,将有助于增强抗噪声的能力。布线时避免小于90度折线,减少高频噪声发射。不要在印制板上留下空白铜箔层,因为它们可以充当发射天线或接收天线,因此可将它们接地以减小电磁干扰。

5. 在线路无法排列或只有绕大圈才能走通的情况下,干脆用绝缘“飞线”连接,而不用印刷线,或采用双面印刷“飞线”或阻容元件直接跨接。

6. 对印刷板上容易受干扰的信号线,不能与产生干扰或传递干扰的线路长距离平行铺设。必要时可在它们之间设置一根地线,以实现屏蔽。

当然,这些布线与布局的抗干扰设计一般不能由自动布线软件来实现,必须有设计者亲自参与并设计有关电路。

三、软件抗干扰设计

在提高硬件系统抗干扰能力的同时,软件抗干扰以其设计灵活、节省硬件资源、可靠性好越来越受到重视。因此,除了采取硬件抗干扰方法外,还要采取如下软件抗干扰措施。

(1)指令冗余技术

当指针受到干扰出现程序跑飞时,可能会出现将操作数数值改变及将操作数误当作操作码的情况。当“跑飞”到某双字节或三字节指令的操作数上时,会将操作数当作操作码,程序将出错,因此可在双字节和三字节指令之后插入两个或三个单字节NOP指令,这可保证其后的指令不被拆散。对程序流向起决定作用的指令(如浸水使柔软、RETI、ACALL、LCALL、LJMP、JZ、JNZ、JC、.INC等)和对系统工作状态起重要作用的指令(如SETB、EA等)之前插入两条NOP指令,可保证跑飞程序迅速纳入轨道;或者在其后面重复写上这些指令,以确保这些指令的正确运行。

(2)软件陷阱

当微处理器受到各种干扰时,若PC指针跳到非程序区,可能会陷入某种循环不能跳出。如果循环中无清WDT指令,在给定看门狗定时器条件下,经过一定时间 WDT起作用,将PC指针复位,工作恢复正常。如果循环中包含了清WDT的指令,则产生死机。对于后者可在非程序区放置软件陷阱加以解决。

软件陷阱有三条指令组成:

* LJMP EER

安排软件陷阱的位置有:

1. 未使用的中断区。如果设计的智能电表未使用全部的中断向量区,则可在剩余的中断区安排软件陷阱,以便能捕捉到错误的中断。

2. 未使用的大片EPROM空间。对于单片机未编程的空间,其初始值为OFFH。OFFH对51指令来说,相当于单字节指令MOV R7,A。当程序跑飞入该区后,不仅无法迅速入轨,而且破坏R7的内容。因此在该区每隔一段地址设一个陷阱,就一定能捕捉到跑飞的程序。

3. 在表格的最后安排陷阱。注意表格中不应被放入。

4. 在程序区。前面曾指出,跑飞的程序在用户程序内部跳转时可用指令冗余加以解决,也可以设置一些软件陷阱,能更有效地抑制程序跑飞。可以将陷阱指令放置在各模块之间的空余单元里。在正常运行中不执行这些陷阱指令,一旦程序跑飞落入这些陷阱区,马上将乱飞的程序拉入正确轨道。由于软件陷阱都安排在正常程序执行不到的地方,故不会影响程序的执行效率。所以在EPROM容量允许的条件下,这种陷阱多一点为好。

(3)“看门狗”措施

如果跑飞的程序落入一个临时构成的死循环中时,冗余指令和软件陷阱都将无能为力,这时可以采用复位的方法使系统恢复正常。“看门狗”电路的功能就是对 CPU进行实时检测,当CPU落入死循环之后,能及时发现并使整个系统复位。在软件编程中,设置约1秒访问一次看门狗芯片,当程序跑飞或大于1.4秒(设置的超时时间)没有访问看门狗芯片,X5045将输出复位脉冲,直至程序正常运行。

(4)保证EEPROM数据写入的可靠性措施

需要注意的是,看门狗如果起作用说明程序计数器内容被破坏,因此其它寄存器或片内公羊的内容也有被破坏的可能,会导致把错误的数据写入EEPROM。在电表工作中,每产电量改变0.1度写入一次EEPROM,如果出现将错误的数据写入EEPROM,这是不允许的。采取以下措施可很好的解决此问题:

1. 正常写入EEPROM之前,要进行一系列操作,可将其分成几部分。每一部分设置一写入口令。只有程序正常一步一步运行,口令才会逐一被赋予正确的值,到最后写入时再判断所有的口令是否正确。若正确,写入,否则退出。写入完成,口令清除。

2. 数据双备份。当由于干扰使微处理器中的寄存器数据改变时,鉴于三组数据在同一值出错的概率较小,故在写入之前,将三组数据比较,若相等则写入,若不相等则将相等的两组数据写入。

3. 写入之前对数据的合法性进行判别,即对电量或参数的数据格式进行判别。有了这样的限制,可进一步提高可靠性。

4. 定时设置I/0口状态;微处理器受到干扰,I/0口状态可能改变,比如电脉冲输入口若改变为输出态,会造成用户用了电但微处理器却检测不到的可能。所以周期性地重复定义I/0口的输入/输出状态对于干扰环境下运行的电表是有好处的。

(5)串行通信数据的冗余校验

在抄表通信过程中,由于信道上各种因素的影响,所传输的信号受一定程度的干扰,PC机、集中器、电表间的性能参数不完全一致,在串行通信中仅靠奇偶校验是不够的。而采用国际上较为流行的传输码校验方法——循环冗余码校验(CRC),可收到了很好的效果。CRC是一种多用于同步通讯方式中的差错检出方式,在该方式中,将所传数据系列看成高次多项式G(x),将此多项式用预先规定的生成多项式P(x)去除,再将其余数码BCC附加在所传数据的尾部一并传送:在接收方,用同样的生成多项式去除,若除得结果为零,则可判断所接收到的数据是正确的。在发送端的一方,即电表先将发送数据转换,连同原数据一同发给集中器,集中器不做校验,直接发给PC机,在接收端,PC机用高级语言实行CRC算法解码;以确定数据的真伪。经实验证明,冗余校验使误码率大为降低,确保了数据传输的可靠性。

另外在软件的编制过程中应注意在执行各功能子模块之前,可先进行功能标志冗余判断,以增强其程序运行可靠性。

四、结束语

在电表设计中,为了少走弯路和节省时间,应充分考虑抗干扰性能的要求,避免在设计完成后再去进行抗干扰的补救措施。因此电表设计开发者应从抑制干扰源,切断干扰传播路径,提高敏感器件的抗干扰性能等方面采取各种措施来提高系统性能。在抗干扰设计中,软件抗干扰是被动措施,而硬件抗干扰是主动措施,只要认真分析系统所处环境的干扰以及传播途径,采用两者相结合的方法,就能保证系统长期稳定可靠地运行。

-

微控制器

+关注

关注

48文章

7672浏览量

152307 -

电源

+关注

关注

185文章

17882浏览量

252295 -

滤波器

+关注

关注

161文章

7892浏览量

179204 -

智能电表

+关注

关注

25文章

944浏览量

109473

发布评论请先 登录

相关推荐

STM32的调试方式、更新程序、仿真以及补救措施

PCB电路抗干扰的三个基本要素

单片机电路干扰的因素与防治措施有哪些

数字电路抗干扰设计

PCB设计有哪些干扰因素以及如何抗干扰

PCB电路抑制干扰源的常用措施介绍

如何实现PCB电路抗干扰性的设计

边缘计算的风险及其补救措施

单片机抗干扰问题

智能电表硬件与布局上的抗干扰补救措施介绍

智能电表硬件与布局上的抗干扰补救措施介绍

评论