引言

在安检机系统中,安检机的主设备与控制台的双向通信具有非对称性,由主设备X射线端采样得到的大量数据通过高速通道传送至PC控制台进行处理。然而由控制台传送给安检机的控制信号,因数据量较小,仅需低速通道进行传输即可,并且在安检主设备端对于高速数据的处理是基于FPGA平台实现的,若同时采用单片FPGA对接收控制信号进行处理,一方面可减少硬件电路的设计负担,另一方面也降低了设备成本。但与此同时,若该系统采用传统串行通信方式,则在处理高速数据的FPGA电路单元中引入低速时钟线,不仅容易受到电路板上高频信号的影响,而且由于控制台距离CT机距离较长,不利于时钟信号的传输。因此,对于安检机控制信号的传输一般采用单路串行低速通信方式。对于这种传输方式,在FPGA上采用一种高效的数字时钟提取技术就十分必要。

1 数字时钟提取环路基本原理

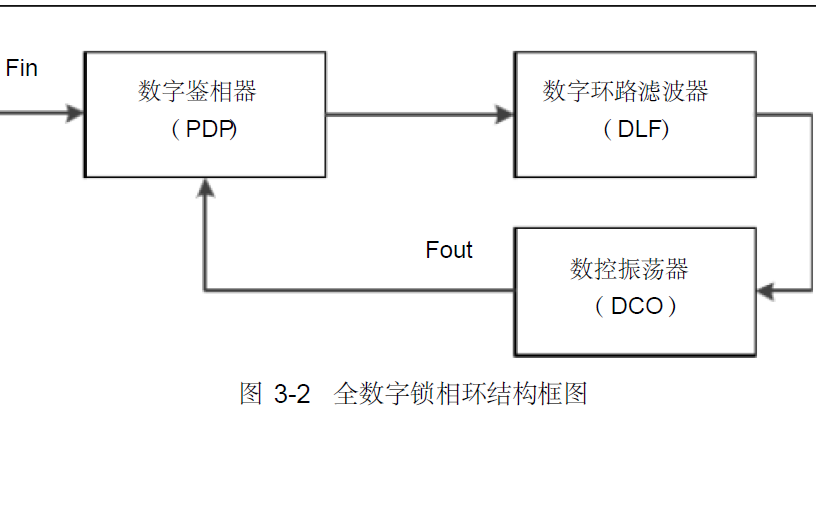

数字锁相环能让本地产生的时钟信号自动跟踪输入信号相位,从而实现一个闭环自动控制系统。数字锁相环的基本结构是由数字鉴相器(DPD)、数字环路滤波器(DLF)、数字可控振荡器(DCO)和本地时钟源(LC)组成的一个反馈环路,其具体原理框图如图1所示。

基于数字锁相环的数据时钟提取系统工作原理如下:本地产生一个高频率的时钟,数字鉴相器通过输入信号与估算时钟进行鉴相比较,输出鉴相信息。之后由数字环路滤波器根据鉴相信息对相位误差进行平滑运算,输出数控振荡器控制信号,通过对本地估算时钟的相位调整,最终跟踪到输入数据的位同步时钟。

2 各模块功能及实现原理

2.1 数字鉴相器

数字鉴相器用于获取输入信号与本地估算时钟的相位比较信息,常用异或门实现。在数字鉴相器中,首先将输入信号的正向过零脉冲与本地估算信号的正向过零脉冲进行比较,从中得到一个表明相位提前或延后误差的脉冲输出,其宽度反映超前(滞后)相位的多少。当本地估算信号超前于输入信号时,其输出为超前脉冲,反之,则为滞后脉冲。综合考虑到安检系统中的控制信号属于数字信号,并且由于FPGA的资源主要用于完成采集数据的处理,应尽量减少对FPGA资源的使用。本文的方案采用了超前/滞后数字鉴相器。

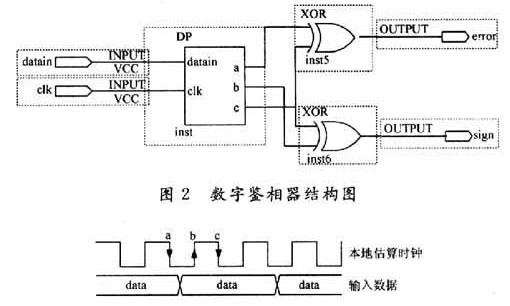

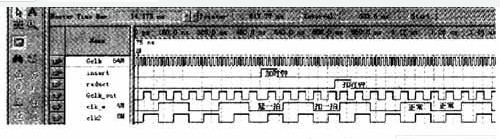

超前/滞后数字鉴相器硬件实现有两种方式,分为积分型结构与微分型结构。积分型结构的硬件实现比较复杂,但具有良好的抗干扰性能;微分型结构则具有相反特性。为了优化系统性能,选择使用微分型结构。尽管微分型结构的抗干扰能力较弱,但是结合安检机系统的实际环境,该结构可以满足系统需要。图2为微分型超前/滞后数字鉴相器的结构原理图,图3为其时序图。

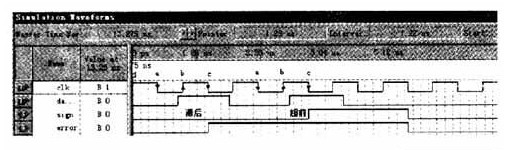

通过时序图可以看到,输入数据datain在本地估算时钟的边沿(包含上升沿和下降沿)触发下,依次存入寄存器a,b,c中。在时钟下降沿的触发下,通过对a,c信号进行异或运算,生成error信号,作为误差跳变绝对值输出。通过对b,c信号进行异或运算,生成sign信号,作为超前/滞后标志位输出。具体仿真结果如图4所示。

从图4可以发现,对于error信号,若前一位数据存在跳变,则输出高电平,否则输出低电平。对于sign信号,当估算时钟超前时,输出高电平,滞后时,输出低电平。该模块输出的两路信号将作为环路滤波器的输入信号,对下级结构进行控制。

2.2 数字环路滤波器

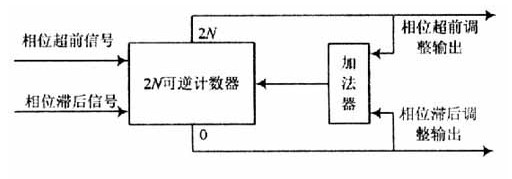

数字环路滤波器在锁相环路系统中主要起两种作用:其一,输出超前调整信号及滞后调整信号,以控制数控振荡器模块,对估计时钟进行相位调整;其二,有数字滤波作用,对噪声信号及高频干扰信号起到较好的抑制作用。数字环路滤波器内部拥有容量为2N的计数器,能够有效消除随机出现的具有正态分布特性的噪声信号。容量2N值越大,对噪声抑制效果越好,但同时2N值越大,跟踪速度越慢,实时捕捉能力下降。所以设计时,2N值的选取要综合考虑安检系统的实际参数要求。出于减少占用FPGA系统资源的考虑,该系统采用随即徘徊滤波器作为实现方案。该滤波器原理框图如图5所示。

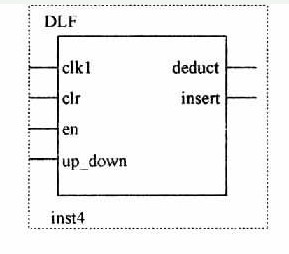

在实现方案中,环路滤波器通过加减计数逻辑单元实现。通过读取鉴相单元输出的两路使能信号对计数器进行代数累加或累减操作,当达到记数的边界值0或2N时在输出端送出insert(插入时钟周期)或deduct(扣除时钟周期),与此同时,计数器内部寄存器值从2N自动恢复到N,重新开始。

该模块如图6所示,其中clkl是记数时钟,由数控振荡器模块内部分频得到;clr是启动清零控制端;en接前端模块的error信号,该引脚是对记数功能的使能,即在输入数据(Data_in)有跳变时,才能判断相位误差;up_down是加减记数输入,与上级模块的sign使能信号相连,当sign=1时,做累加操作,当sign=0时,做累减操作,直到代数累加/累减运算到0或2N时,再对累加/累减计数器进行恢复。

在安检机控制信号中,考虑到随机噪声引起的相位误差输出长时间地保持在同一极性,误差很小,在该模块中会被有效抵消,而不会传到后级模块,从而可达到抑制噪声的目的。与此同时,根据安检机系统参数的要求,取N=512,当处于累加计算时,计算上限为1 023;当处于累减计算时,计算下限是O。

2.3 数控振荡器

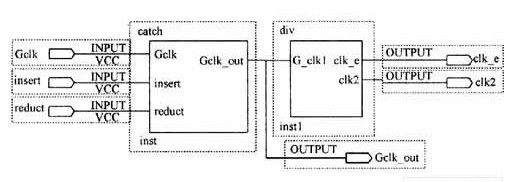

数控振荡器的主要功能是根据前级环路滤波器模块输出的insert和deduct:控制信号,生成本地估算时钟clk_e,该时钟即为数字锁相环(DPLL)最终提取到的数据时钟。此外,在本设计中,数控振荡器整合了本地时钟模块的功能,同时产生了用于整个系统的各路时钟信号,从而使系统各个模块能够协调工作,保证了系统运行的稳定性和可靠性。数控振荡器模块分为两个基本模块,即catch和div模块。具体结构图如图7所示。

catch模块的功能如下:

在本系统中,FPGA上用于驱动高速采样数据发送的主时钟为64 MHz,因此本设计中的全局时钟Gclk频率为64 MHz,这样可以有效节约FPGA上的硬件PLL资源,提高了硬件使用效率。

在catch模块内部,首先对全局时钟Gclk进行4分频,由于Gclk的设计频率为64 MHz,实现4分频后达到16 MHz。之后,catch模块根据前端环路滤波器的输出信号insert和reduct,在分频后的16 MHz时钟推动下,若insert信号出现高脉冲,自动在4分频后的时钟上补充一个Gclk时钟周期的延时,该操作仅对insert信号的高脉冲上升沿有效;相类似,若reduct信号出现高脉冲,自动在4分频后的时钟上扣除一个Gclk时钟周期。

div模块的功能如下:

该模块为catch单元的后级,其主要功能是根据catch给出的Gelk_out信号进行N分频。在本系统中,需要恢复频率为4 MHz的数据时钟,因此这里第一个分频系数N=4,输出为1*=4 MHz的时钟信号(clk_e),第二个分频时钟为数字环路滤波器的记数时钟,该信号是经过2分频(频率为8 MHz)后的时钟信号,用于进行DLF滤波。与此同时,也可以加速该时钟,这样可以缩短捕捉时间,并且扩展其捕捉带宽。该数控振荡器的加扣时钟和分频的综合仿真时序图如图8所示。

从该时序图可以看到,在insert与reduct信号的控制下,模块内部进行加/减时钟操作,最终在输出时钟信号中得到延时或者扣除节拍的捕捉效果。

3 本系统整体时序仿真结果

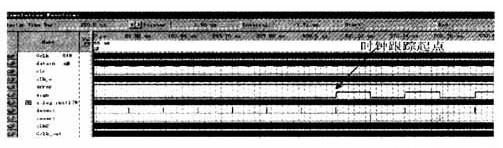

结合安检机控制信号的实际传输情况,确定设计要求,对整体系统进行时序仿真。其中,选定Gclk频率为64 MHz,数据速率为4 Mb/s,并设定初始状态中,估计时钟和数据的相位差为103.775 ns,显示结果为相位滞后。根据数字锁相环的基本原理,必须进行扣脉冲的操作后才能最终提取到同步时钟。鉴于该系统需要的捕获精度较高,因此捕获时间较长,并且由于整个仿真界面有限,只能观察到时钟提取过程,具体如图9所示。

由图9可以看出,从箭头处开始,出现了扣脉冲和加脉冲循环出现的情况,对于该情况分析如下:

由于初始设定的估计时钟相位滞后为103.775 ns,从图9仿真结果可以看出,在经历了7次扣脉运算后,由于每次扣脉冲的时间是1/(64×106)=15.225 ns,那么7个扣脉冲的时间就是15.225 ns×7=106.575 ns。在7个时钟扣除以后,相位又超前了106.575-103.775=2.8 ns,因此后续的操作必须加脉冲,从而实现相位捕捉。因为每加一个脉冲是15.225 ns,之后会再次出现相位滞后,又进行扣脉冲操作。如此循环,直到最终接近极限,提取到稳定的时钟信号。

4 FPGA硬件测试

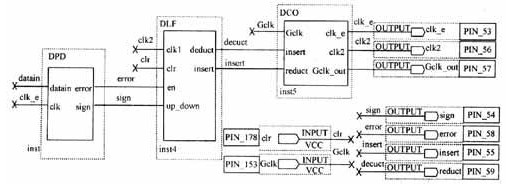

鉴于该系统应用于安检机控制信号传输系统中,故将该设计通过FPGA硬件平台进行了验证。该验证平台基于Altera公司Cyclone系列的EPlCl2Q240C8型号的FPGA芯片。鉴于实际系统中FPGA的本地系统时钟为32.768 MHz,故测试输入数据(datain)的速率为4.096 MHz。基于FPGA开发软件Quartus实现的测试系统整体结构图如图10所示。

Signal TapⅡ逻辑分析器是Quartus软件中集成的一个内部逻辑分析软件,使用它可以观察设计的内部信号变化,为FPGA设计的调试、开发带来极大的方便,实用性很高。以下各图为Quartus软件中SignalTapⅡ实时观察到的数据。

相位调整验证如图11所示。由图11可以发现,开始时钟的相位滞后于数据相位。因此经过调整,通过数字环路滤波器输出的reduct信号控制数控振荡器模块进行扣时钟操作,最终使本地估算时钟与数据时钟同步,正确地调整了相位。

当该系统捕获到数据时钟后,就会稳定输出与数据信号同相的时钟信号,稳定状态截图如图12所示。

利用FPGA开发平台所具有的Signal TapⅡ功能,成功地在硬件平台上验证了该系统的可行性与稳定性。

5 结语

目前,鉴于国际国内形势的发展,安检机系统得到了越来越广泛的应用,安检机中通信系统的发展也逐渐趋向高速化、高效化。对于采样数据量的增大,就要求有一条高速传输通道,同时,控制台低速控制信号的传输也要求有高效链路的构建。本文设计了一个高效时钟提取方案,并在FPGA上完成了验证。实验结果表明,基于锁相环的实现方案不仅提高了时钟提取的精度,而且平衡了捕捉时间,为安检机系统低速控制信令的传输提供了基本的技术支持,并且使控制信号的传输仅需要一条数据线就可以完全实现,保证了安检机控制信号链路传输的高效性,降低了设备成本,加快了开发速度,提高了整体系统的运行效率。

:

-

FPGA

+关注

关注

1664文章

22513浏览量

639651 -

滤波器

+关注

关注

162文章

8481浏览量

186388 -

振荡器

+关注

关注

28文章

4195浏览量

143213

发布评论请先 登录

基于数字锁相环实现X光安检机控制信号时钟提取系统的设计

基于数字锁相环实现X光安检机控制信号时钟提取系统的设计

评论