引言

数据采集设备是测试系统中不可缺少的一部分,数据采集需要针对不同类型的需求,需要有高速A/D、低速A/D、数字多用表等功能,传统数据采集设备是用一种仪器进行一类测试,通过多种仪器组合实现一组完整测试,这种由多种仪器堆叠起来的数据采集系统具有体积和重量较大、成本较高、维护困难等诸多问题。针对这些问题,为完成某系列型号装备自动测试任务,设计实现了一种高集成度数据采集设备。该设备需实现100 M高速A/D、双通道隔离A/D、6通道低速A/D和数字多用表功能,采集数据通过LAN传输给上位机。输入前端调理电路支持宽范围多种信号输入,并采用超宽输入范围的保护电路,实现设备通用性的同时保证其安全可靠。本设计采用DSP+FPGA架构,利用DSP/BIOS实时操作系统,结合TI提供的NDK 网络开发工具包,选用高集成度芯片,在10 cm×18 cm面积上设计实现该数据采集系统。

1 总体设计

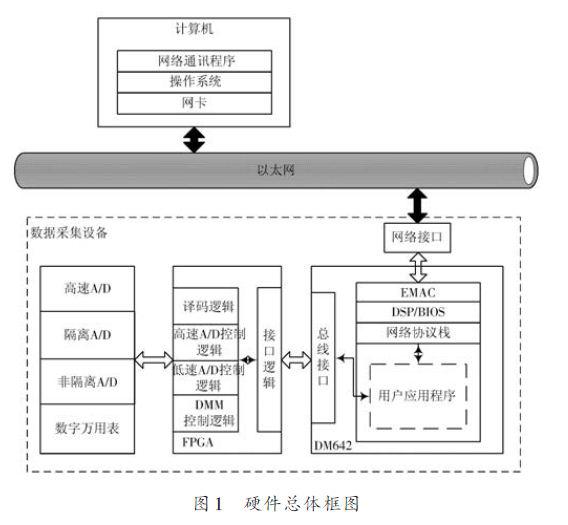

设备的总体结构如图1所示。设备能够接入到以太网中,并能够被计算机远程访问。

计算机中网络通讯程序控制设备进行数据采集并读取数据。整个设备以DSP+FPGA核心,包含高速A/D、低速隔离A/D、低速非隔离A/D和数字多用表。DSP选用TI公司主频720 MHz、32 b定点高性能的TMS320DM642,DM642完成了网络、主控功能。利用DM642的自带的网络功能接口,结合TI提供的网络功能开发包(NDK)实现网络通讯功能。采用DSP/BIOS实现分配调度线程、数据采集任务和网络控制传输任务,实现对数据采集、存储和网络通讯的控制。FPGA选用Altera公司的CycloneⅢ系列低成本工业级的EP3C55F484I8,编写接口逻辑实现与DM642的数据交互,编写译码逻辑、高速A/D控制逻辑、低速A/D控制逻辑、数字多用表控制逻辑实现数据采集功能。

2 硬件设计

2.1 网络接口设计

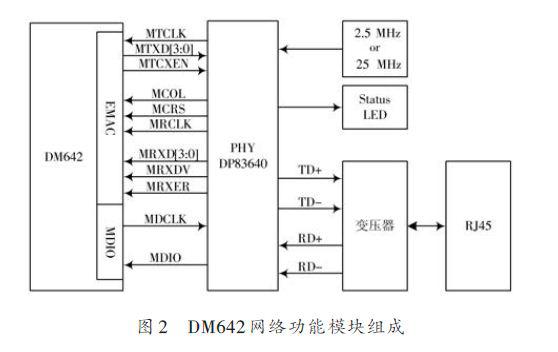

TMS320DM642 自带一个网络功能接口,由EMAC控制模块、EMAC 模块和MDIO 模块组成[4],符合IEEE802.3协议,在设计网络通讯接口时只需要外接一片网络收发芯片即可,DM642的网络功能模块如图2所示。

网络收发芯片选用美国国家半导体公司推出的DP83640,其MII接口与DM642 的EMAC 接口直连,MII接口包括接收总线和发送总线,接收部分包括接收数据线RXD[30],接收错误标志RX_ER,接收数据有效标志RX_DV 和数据同步接收时钟信号RX_CLK,当工作在10 Mb/s 时,RX_CLK 为2.5 MHz,工作在100 Mb/s 时,RX_CLK 为25 MHz.发送部分包含发送数据线TXD[30],发送使能位TX_EN,和发送时钟TX_CLK,同样,时钟可以为2.5 MHz或者25 MHz.另外,MII接口带有冲突检测信号COL,用于检测在半双工模式下发送和接收同时发生的情况。该芯片具有的IEEE1588功能方便日后设备升级时钟同步功能。

2.2 A/D采集模块设计

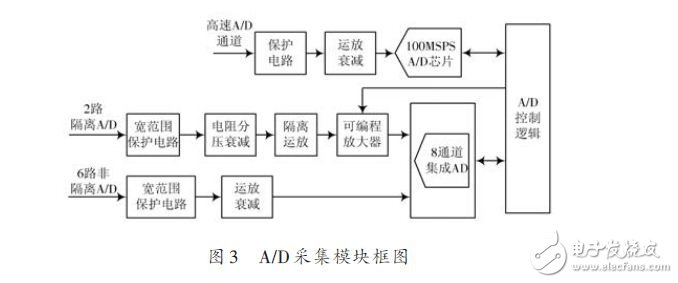

A/D 采集单元分为1 路高速采集和8 路低速采集两部分,其中低速采集部分,分为2路隔离通道和6路非隔离通道,总图框图如图3 所示。高速采集通道选用14 位的A/D6645,最高采样率105 MSPS,并行输出。低速采集通道选用24位的A/DS1278,单片并行8通道,最高采样率144 KSPS,采用8 路串行输出,同时采集8 路输入信号。两路隔离通道选用A/D215隔离运放。

两路隔离通道输入电压范围±380 V,输入阻抗为10 MΩ,1 路高速通道和6 路非隔离通道前端均采用运放衰减,分别实现±5 V 和±40 V 电压输入范围,高输入阻抗和宽范围电压输入范围使该设备能够适应大部分被测系统,实现了设备的通用化。每通道前端采用压敏电阻和自恢复保险丝设计宽范围高可靠保护电路,保证设备的稳定性和安全性。

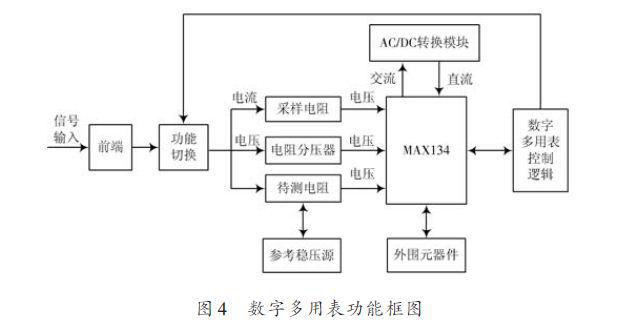

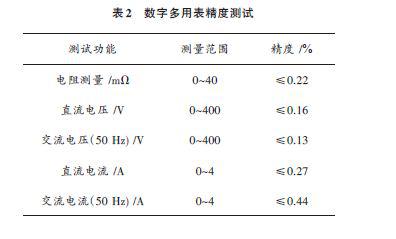

2.3 数字多用表模块设计

该设备对数字多用表测量速度、精度要求不是很高,但要求电路板的体积尽可能的小,因此在数字多用表电路设计上,选用了MAXIM 公司生产的MAX134 作为测量的核心芯片。MAX134 是单片智能数字多用表专用芯片,在其外围配置少量元器件,设计简单的电路即可实现精度达到3位半的数字多用表。该设备的数字多用表功能框图如图4所示。采用继电器实现功能切换;电阻分压器实现0~400 V交、直流电压输入;0.1 Ω和1 Ω采样电阻实现0~4 A交、直流电流转换为电压信号输入;AC/DC转换模块采用有效值转换芯片A/D637,实现交流信号转直流;参考稳压源提供电阻测试的参考电压,实现0~40 MΩ 电阻测量;外围元器件实现MAX134 正常工作所需的晶振、电源、滤波等功能。

FPGA 内部逻辑控制功能切换、实现MAX134内部寄存器的读写,进而实现数字多用表功能。

3 软件设计

3.1 网络通讯功能实现方法

本设计利用DSP/BIOS 结合NDK 实现网络通讯功能。DSP/BIOS 是TI 公司为C28x,C5000 和C6000 系列DSP开发的可剪裁实时多任务操作系统,同时也是CCS提供的一套多任务开发、硬件抽象、实时分析和系统配置的专用工具。DSP/BIOS以其功能丰富的APIs综合管理系统内存,实现任务分配和调度,实时监测分析系统运行,并提供方便的数据通信接口和外设驱动开发工具。NDK是TI专门为网络应用开发提供的网络开发工具包,利用其TCP/IP协议栈开发网络应用具有成本低、开发周期短的特点。网络性能由套接字类型、套接字缓冲区、CPU速度和CPU缓冲等几方面决定。要使用NDK 必须在DSP/BIOS 中配置TCP/IP 协议栈,主要在DSP/BIOS的。cdb文件中做以下配置:

(1)全局设置GBL

设置系统初始化函数dm642_init,用于设置L2 模式,分配MAC地址;

(2)设置MEM对象

配置程序、数据存储区域及堆栈大小;

(3)设置HOOK对象

设置NDK的TCP/IP协议栈保存空间;

(4)设置PRD对象

设置NDK HAL库中的定时驱动事件;

(5)设置线程TSK

静态创建2个线程:TSK_idle线程,优先级最低,当系统没有其他任务执行时运行;TSK_main主线程,优先级最高,用于配置服务器信息及启动HTTP服务。

配置文件生成之后,在DSP/BIOS 中编写网络主线程TSK_main,用于启动运行TCP/IP 协议栈,启动HTTP服务,同时不断监测和响应网络底层事件。在主线程中可以动态创建任务,用于实现与其他网络设备的网络通讯功能。

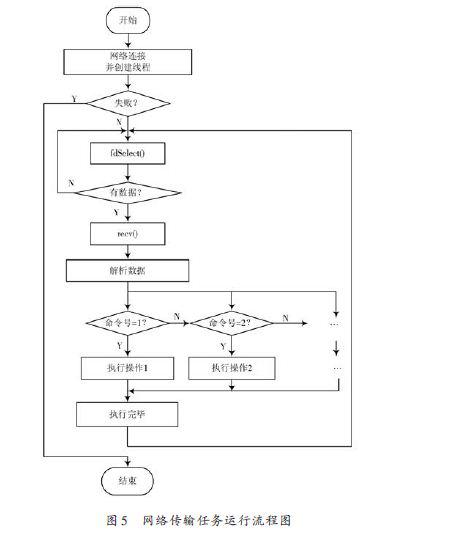

3.2 多任务线程管理机制

为了优化CPU资源,实现各功能的协调运作,需要合理划分功能、规划任务。本设计构建了按优先级从高到低创建了高速A/D 线程、低速A/D 线程、数字多用表线程、网络传输线程和网络配置线程。其中,网络传输任务是最核心的任务线程,主要完成创建线程、网络命令解析、通道查询和数据上传的功能,流程图如5所示。

网络传输任务使用套接字编程,工作在服务器模式,通讯方式采用TCP.首先调用fdOpenSession()函数建立文件描述表,调用socket()创建套接字,然后绑定IP信息、监听,然后等待客户端连接请求,一旦客户端连接上,便调用fdSelect()函数检测客户端是否发送数据,如果有数据则接收,否则继续检测,除非客户端断开连接。在这种设计模式下,允许客户端重复的执行断开、连接操作,保证了系统工作的稳定性。

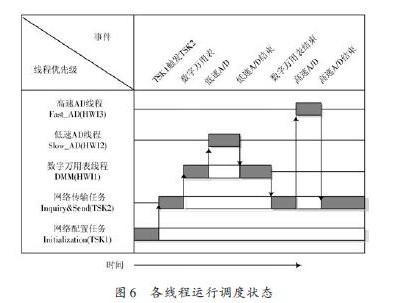

DSP/BIOS 支持硬件中断(HWI)、软件中断(SWI)、任务(TSK)和空闲线程(IDL)4种类型的线程,它们的线程优先级从高到低。硬件中断线程主要用来处理响应时间要求严格的请求,同时它的优先级最高,能抢占当前运行的其他线程及时运行,本设计各线程运行调度状态如图6所示。

图中黑色阴影部分表示线程运行,白色不封表象线程挂起。高速A/D处理的数据量最大,对处理响应的时间要求严格,故将它的优先级设为最高,能抢占当前运行的其他线程及时运行,保证数据实时上传,低速A/D线程和数字多用表线程的优先级根据其对时间的要求逐次降低。

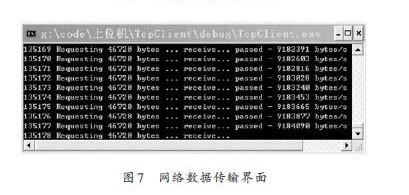

4 测试

为了测试接口板的网络通讯功能,使用PC 机作为客户端,与设备通过路由器连在局域网内。设备作为服务器端,在PC机端采用VS2005编写上位机网络通讯程序,每次传输46 720 B数据,在开始和结束数据传输时刻读取系统时间,并计算出网络传输的速率,如图7所示。

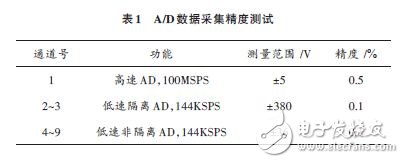

DM642中L2的Cache大小会影响网络传输速度,实验发现,当Cache大小在128 KB是,传输速率达到了最佳,为89.2 Mb/s,由于在局域网中网络环境相对复杂等原因,没有达到理想的100 Mb/s的传输速率。A/D数据采集和数字多用表功能的测试,利用Agilent E3631A直流电源、Agilent 34110A6位半数字多用表和正泰TDGC2-0.2电源模块等仪器,测试结果如表1和表2所示。

5 结语

本设备选用高性能高集成芯片,采用DSP+FPGA的主控方案,实现了数据采集设备的小型化。前端调理电路支持多种信号的宽动态范围测量,并具有可靠的过压保护,保证了设备的通用性与安全性。以DM642 的硬件资源为基础,通过调用NDK提供的APIs,实现了百兆以太网的传输。同时,利用DSP/BIOS的多任务机制,实现网络控制、数据采集以及网络通讯的有效配合,保证底层高速采集的大数据量快速可靠得上传给上位机。

实际应用表明,该设备稳定可靠、实时性强、兼容多种被测系统,在数据采集领域中有一定的应用价值。

-

dsp

+关注

关注

561文章

8269浏览量

368144 -

FPGA

+关注

关注

1663文章

22493浏览量

638944 -

数据采集

+关注

关注

42文章

8300浏览量

121222

发布评论请先 登录

【PCB 设计】板载式电流传感器设计集成,适配电子设备小型化

基于FPGA的DAQ系统|实现高性能数据采集的挑战

小型化云台电机驱动板载集成技术研究与实现

Neway电机方案的小型化设计

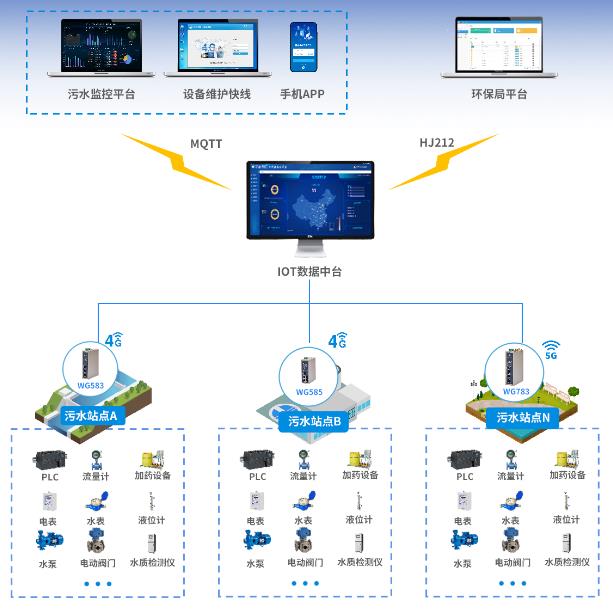

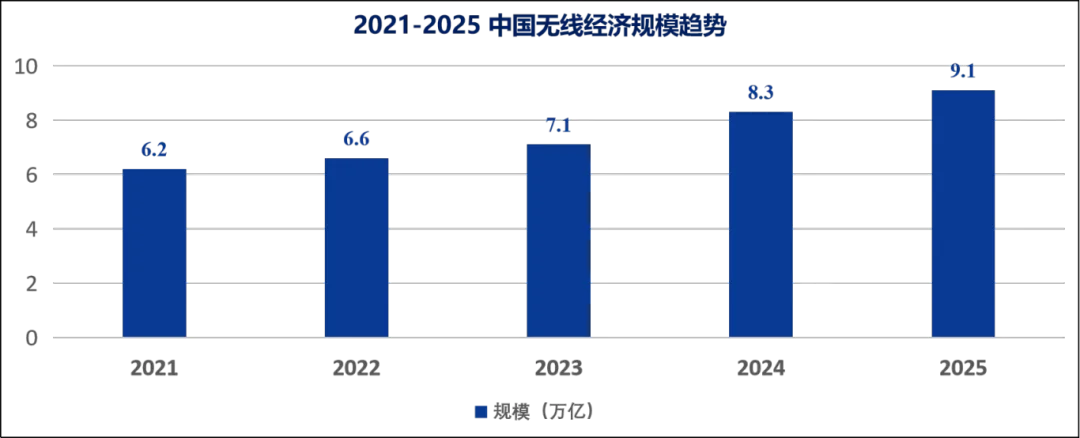

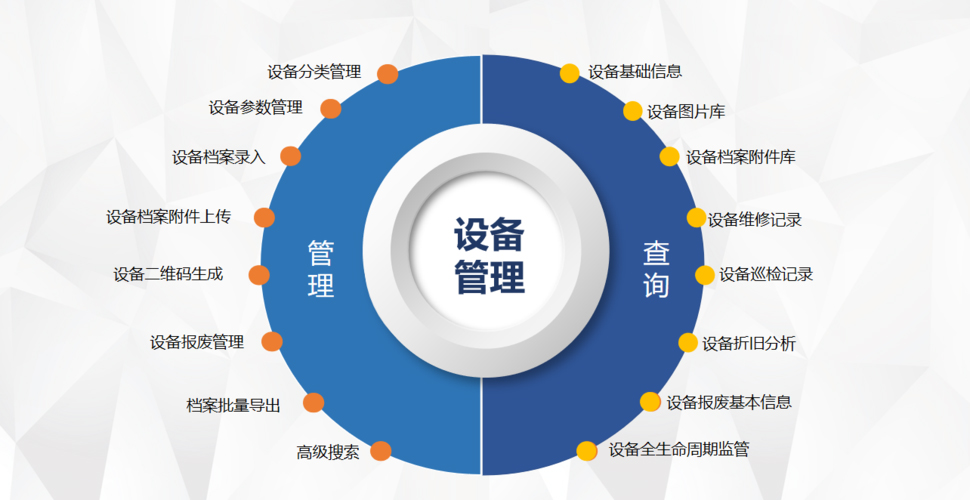

污水处理设备数据采集到组态云平台解决方案

基于DSP技与+FPGA器件实现数据采集设备的小型化

基于DSP技与+FPGA器件实现数据采集设备的小型化

评论