引 言

随着数字视频技术的发展,近年来世界上出现了许多数字音视频压缩标准。AVS(Audio Vicleo Coding Stand-ard)是我国自主制定,拥有自主知识产权的音视频编码标准。与世界其他知名音视频编码标准相比,它具有如下特点:①性能高,编码效率比MPEG2高2倍以上,与H.264的编码效率相当;②算法复杂度比H.264低;③软硬件实现成本都低于H.264;④专利授权模式简单,费用明显低于同类标准。在码率和PSNR相当的情况下,AVS的编码速度是H.264的4倍以上。

AVS视频标准采用了一系列技术来达到高效率的视频编码,包括帧内预测、帧间预测、变换和量化、熵编码等。帧问预测使用基于块的运动矢量消除图像闻的冗余;帧内预测使用空间预测模式消除图像内的冗余;再通过对预测残差进行变换和量化消除图像内的视觉冗余;最后,运动矢量、预测模式、量化参数和变换系数用熵编码进行压缩,以消除编码码字冗余。

DSP的实现是AVS硬件应用的一个重要领域,而实时性则是一个重要要求;但由于标准提出的时间短,所以DSP实现的实例很少,能将AV5算法在DSP上实现,对AVS的发展有很大的意义。另外,具有强大处理能力的DSP非常适合应用在通信和图像处理领域。

本系统选用TI公司最新推出的数字媒体处理器TMS320DM6446(简称“DM6446”),其主频高达594MHz,具有丰富的专为多媒体运算优化的指令集,包括可简化设计并能降低系统成本的集成多媒体与通信外设。片上集成的基于ARM9的ARM926EJ-S核(主频高达297 MHz),丰富的媒体、外设接口,为AVS视频编解码方案提供了很好的硬件基础。

1 系统硬件设计

本系统是基于DSP的视频监控系统,通过DSP对CCD摄像头获取的YUV 4:2:0信号进行实时处理,将压缩后的数据流通过以太网接口发送到监控室。

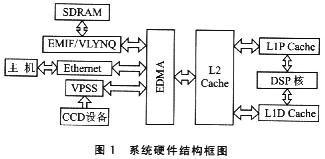

数据压缩单元主要由DSP和SDRAM实现。系统硬件结构框图如图l所示。

DM6446增加了很多外围设备及接口。例如:

◇视频处理子系统VPSS(Video Processing Subsystem),其中包含CCD设备接口;

◇扩展内存接口EMIF(External Memory Inter-faces);

◇FPGA接口(VLYNQ Interface);

◇以太网接口1O/100Mbps EMAC(Ethernet MAC)。

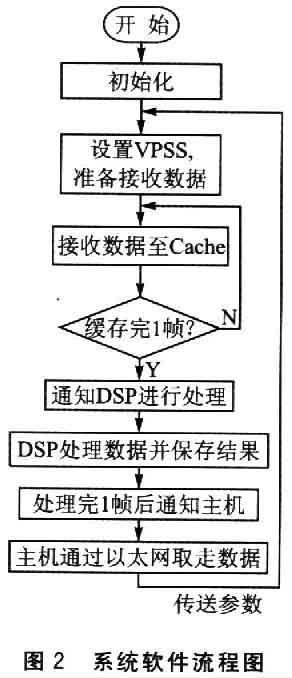

视频信号采集进来之后,采用EDMA方式进行数据搬移;搬移到缓存(cache)中后,DM6446便对数据进行压缩处理。图2为该系统的软件流程图。

缓存完l帧后,DSP便通过EDMA读取数据,并对数据进行压缩处理,结果通过EDMA存储在SDRAM中。当DSP处理完1帧之后,通知主机读取数据;主机接到通知后,通过以太网以EDMA形式将压缩数据读到主机内存中并保存在硬盘里。在监控主机上安装有AVS解码器客户端,还可以在主机上对传输的数据进行实时播放。上述过程循环执行。在执行过程中可以根据视频码率自动调节有关参数。

2 系统软件设计

2.1 AVS视频压缩原理

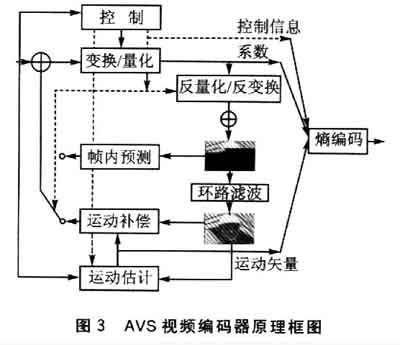

该系统采用AVS视频标准,原理框图如图3所示。

在AVS视频标准中,所有宏块都要进行帧内预测或帧间预测。预测残差需要进行8×8离散余弦变换(DCT)和量化,然后对量化系数进行扫描,得到一维排列的量化系数,最后对量化系数进行熵编码。AVS使用环路滤波器对重建图像滤波,优点在于:一方面可以消除方块效应.改善重建图像的主观质量;另一方面能够提高编码效率。滤波强度可以自适应调整。

2.2 AVS的主要技术

(1)变换和量化

考虑到编码性能、实现复杂度、AVS视频标准的主要应用等多方面因素,AVS视频标准最终选择了8×8离散余弦变换。在AVS中,采用带PIT(Pre-Scaled Integer Transform)的8x8整数余弦变换技术,即正向缩放、量化、反向缩放结合在一起,而解码端只进行反量化,不再需要反向缩放。AVS的8×8变换量化可在16位精度上无失配地实现。

对于PC机,一般将DCT中大量的乘加运算使用加法和移位来实现。但就本系统的TMS32013M6446而言,乘加可以通过合理安排流水线而在一个周期内完成,完全没有必要也不应该为了减少乘法而使用大量的加法和移位运算。而对于2的整次幂的乘法还是应使用移位来实现,因为移位运算比乘法运算的功耗要低。

(2)帧内预测

AVS视频标准使用帧内预测技术来提高帧内编码宏块的编码效率,预测时使用当前块的左边块和上边块中的相邻像素作为参考像素。AVS视频标准的帧内预测以8×8亮度块和色度块为单位,定义了5种8×8亮度块预测模式和4种8×8色度块预测模式(参见表1和图4),大大简化了帧内预测。

(3)帧间预测

AVS支持P帧和B帧两种帧间预测图像。P帧至多采用2个前向参考帧,可在不增加缓冲区大小的前提下提高编码效率;B帧采用前后各一个参考帧。

AVS视频标准中运动补偿块的大小包括16×16、16×8、8×16、8×8等。运动矢量的精度为1/4像素,为得到非整数样本,需要进行插值运算。AVS视频标准定义了2个4抽头FIR滤波器,分别用于l/2和1/4亮度样本的插值。与H.264使用的6抽头FIR滤波器相比,AVS视频标准的滤波器实现复杂度较低。

(4)环路滤波

基于块的视频编码很容易造成方块效应,特别是在低码率的情况下。AVS视频标准定义了自适应环路滤波器来消除方块效应,改善重建图像的主观质量,同时可提高编码效率。环路滤波是对亮度块和色度块的边界进行的。滤波时首先对块的水平边界滤波,然后再对块的垂直边界滤波。滤波强度由宏块编码模式、量化参数和运动矢量等决定。H.264的环路滤波器滤波时使用边界左右各4个像素,而AVS视频标准只使用左右各3个像素,实现复杂度低于H.264的环路滤波器。AVS视频标准使用的环路滤波器也更有利于DSP的并行实现。

(5)熵编码

AVS视频标准使用k阶(k=O~3)指数哥伦布码。CBP、宏块模式和运动矢最等用0阶指数哥伦布码编码。量化系数使用全部4种指数哥伦布码,采用2D-VLC编码方法,对量化系数的(run、level)进行编码。指数哥伦布码的码字结构非常规则,解码器不需要存储码表。量化系数使用的19张映射表所需的存储空间小于2 KB。视频标准还定义了新的ESCAPE编码方法,能够获得O.05~O.08 dB的编码增益。

2.3 程序在DSP上的优化

本系统压缩部分程序以AVS参考代码rm52f为编码部分的源代码基础,针对AVS编码算法和DSP的特点对其结构和算法进行了调整和改进。对程序作如下优化:

①合理设置结构体和变量类型。经常用到的数组变量不放到结构体中,否则要进行双级寻址,降低效率;对变最长度进行合理定义,严格合理区分8位、16位、32位的变量分配,能用小的则不用大的。(注意:在循环体中,循环计数变量应一律使用int型,即船位,而不要使用short型)

②循环展开。过多过深的循环不利于编译器做软件流水优化,影响DSP并行处理,因此根据DSP特性适当拆开内循环,可以使DSP在一个周期内执行多条指令。优化循环较好的方法是抽出循环作为单独文件,对其重新编写、编译和单独执行。由于内层循环是惟一可以进行软件流水的循环,所以应该注意以下问题(否则会使循环不能进行软件流水,严重影响性能):①可以包括内联函数,但不可包括函数调用;②不可有条件终止、提前退出指令;③必须递减计数且在O时终止(可用-o2、-o3自动转换);④不可在循环体中修改循环计数值。

③使用EEMA方式进行数据搬移,这在CPU频繁访问外部存储器数据时能大大节省CPU资源。其主要实现了下列数据传输:视频数据从片外存储器传到片内Cache中;编 码数据从片内传输到片外保存;做运动补偿时,将片外对应的参考块数据传输到片内。

④使用内联函数和线性汇编。DSP提供了许多非常有用的内联函数(Intrinsics),使用这些内联函数可以很大程度地提高程序运行速度。对于耗时最多的运动估计和DCT变换部分进行线性汇编能大大提高程序的执行效率。使用线性汇编和标准汇编相比,不必考虑并行指令安排、指令延迟、寄存器使用和功能单元的使用,可以大大缩短编写代码的时间,且效率远远高于C程序。

⑤利用编译选顶。可以通过参数-o3的设置进行最高级别的软件流水线优化;可以通过参数-mt告诉编译器源程序没有使用混叠技术,以此提高编译器优化的效果;可以通过参数-pm的设置,使编译器对程序级代码进行优化。使用C64xx型DSP时,应使用-mv6400编译选项,以便对此类DSP进行更高级别的优化。

⑥利用快速算法。AVS编码器中,运动估计耗时相当大。优化运动估计的搜索次序,采用自适应的搜索策略可以较大地提高运动估计的速度,比如使用FastME来进行优化。另外在1/4像素插值方面也可进行一些调整,以避免重复计算。

3 总结

本系统很好地实现了对视频数据的实时压缩处理及传输,能够实现图像数据读写、内存读写、SDRAM读写、配置空间读写和寄存器读写操作,同时协调几种操作实现图像数据的AVS压缩。本系统能够完成4路CIF格式(352×288)视频的实时编码,且有预留资源可供性能扩展。以CIF格式测试序序bus为例,本系统压缩的结果:当设置QP为36时,码率为952.77 kbps,SNRY(亮度信号的信噪比)为30.80 dB,编码速度为36 fps。从结果中可以看出,对于视频监控系统,PSNR(峰值信噪比)指标较理想,编码速度也满足了实时的要求。随着AVS视频编码技术的不断完善,该系统可以很容易地进行升级,将在电视会议等领域得到广泛应用,具有很大的发展潜力。

-

处理器

+关注

关注

68文章

19313浏览量

230044 -

dsp

+关注

关注

553文章

8011浏览量

349143 -

多媒体

+关注

关注

0文章

500浏览量

37002

发布评论请先 登录

相关推荐

当算术运算期间发生除以零或下溢/溢出时,ARM926EJ-S内核的行为是什么?

OMAP-L138的ARM端有浮点处理能力么?

基于AT91SAM9G35 SAM9G35 MCU ARM9系列的评估套件AT91SAM9G35-EK

基于ARM926EJ-S内核微处理器单元的AT91SAM9X25-EK评估套件

基于AT91SAM9G25 SAM9G25 MCU ARM9系列的评估板AT91SAM9G25-EK

ARM926EJ-S处理器技术参考手册

ARM926EJ-S通用应用基板用户指南

用于ARM926EJ的RealView平台底板-S用户指南

基于ARM926EJ-S内核的低功耗ARM

基于ARM 926EJ-S微控制器的网络广播设计

基于ARM926EJ-S的温湿度无线监控系统的设计

ARM926EJ-S应用资料

通过Linux和ARM926EJ-S微控制器实现以太网网络广播的设计

基于ARM9的ARM926EJ-S核实现AVS视频编解码的设计

基于ARM9的ARM926EJ-S核实现AVS视频编解码的设计

评论