引言

锁相环简称PLL,是实现相位自动控制的一门技术,早期是为了解决接收机的同步接收问题而开发的,后来应用在电视机的扫描电路中。由于锁相技术的发展,该技术已逐渐应用到通信、导航、雷达、计算机到家用电器的各个领域。自从20世纪70年代起,随着集成电路的发展,开始出现集成的锁相环器件、通用和专用集成单片锁相环,使锁相环逐渐变成一个低成本、使用简便的多功能器件。如今,PLL技术主要应用在调制解调、频率合成、彩电色幅载波提取、雷达、FM立体声解码等各个领域。随着数字技术的发展,还出现了各种数字PLL器件,它们在数字通信中的载波同步、位同步、相干解调等方面起着重要的作用。

随着现代电子技术的飞快发展,具有高稳定性和准确度的频率源已经成为科研生产的重要组成部分。高性能的频率源可通过频率合成技术获得。随着大规模集成电路的发展,锁相式频率合成技术占有越来越重要的地位。由一个或几个高稳定度、高准确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

1 锁相环及频率合成器的原理

1.1 锁相环原理

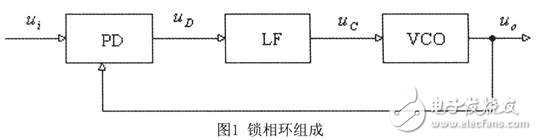

PLL是一种反馈控制电路,其特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因PLL可以实现输出信号频率对输入信号频率的自动跟踪,所以PLL通常用于闭环跟踪电路。PLL在工作的过程中,当输出信号的频率与输入信号的频率相同时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是PLL名称的由来。PLL通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,PLL组成的原理框图如图1所示。

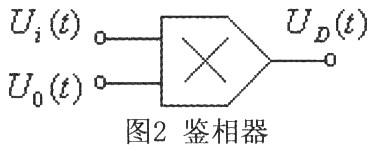

PLL中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:

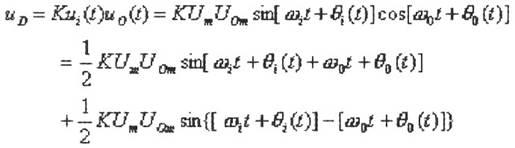

式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压uD为:

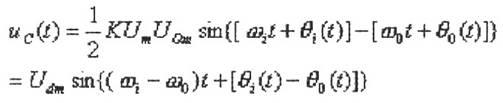

用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。即uC(t)为:

式中的ωi为输入信号的瞬时振荡角频率,θ i(t)和θ 0(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:

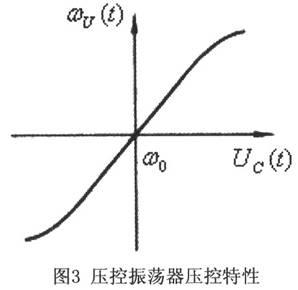

上式等于零,说明PLL进入相位锁定状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。当上式不等于零时,说明PLL的相位还未锁定,输入信号和输出信号的频率不等,uc(t)随时间而变。因压控振荡器的压控特性如图3所示,

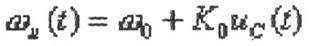

该特性说明压控振荡器的振荡频率ωu以ω0为中心,随输入信号电压uc(t)的变化而变化。该特性的表达式为

上式说明,当uc(t)随时间而变时,压控振荡器的振荡频率ωu也随时间而变,Pll进入“频率牵引”,自动跟踪捕捉输入信号的频率,使PLL进入锁定状态,并保持ω0=ω。

1.2 频率合成器原理

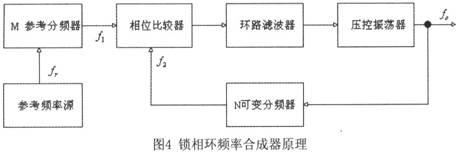

如图4所示,PLL频率合成器是由参考频率源、参考分频器、相位比较器、环路滤波器、压控振荡器、可变分频器构成。参考分频器对参考频率源进行分频,输出信号作为相位比较器参考信号。可变分频器对压控振荡器的输出信号进行分频,分频之后返回到相位比较器输入端与参考信号进行比较。当环路处于锁定时,有f1=f2,因为f1=fr/M,f2=f0/N,所以有f0=Nfr/M.只要改变可变分频器的分频系数N,就可以输出不同频率的信号。

2 集成锁相环CD4046电路介绍

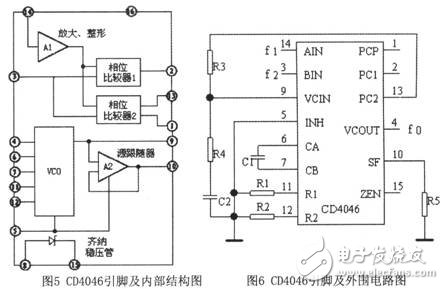

CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V~8V),输入阻抗高(约100M Ω),动态功耗小,在中心频率f0为10kHz下,功耗仅为600μW,属微功耗器件。在电源电压VDD=15V时最高频率可达1.2MHz,常用在中、低频段。CD4046内部集成了相位比较器1、相位比较器2、压控振荡器以及线性放大器、源跟随器、整形电路等。各引脚功能如下:

1脚是相位输出端,环路人锁时为高电平,环路失锁时为低电平。2脚是相位比较器I的输出端。3脚是比较信号输入端。4脚是压控振荡器输出端。5脚是禁止端,高电平时禁止,低电平时允许压控振荡器工作。6、7脚是外接振荡电容端。8、16脚是电源的负端和正端。9脚是压控振荡器的控制端。10脚是解调输出端,用于FM解调。11、12脚是外接振荡电阻。13脚是相位比较器2的输出端。14脚是信号输入端。15脚是内部独立的齐纳稳压管负极。图5是CD4046内部结构图,图6是外围电路连线图。

相位比较器1采用异或门结构,使用时要求输入信号占空比为50%.当两路输入信号的高低电平相异时,输出信号为高电平,反之,输出信号为低电平。相位比较器1的捕捉能力和滤波器有关,选择合适的滤波器可以得到较宽的捕捉范围。相位比较器2由一个信号的上升沿控制,它对输入信号的占空比要求不高,允许输入非对称波形,具有很宽的捕捉范围。相位比较器2的输出和两路输入信号的频率高低有关,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”,反之则输出逻辑“1”.如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器2输出的为正脉冲,当相位超前时则输出为负脉冲。而当两个输入脉冲的频率和相位均相同时,相位比较器2的输出为高阻态。压控振荡器需要外接电阻R1、R2和电容C1.R1、C1是充放电元件,电阻R2起频率补偿作用。VCO的振荡频率不仅和R1、R以及C1的取值有关,还和电源电压有关,电源电压越高振荡频率越高。

3 频率合成器外围电路设计

3.1 参考频率源

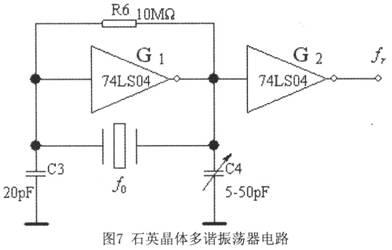

本设计中参考频率源选用CMOS石英晶体多谐振荡器-产生2MHz的矩形脉冲信号,电路如图7所示。

3.2 可变分频器

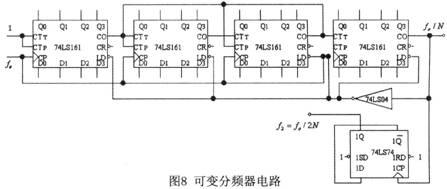

可变分频器由集成四位二进制同步加法计数器74LS161来完成。这里采用4片74LS161通过预置数的方法来实现可变分频。为提高工作速度,可采用图8所示接法。利用同步方案最高可实现65536分频。预制值=65536-N.经过可变分频后获得的信号是窄脉冲信号,在输出端可利用74LS74对该信号进行二分频,以便获得方波信号,从而满足相位比较器1的占空比要求。此时实际分频系数变为2N.电路如图8所示。

参考分频器与可变分频器采用同样的电路,目的在于通过设置不同的分频系数M,以实现不同的频率间隔的需求。

3.3 环路滤波

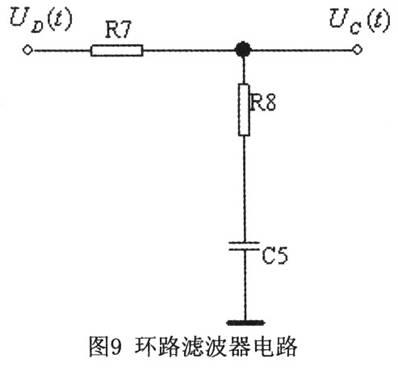

本设计选取无源比例积分滤波器作为环路滤波器,其时间常数T=(R7+R8)C5电路如图9所示。

4 电路的调试

在调试的过程中需注意R1、R以及C1的选取,选取不同的R1、R、C1并合理设置可变分频系数N就可获得不同频率范围的输出信号,同时根据所需情况选取合适的滤波器,设置不同的参考分频系数即可改变频率间隔。

5 结束语

本电路由于频率范围和频率间隔可根据具体需要进行调节,且输出信号频率具有高稳定性和准确性,可广泛作为离散信号源来使用,也可用于集成。此外,如用单片机对分频器的置数端进行控制,可更加方便地实现频率的调整。

-

集成电路

+关注

关注

5388文章

11556浏览量

361977 -

频率合成器

+关注

关注

5文章

220浏览量

32362 -

电视机

+关注

关注

7文章

396浏览量

44090

发布评论请先 登录

相关推荐

一种基于ADF4106的锁相环频率合成器应用实例介绍

基于ADF4106的锁相环频率合成器

锁相环MC14046构成的新型频率合成器

锁相环及频率合成器的原理及电路设计方案介绍

锁相环及频率合成器的原理及电路设计方案介绍

评论