引言

LDPC 码最早于1962 年由Gallager提出,可以看成是一个具有稀疏校验矩阵的线性分组码。自从Mackay 和Neal发现LDPC 码的性能非常接近香农限以后,LDPC 码越来越受到人们的重视。基于准循环LDPC(QC-LDPC)码结构特点,提出了一种支持多种码率QC-LDPC 译码器的设计方法,并设计实现了一个能够实时自适应支持三个不同H 阵的通用QC-LDPC 译码器。

1 QC-LDPC 码简介

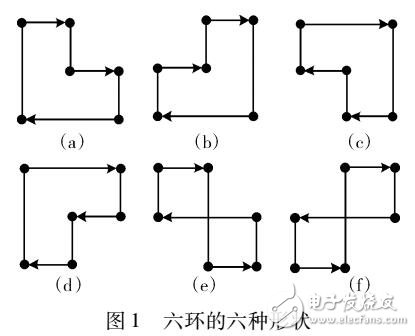

QC-LDPC 码的校验矩阵Hqc是由c × t 个循环置换矩阵组成的,其中c,t均为整数,且c < t 。将QC-LDPC码的校验矩阵中每一个置换矩阵替换为相应的移位值,这样得到了一个新的矩阵,称为基本矩阵。基本矩阵与Η 阵是一一对应的。QC-LDPC 规则的结构使得其编译码在工程上易于实现,因此许多标准中的LDPC 码都采用了QC-LDPC 码。

2 译码算法简介

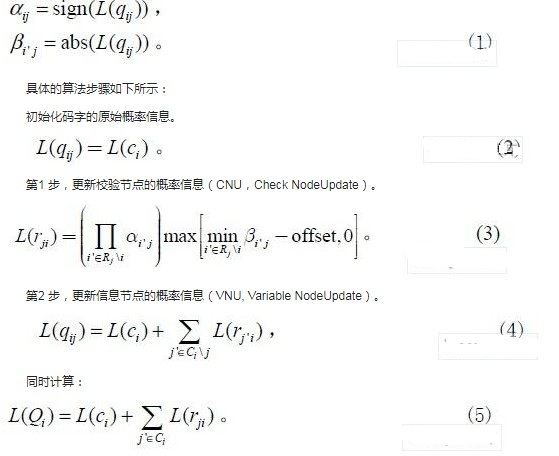

这里设计的译码器主要采用基于软判决的偏移值最小和算法。偏移值最小和算法是在和积算法和最小和算法的基础上改进而来,具有译码复杂度低,性能优异等特点。为了能够较好地描述该算法,先对一些符号进行定义。

L(ci )表示输入译码器变量节点i 的原始软信息, L( rji) 表示由校验节点j 传递给变量节点i 的信息, L(q ij )表示由变量节点i 传递给校验节点j 的信息。而αij ,βi ' j 的意义如式1 所示:

L Q 进行硬判决,若( ) 0 i L Q > ,判决为0 否则为1。计算cHT 是否为0,或者已经达到设定的最大迭代次数,如果是转第3 步,否则转第1 步。

第3 步,输出判决结果。

通过仿真,文中确定的译码器输入定点化方案如下:量化位宽为6 bit,其中3 bit 表示整数位,2 bit 表示小数位。

3 多码率LDPC 译码器设计

首先考虑下面3 种QC-LDPC 码字作为参考,码长8 064bit,码率分别为7/8, 3/4, 1/2。其中,不同码率的最小和译码算法所需的最佳偏移值((3)式中的offset 值)经仿真得到,分别为1, 0.7, 0.5。上述QC-LDPC 码中所用到的码型膨胀因子是112。

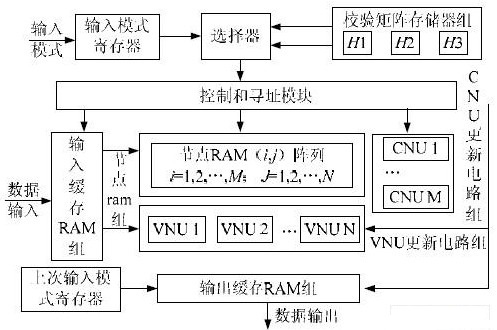

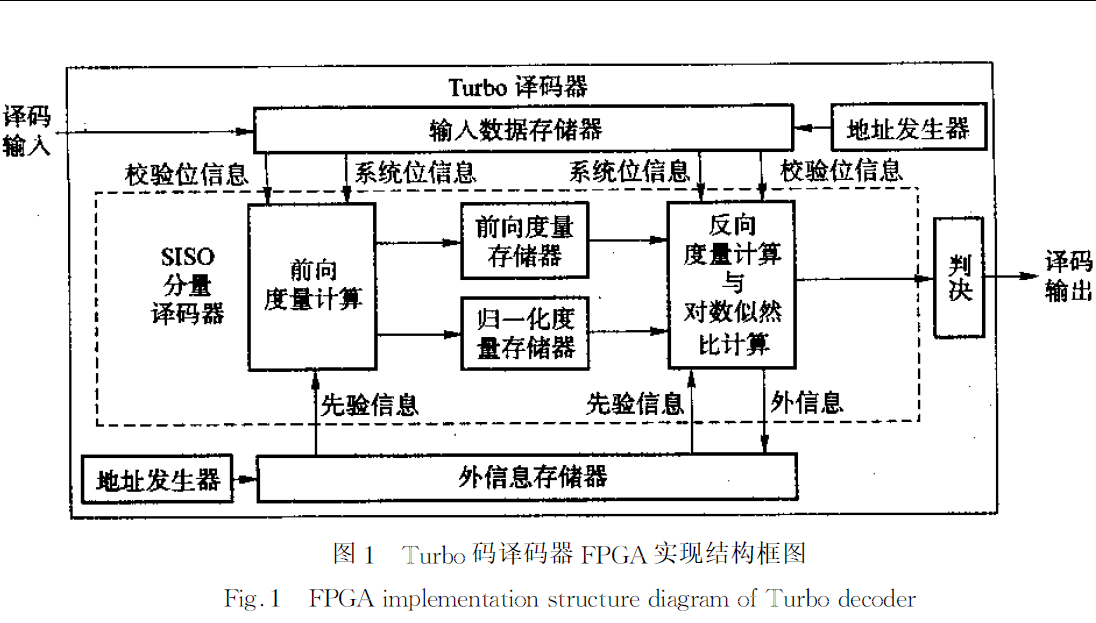

文中实现的LDPC 译码器基于部分并行的译码结构,对译码器进行了输入输出双缓冲处理,支持数据连续处理,总体的结构如图1 所示。

图 1 译码器的总体结构

由于要支持三个不同H 阵的LDPC 码,所以需要有一个模式端口,告知译码器当前数据块是属于哪个码型。输入模式寄存器控制选择器选择不同的H 阵来配置控制和寻址模块,使其能选择需要更新的节点RAM 和需要更新的校验节点单元(CNU),变量节点单元(VNU)的电路套数。

输入数据首先输入到输入缓存RAM 组中,输入缓存RAM 组按照基本矩阵的列数分成N 块对数据进行缓存,其中N 可配置,文中用到的N 是72。数据存满一帧编码块后,就输入到节点RAM 组中。节点RAM 组的作用是对算法迭代更新时的中间信息进行存储。由于基本矩阵中有较多的零矩阵,所以实际生成的节点RAM个数远小于M × N 个。

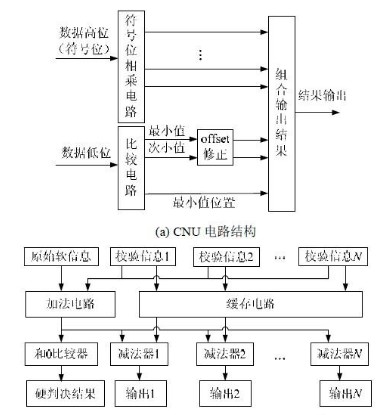

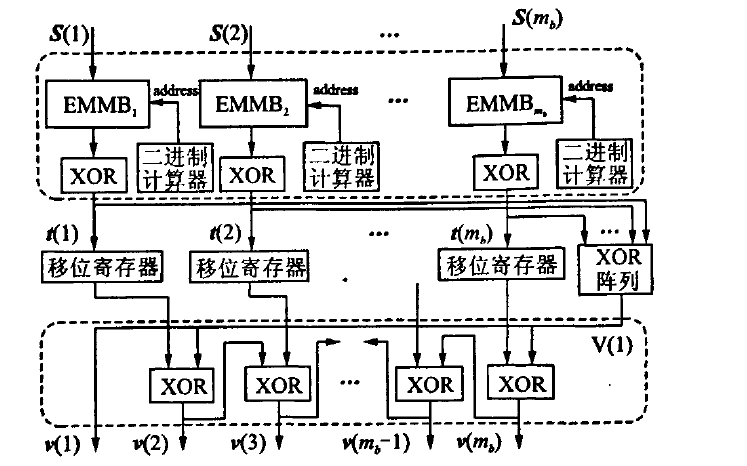

CNU 电路的用途是做校验节点概率更新,完成式(3)的计算。实现结构如图2(a)所示。VNU 电路的用途是做变量节点概率更新,同时计算硬判决结果,完成式(4)和式(5)的计算。

具体结构如图2(b)所示。

图2 CNU 和VNU 电路的结构

输出缓存RAM 组用来存储和输出译码结果,同样也采取了乒乓操作,支持数据块连续的输入输出。控制和寻址模块是译码器的核心模块,它为译码器提供各种控制信号和读写RAM 的寻址信号。寻址模块分为CNU 地址产生模块和VNU 地址产生模块两部分,CNU 地址产生模块的起始地址都是其偏移值;而VNU 地址产生的地址则都是从0 到Z。

由于采用了输入输出双缓冲,所以译码器中最多可以存在三块数据块,同时这三块数据块可以是不同码率的数据块,这就实现了对连续输入的不同码率数据块自适应译码的功能。

4 FPGA 实现以及性能测试:

根据以上设计方案,选用Verilog HDL 进行设计,同时采用了Modelsim 6.1b 进行了仿真验证,最后在Stratix IIEP2S180F1020I4 芯片上进行了测试。具体见表1 所示。

表1 资源占用情况

表1 中同时也列出了一个单码率译码器的资源占用(7/8码率)。可以看出,该多码率译码器在资源占用不超过2 种码率译码器资源之和的前提下能够有效支持3 种码率。

同时,还针对每种码率都测试了其吞吐率和运行的最高时钟,其中三种码率(1/2,3/4,7/8)工作最高时钟均为110 MHz,最高吞吐率分别为110 Mb/s、165 Mb/s 和192.5 Mb/s。从该测试结果可以看出,该多码率译码器吞吐率也在110 Mb/s以上,说明其在满足自适应多码率应用需求的同时,仍然保持了很高的译码吞吐率。

5 结语

针对QC-LDPC 码特点,提出了一种多码率QC-LDPC译码器实现方法,并用FPGA实现了此通用的多码率译码器,可支持至少三种不同码型的QC-LDPC 码。此多码率QC-LDPC 译码器的输入输出参数可以根据所需支持的码型灵活配置,最终实现的译码吞吐率对任何码率都可超过110 Mb/s,兼顾了多码率译码器所需的灵活性和高吞吐量。

-

FPGA

+关注

关注

1631文章

21810浏览量

606818 -

芯片

+关注

关注

458文章

51391浏览量

428445 -

译码器

+关注

关注

4文章

312浏览量

50504

发布评论请先 登录

相关推荐

一种通用的低成本QC-LDPC码译码结构

大围数QC_LDPC码的译码器该怎么设计?

基于FPGA 的(3,6)LDPC 码并行译码器设计与实现

最新LDPC译码器结构论文合集

IEEE 802.16e中LDPC译码器的实现

码长连续变化的QC-LDPC码的设计

高码率LDPC码译码器的优化设计与实现

WIMAX LDPC码译码器的FPGA实现

一种基于距离图的QC-LDPC构造算法

基于FPGA 的LDPC 码编译码器联合设计

大列重低复杂度的QC-LDPC码构造

如何使用FPGA实现结构化LDPC码的高速编译码器

如何使用FPGA实现跳频系统中的Turbo码译码器

采用FPGA芯片实现多码率QC-LDPC译码器的设计与测试

采用FPGA芯片实现多码率QC-LDPC译码器的设计与测试

评论