1 引言

超声波流量计是一种新兴的工业产品,具有无阻挡体,无可动件,无压损,无示值漂移,适用于大口径管道测量,测量精确度高,重复性强,量程比宽,可承受工作压力高,可测多相流,不受气体温度、压力、组成等变化的影响、易于实现数字通信等优点。为减小甚至避免流速分布对流量计精度带来的影响,超声波流量计采用多声道超声波的测量方式。

对于多声路超声波流量计,发射和接收电路是公用的,通过传感器切换电路测量转换各个声路顺流和逆流传播时间,但由于各个声路的长度不同,传感器的特性存在差异,每次测量的接收信号大小也不同,并且强度也不稳定。因此,要实现超声波信号的精确测量,必须根据接收信号的强度自动调节接收电路增益,而且要单独控制每个方向上的增益。为实现高精度的测量,在信号到达检测电路之前必须使信号稳定可靠。为此,信号处理要采用自动增益控制放大器。

2 自动增益控制AGC

自动增益控制AGC(Automatic Gain Control)是一种在输入信号幅度变化很大的情况下,使输出信号幅度保持恒定或仅在较小的范围内变化的自动增益控制环路,即当输入信号很弱时,自动增益控制电路的增益较大,自动增益控制电路不起作用;当输入信号很强时,自动增益控制电路进行控制使增益减小。这样,当输入信号强度变化时,输出端的信号电压或功率基本不变或保持恒定。

信号传输过程中,随着传输距离的变化及其他因素的影响,信号在空间传播过程中存在明显衰落,在接收机输入端的信号强度有很大变化。因此在接收机前端必须加一个幅度控制系统,自动增益控制环路是信号传输中必不可少的。

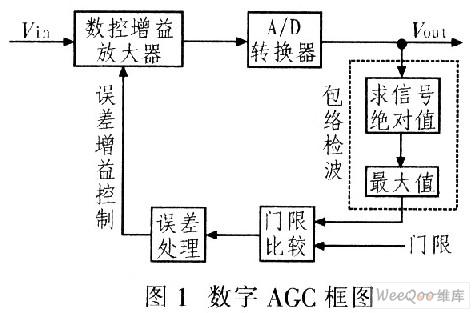

数字AGC精度高、适应性好、体积小、可靠性高,因此受到广大设计人员的关注。图1为数字AGC框图。

3 数字AGC的设计

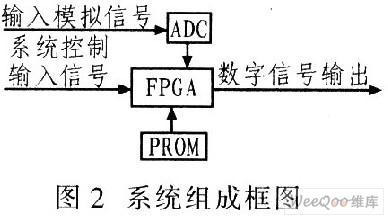

数字AGC系统组成包括A/D转换器(ADC)、现场可编程门阵列(FPGA)、可编程只读存储器(PROM),如图2所示。

3.1 FPGA选型简介

该设计采用Altera公司的ACEX系列FPGA器件EPlK30TCl44-3作为核心控制器,其特点是:高密集型;适合大容量应用的低成本可编程结构;多电平标准系统,其I/O接口可驱动2.5 V和3.3 v器件或被5 V器件驱动;灵活的内部连接;强大的I/0接口.对于每个I/0接口有独立的三态输出控制使能,对于每个I/O接口都有开漏输出选择。

EPIK30TCl44-3型FPGA满足该系统设计要求,30 000个逻辑门适合于数字系统设计所需的逻辑门数量;多电平标准简化了FPGA与外部电路的接口;102个功能强大的I/0接口方便了FPGA外嗣电路设计;JATG边界扫描功能为系统开发与完善提供了很大的方便。

3.2 FPGA内部设计

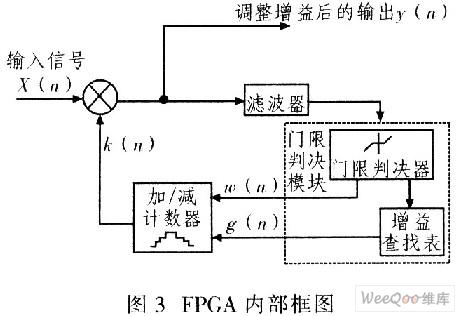

该设计主要由乘法器、门限判决、寄存器、加/减计数器4个模块组成,实现40 dB动态范围的控制。FPGA内部框图如图3所示。

经A/D采样后的信号x(n)进入FPGA进行处理。x(n)首先进入乘法器模块与可控增益因子k(n)相乘,然后分成两路。一路作为调整增益后的AGC输出y(n);另一路送入门限判决模块。门限判别模块包括门限判决器和增益查找表,门限判决器内设有高低2个门限,当输入包络信号电平大于高门限时,则认为输入信号过大,应调整增益控制因子k(n)减小:当输入包络信号电平小于低门限时,则认为输入信号过小,应调整增益控制因子k(n)增加。对于增加或减少的步进量g(n)则从增益查找表中得到。加/减计数器模块根据查找表得到的步进因子g(n)及门限判决模块提供的计数方向w(n)来调整增益控制因子的。

3.2.1 门限判决模块

门限判决模块用于限制加/减计数器控制号的波动,防止环路振荡,其内设高低2个门之间的范围即为AGC输出信号的波动范围。防止AGC发生振荡,该范围应该在满足解调器要求的动态范围条件下足够宽,而不是恒定不变的电平值。如果大于高门限,则认为信号过大,首先送给加/减计数器一个向下计数的信号,然后根据信号的范同从查找表中确定加/减计数器的步进量;如果小于低门限,则认为信号过小,首先送给加/减计数器一个向上计数的信号,然后根据信号的范围从查找表中确定加/减计数器的步进量;如果在两门限之间,则加/减计数器的步进量为零。

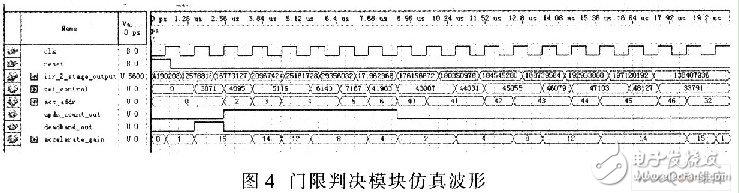

图4是门限判决模块的仿真波形。其中,clk为时钟信号,reset为复位信号,iir_2_stage_output为滤波器的输出信号,set_control为与门限进行比较的信号,acc_addr为查找表地址,updn_count_out为控制加/减计数器的计数方向,dead_band_out为控制加/减计数器的计数控制信号,accelerate_gain为控制加/减计数器的计数步进量。

从图4中可以看出,当信号小于低门限7500时,dead_band_out=‘0’,updn_count_out=‘1’,控制加/减计数器向上计数,set_control远离低门限,计数步进量增大;当信号大于高门限10 500时,deadband_out=‘0’,updn_count_out=‘0’,控制加/减计数器向下计数,set_control远离高门限,计数步进量增大。

3.2.2 加/减计数器模块

加/减计数器模块根据输入信号与最佳的接收信号之间的差值,对输入信号进行反向补偿。假设输入信号经过一定衰减,AGC环路经过比较可确定接收信号电平低于最佳电平。这个差值将导致计数器向上计数,增加环路增益,直到环路滤波器的输出重新回到门限判决模块的两个门限之间。如果信号乘以增益后、环路滤波器的输出信号大于门限判决模块的高门限时,计数器向下计数,降低环路增益,直到信号重新回到可以准确解调所需的接收信号范围。

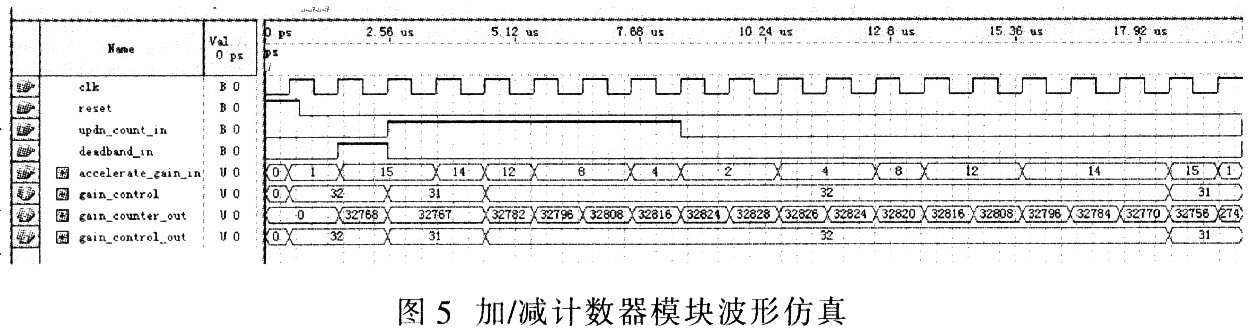

图5是加/减计数器模块的仿真波形。gain_counter_out为截位前的增益值,gain_control_out为截位后实际输出的增益值。从图5看出,当reset=‘1’时,计数器复位,设增益初始值gain_control_out=‘32’。而当deadband_in=‘O’,updn_count_in=‘1’,加/减计数器按步进量accelerate_gain_in向上计数;而当deadband_in=‘O’,updn_count_in=‘0’,加/减计数器按步进量accelerate_gainjn向下计数。计数所得的值即为输出的增益控制因子。

4 结论

本文实现了一种全数字AGC的设计方案。此方案可实现40 dB动态范围的控制,并且具有控制精度高,调节速度快,调试简单,受环境影响小,稳定性和可靠性高等优点。随着集成器件的发展,有望实现高动态范围的全数字AGC,以便应用到更广阔的领域中。

-

传感器

+关注

关注

2551文章

51106浏览量

753644 -

FPGA

+关注

关注

1629文章

21738浏览量

603459 -

超声波

+关注

关注

63文章

3017浏览量

138399

发布评论请先 登录

相关推荐

基于FPGA和EPlK30TCl44-3d实现超声波气体流量计中全数字AGC的设计

基于FPGA和EPlK30TCl44-3d实现超声波气体流量计中全数字AGC的设计

评论