引言

Profibus-DP是由西门子公司推出的一种开放式现场总线标准,用于现场级分布式自动化外设之间的高速数据传输。Profibus在2007年4月突破2000万节点大关。据PI(世界性的现场总线Profibus用户组织)称现在已经超过2 500万个节点,并希望在2012年突破5 000万个节点,年销售芯片450万个。

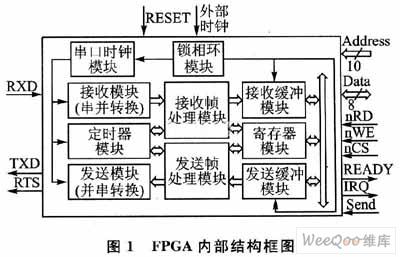

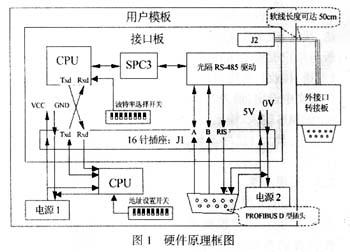

目前国内业界对于Profibus-DP的研究和相关产品的开发都是基于国外提供的专用协议芯片(主站多数采用西门子推出的ASPC2,从站多采用SPC3等智能通信芯片),而没有协议芯片样机开发的相关报道。对于主站的开发,国内一些科研院所(北航706教研室、中科院、浙大等)也曾利用可编程逻辑器件配合MCU设计出简单主站的试验产品,但是这些产品仅能实现单主站的功能,对于组成强大的Profibu-DP网络还望尘莫及。为了打破国外芯片的垄断,推动国内相关芯片及产品的开发,本文提出了一种FPGA与ARM相结合的方式解决Profibu-DP 1类主站的主主通信及主从通信问题,实现了比较完整的主站研制方案。

1 Profibus-DP主站通信机理及技术特性

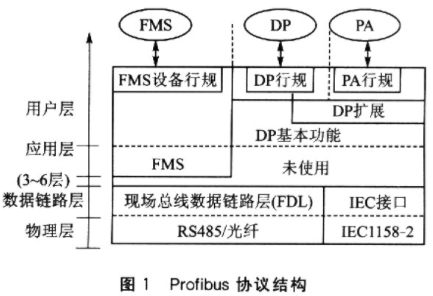

1.1 Profibus-DP主站通信协议

Profibus协议的结构以OSI为参考模型,DP使用第1层、第2层和用户接口,第3层到第7层未加以描述。一个DP系统既可以是一个单主站结构,也可以是一个多主站结构,本文涉及的是多主站结构。多主站结构使用混合的总线访问控制机制,主站之间采取令牌控制方式;令牌在主站之间传递,拥有令牌的主站拥有总线访问控制权;主站与从站之间采取主从的控制方式。

令牌是一种特殊的报文,如下所示:

SD为开始分界符,DA为目的地址,SA为源地址。令牌环是所有主站的组织链,按照主站的地址构成逻辑环。在这个环中,令牌在规定的时间内按照地址的升序在各主站间依次传递,用户通过编写令牌传递程序保证每个主站在一个确切规定的时问内得到令牌,之后该主站就可以在规定的时间内与所属从站通信,也可与所有主站通信。其中主站与所属从站间的数据通信由主站按已确定的循环顺序自动地进行处理。

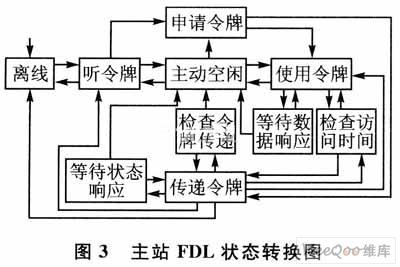

1.2 令牌循环时间分析

最坏情况下令牌循环时间为:

其中,TTH为站点令牌保持时间,TTS为令牌的整体传输延迟,TMA为令牌维护时间。在不考虑出错重发的前提下,N个主站令牌的整体传输延迟TTS=N·TTK,TTk是发送令牌PDU(协议数据单元)需要的时间。高优先级报文的传送时间为THMS,报文数量为M;低优先级报文的传送时间为TLMS,报文数量为L。

2.2 ARM控制器部分程序设计

ARM控制器程序对应于Profibus通信协议数据链路层之上的DDLM直接数据链路映射程序、主站通信状态机、应用层数据接口及应用层。

本设计对Profibus-DP协议按层次封装为函数,层层调用。

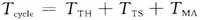

2.2.1 Slave_Handler状态机

Slave_Handler状态机功能块负责实现主从通信功能,根据从站状态做出相应处理,有固定的处理次序,每次调用Slave_Handler状态机产生一个DDLM请求,从而控制从站进入相应的通信状态。Slave_Handler状态转换图如图2所示。

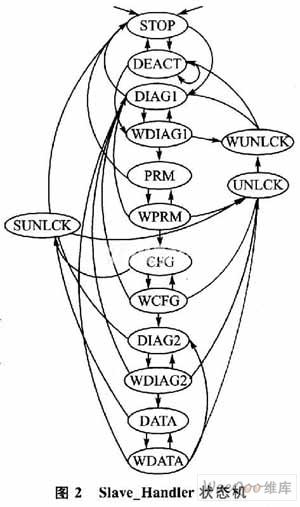

2.2.2 Scheduler和FDL_Controller状态机

Scheduler状态机功能块负责实现对Slave_Handler状态机的控制。它向Slave_Handler状态机发送从站轮询控制信号,控制其逐步与从站建立数据交换关系。

FDL_Controller状态机由10个FDL状态组成并在这些状态间转换,如图3所示。

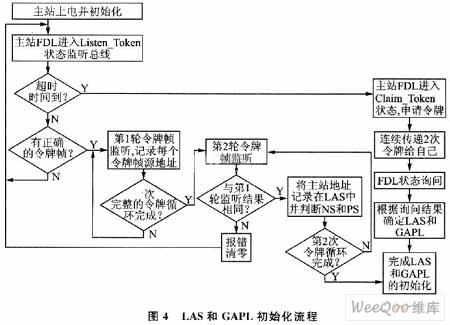

逻辑令牌环的建立主要工作是对LAS和GAPL的初始化。LAS和GAPL的具体初始化流程如图4所示。

LAS的形成标志着逻辑令牌环初始化的完成。接下来就是逻辑令牌环运转的维护阶段,令牌将按照LAS进行循环传递,得到令牌的主站有权进行对其所属从站的轮询。传递过程中主站将以固定的时间间隔,通过Request FDLStatus主动帧来询问自己GAP范围内的所有地址,并根据询问结果修改LAS和GAPL。在主站活动表生成之后,前驱站询问ReqtJest FDL Starus,主站回复准备进入逻辑令牌环,并从Listen_Token状态进入Active_Idle状态(主站的前驱站会修改自己的GAP和LAS,并把该主站作为自己的后继站)。主站在Active_Idle状态*总线,能够对寻址自己的主动帧作应答,但没有发起总线活动的权力,直到前驱站传送令牌给它,它保留令牌并进入Use_Token状态,在此状态下驱动Scheduler状态机工作。主站持有令牌后,首先计算上次令牌获得时刻到本次令牌获得时刻经过的时间(即实际轮转时间tRR),并与用户设定的目标轮转时间tTR比较,如果tRR小于tTR,则主站开始处理传输任务。首先处理高优先级传输服务,所有高优先级服务处理完毕后处理低优先级服务。在这个过程中,每一个完整的报文循环之后,主站就重新计算tTR—tTH。若结果小于0,主站进入PassToken状态,将令牌传递给后继站,未完成的任务留到下一次令牌持有的时候再执行。所有传输服务都完成后,不管是否有时间剩余,主站都交出令牌。如果主站接到令牌时发现tTR—tTH

3 系统工作过程

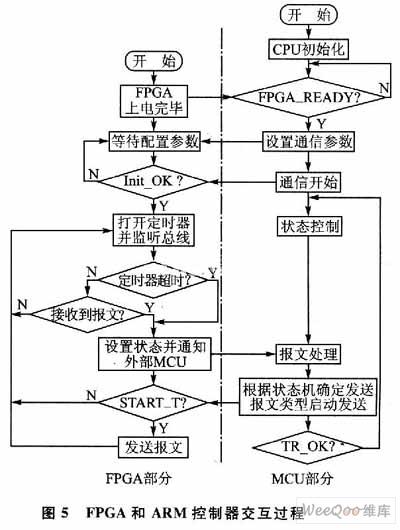

系统工作过程主要是ARM控制器和FPGA的通信交互过程,如图5所示。从系统安全性上考虑,FPGA和ARM建立通信必须有双方的确认信号,虽然Altera Cyclone系列FP-GA从上电到稳定之前引脚没有输出,从系统安全性角度考虑还是不够的。

这里FPGA_READY信号的设计是考虑到FPGA内部锁相环模块PLL稳定工作之前需要建立时间,而其未稳定时是不能对其进行操作的。通信的状态通过ARM控制器上的状态机(FDL控制状态机、调度状态机和主从通信状态机)进行转换,根据定时要求、从站响应帧给出的信息,以及错误检查等信息,状态机能够应付一般的异常并自行恢复到正常的通信之中。

4 结论

Profibus-DP协议用任何微处理器都能实现,只要微处理器配有内部或外部的异步串行接口(UART),但当数据传输速率较快(超过500 kb/s)时,用ASIC芯片来实现更安全可靠。本文充分利用了FPGA实时性好和ARM核微控制器便于开发的优点,实现了Profibus-DP 1类主站,经过搭建简单测试环境进行测试,能和市场上的成品主从站建立通信连接并进行基本的主主、主从通信。

-

FPGA

+关注

关注

1626文章

21666浏览量

601836 -

芯片

+关注

关注

453文章

50402浏览量

421802 -

ARM

+关注

关注

134文章

9046浏览量

366815 -

西门子

+关注

关注

93文章

3008浏览量

115635

发布评论请先 登录

相关推荐

基于PROFIBUS-DP的电能管理及电力监控系统

如何实现集成PROFIBUS-DP主站接口的软PLC控制器?

怎样去解决ARM与PROFIBUS-DP的通信问题呢

PROFIBUS-DP主站通信卡的研发

PROFIBUS-DP从站通讯模块

基于VC的Profibus-DP通信系统的设计与实现

PROFIBUS-DP主站通信卡的研发

Profibus-DP通信系统的设计

Linux和S3C2410的PROFIBUS-DP主站平台设计

Profibus-DP现场总线结构、技术特性及实现应用设计

PROFIBUS-DP主站转ETHERNET/IP网关ethernet和tcp/ip的区别

Profibus-DP主站通信平台的设计方案

Profibus-DP主站通信平台的设计方案

评论