引 言

微机保护装置是指微机系统构成的数字式继电保护装置。在我国煤矿井下高压(6kV)供电系统中,绝大多数属于变压器中性点绝缘运行方式(三相三线制),通过动力电缆送电。煤矿井下环境恶劣,空间狭窄,动力电缆长期处在潮湿、淋水、腐蚀的环境中,散热条件差,绝缘性能易下降,经常发生单相漏电或单相接地故障。这种故障引起正常相电压升高,若不及时断电,会造成多相短路,迫使供电中断,并使电力故障进一步扩大。高压防爆开关微机保护装置是安装在高压防爆开关中,对井下电缆和用电设备的单相漏电或单相接地、短路、过流、绝缘监视、过欠压等故障进行综合保护的一种装置,能快速切除故障回路,防止事故扩大,通知维护人员及时排查故障源并排除。因此,对高压防爆开关微机保护装置提出很高的可靠性要求: 在故障发生时能快速动作;在未故障时,不能误动。然而,高压开关通断感性负载(井下电器设备主要是电动机等感性负载)时刻,开关触点拉弧会产生很强的电磁干扰和浪涌干扰,严重程度可造成CPU的程序跑飞。这种电磁干扰是高压防爆开关微机保护系统的头号强干扰源,主要通过电源线和交流互感器摸入通道侵入微机保护系统。微机保护系统长期工作在这种强电磁干扰中,抗干扰性能成为衡量微机保护系统的重要指标之一。

提高微机保护装置的抗干扰性能的根本途径是阻塞共模干扰的耦合通道,提高敏感回路的抗干扰能力,合理设计接地泄放回路等措施。电磁兼容性(EMC)设计是一个复杂的系统工程,从硬件上考虑抗干扰设计是非常必要的,但想从硬件上完全消除干扰是不可能的。还要从软件上考虑数字滤波等,很难做到尽善尽美。国内科技人员在单片机系统、微机测控系统的抗干扰技术等方面做了很多研究工作,发表大量的抗干扰技术论文,可分为两大类。一类是从硬件电路阻塞干扰信号的入侵通道,如模拟通道加前置滤波器、电源输入加电源滤波器、开关入与出加光耦隔离、pCB布局和布线的抗干扰技术、接地技术和屏蔽技术等等;另一类是软件抗干扰措施,包括数字滤波、指令冗余、软件陷阱、软硬件看门狗等。硬件措施抗干扰是拒干扰信号于门外,是电磁兼容性设计的主攻方向。软件抗干扰是在硬件尚未失效前提下,利用软件的灵活性设计来抵消干扰的影响,只能起到辅助的抗干扰作用。关于微机保护装置的控制出口可靠性设计的文献很少,归纳起来,防止控制出口失控的常用措施有两种: 硬件冗余设计和软件冗余设计。硬件冗余设计基本方法是采用双或多CPU结构,一个负责保护的启动,另一个CPU负责保护的执行。两个CPU相“与”才开始控制出口。软件冗余设计主要采用以下措施:

(1)设置多重跳闸命令,分多条控制指令来执行分闸,在每条指令之间执行一段核对程序,设置相应的标志位。CPU核对标志位相符后才执行下一条指令,否则初始化重来。

(2)设置当前输出状态寄存器的状态信息,系统运行自检程序循环查询测试这些状态,若发现干扰出错,及时纠正输出通道的出错信息。

多CPU结构设计是防止保护误动,提高微机保护系统可靠性的一种有效措施,但采用多CPU结构使硬件结构复杂,调试繁琐,成本高,而且当多CPU同时程序跑飞时,同样造成控制出口失控,有可能引起误动。软件冗余设计是在程序运行正常情况下提出的(即假设CPU运行程序正确,没有出轨),如果程序跑飞,已经执行不到软件冗余设计程序,则控制出口处于失控状态,既使看门狗电路起作用,使CPU复位重新回到正常程序,经历的时间最短也要几毫秒。在这段时间内,干扰信号足以引起控制出口的误跳闸。显然,上述两种方法并不能完全确保继电保护控制出口的可靠性和安全性。

对微机保护系统来说,最重要的一点就是当强干扰引起程序跑飞后,不能引起继电保护控制出口的误动作。笔者在研制KJ118型矿用变电所远程监控系统配套的高压防爆开关微机保护系统中,针对继电保护控制出口的特点,创造性地提出采用CPLD技术,加强微机保护控制出口的可靠性研究,成功设计出一种基于CPLD的抗干扰微机保护控制出口硬件电路。文中介绍的这种基于CPLD控制接口抗干扰设计的新方法,比多CPU结构更简单,更经济,可靠性更高,不依赖于CPU本身的抗干扰性能,即使CPU程序跑飞,控制接口仍有很高抗干扰性能,不会产生误跳闸电平,彻底解决继电保护系统控制出口的可靠性问题。

CPLD技术在微机保护装置中应用的优越性

CPLD(complex programmable logic device,复杂可编程逻辑器件)与FPGA(field programmable gate array,现场可编程门阵列)是两大可编程ASIC(application specific intergrate dcircuit)芯片,都可用VHDL(very high speed intergrate dcircuit hardware description language)进行描述和编程下载。CPLD门阵列规模较FPGA小,CPLD主要结构是基于乘积项,易于实现较复杂的组合逻辑。CPLD的逻辑宏单元较FPGA少,较多的触发器时序逻辑用FPGA较合适。FPGA主要结构是基于SRAM的查表项,虽然电路结构配置灵活,但延时不可预测,实际传输延时要大于CPLD。CPLD采用EEpROM编程技术,掉电配置信息不丢失。FPGA采用SRAM工艺开关技术,上电通过在线可重配置方式对FPGA进行功能配置,理论上可无限次配置,并可实现真正意义上的在线可配置,但掉电配置信息丢失,必须借助串行EEpROM、单片机等进行上电的重配置。对于I/O数量和触发器数目不太大的应用场合,CPLD在使用方便性和编程的保密性均优于FPGA。

微机保护系统中的数字组合逻辑电路和时序逻辑电路规模均不大,宜采用CPLD芯片实现,有利于微机保护系统的微型化和智能化设计。

微机保护装置控制接口设计

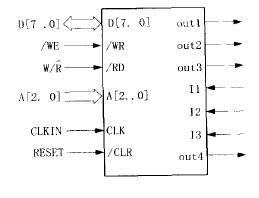

微机保护系统的控制接口由I/O接口和微型继电器组成,典型电路是将分合闸继电器分成2级,第1级控制第2级。第2级控制主回路的分合闸接触器。原理框图如图1所示。

2级继电器有利于隔离主回路的分合闸接触器通断产生的干扰。

合闸指令执行顺序为:OUT1→OUT2→OUT4。分闸指令执行顺序为:OUT1→OUT3→OUT4。如果I/O接口直接由CPU控制,当CPU受干扰程序跑飞或CPU芯片出故障使I/O接口失控,正巧产生分合闸所需的电平时,继电保护控制出口就不可避免地发生误动。

图1继电保护控制出口原理

因此,继电保护控制出口的闭锁和冗余度设计是防止控制出口误动的关键所在。严格监视分合闸多重命令的执行顺序,不允许无序分合闸命令通过,是防止控制出口误动的根本措施。分合闸多重命令的有序执行,可以看作一个状态变化序列,用CPLD状态机对这个状态序列进行监控,就能杜绝无序状态的通过,实现控制出口的无干扰控制。

基于CPLD状态机的抗干扰控制接口设计

设计一个基于DSP的高压开关柜微机综合保护系统时,用一片CPLD芯片实现图1所示的I/O接口,并设计一个有限状态机,对状态输入I1,I2,I3进行监控,状态机输出作为总分合闸命令的允许和禁止信号。基于CPLD的微机保护控制接口如图2 所示。

图2微机保护的CPLD控制接口

分合闸多重命令的状态编码

状态机有3位二进制输入,共有23=8种状态。采用二进制编码方式(Binary coded)将控制接口的初始状态S0到所有可能的状态变迁,列成一张编码表,如表1 所示。状态编码表是编写VHDL程序的基础。

表1微机保护控制接口状态机编码表

状态机设计

状态机的时钟频率为5MHz。复位信号/Reset来自DSP微机保护装置的系统复位信号,对状态机的状态初始化。

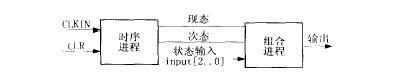

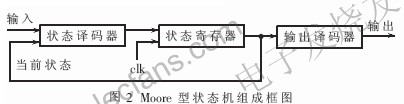

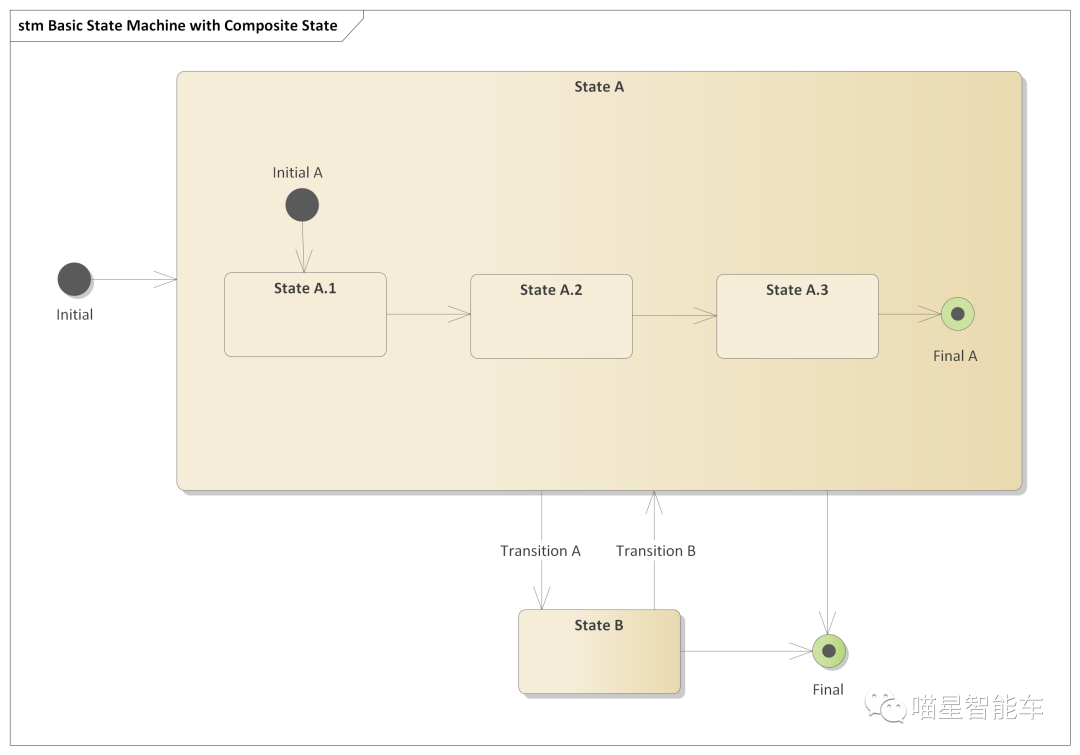

状态机的设计可采用单进程,双进程,3进程等进行编写,根据微机保护控制接口的应用特点宜采用双进程来描述状态机,即一个时序进程和一个组合进程。时序进程负责旧次态到新现态的转换,以及异步复位。组合进程完成根据现态决定状态机输出的变化,根据状态输入来决定新的次态。双进程状态机的逻辑框图如图3所示。

图3双进程状态机逻辑图

状态机的行为及代码是一种流程控制代码,很容易用VHDL语言中的CASE语句和IF语句加以实现。时序进程与组合进程之间利用现态信号和次态信号进行同步通信。

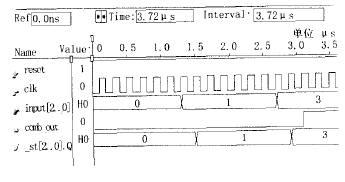

状态机仿真波形

利用Altera公司的EDA工具软件MAX+plus对用VHDL语言设计的状态机进行时序仿真,仿真波形如图4所示。

图4状态机仿真波形

CPLD状态机抗干扰控制原理分析

基于CPU的微机系统是按指令周期顺序执行机器指令的,一旦受干扰程序出轨,则CPU不按事先编好的流程执行程序,出现死机,通常的对策是设置看门狗使CPU硬件复位,使CPU重新运行正常程序,但是从CPU死机到看门狗复位一般要经历几毫秒到1~2s,这段失控时间,继电保护控制出口的状态是不可预测的,足以对继电保护系统构成危害,严重情况就是发生误动。而基于CPLD的状态机系统,状态变换周期只有一个时钟周期,若时钟频率为5MHz,时钟周期为012Ls。若状态机受干扰进入非法状态再转入合法状态,只需2个时钟周期,即几百纳秒,不足以对状态机系统运行造成危害。可见,用CPLD状态机控制微机继电保护的控制接口,就能实现无干扰控制,获得继电保护系统的高可靠性控制。

就DSP芯片与CPLD芯片的可靠性比较而言,DSP的外围接口繁多,输入信号有模拟和数字,电压有模拟电压和数字电压,CPLD只有数字接口,电压单一,受外界干扰损坏的可能性比DSP小的多。另外,CPLD状态机含有多个进程,就相当于包含有并行运算的“多CPU”功能,对不合格的输入,裁决状态机输出0。因此,笔者认为,双CPU控制硬件冗余设计远不如CPLD状态机的控制接口可靠性高。

结 论

用Altera公司的MAX7000系列的EMp7128SLC84-15实现继电保护控制接口,与TMS320F240DSP芯片总线直接相连,DSP执行合闸或分闸多重命令时,不需要插入等待周期,只需要连续执行3条合闸或分闸指令,CPLD状态机就能立即决定是否允许总执行命令通过。试验表明: 用CPLD实现的继电保护控制接口具有速度快,占用硬件体积小,接口简单,可靠性高等特点。

该接口应用到基于TMS320F240的高压开关柜数字综合保护装置中,随KJ118型矿用变电所远程监控系统于2003年10月在徐州矿务局旗山煤矿井下采区变电所投运,进行工业性试验,正常运行至今已超过半年以上。采区变电所现场高爆开关就地人工分合闸操作、地面主机遥控命令分合闸以及故障保护跳闸试验表明,从未发生因高压开关分合闸操作等强电磁干扰引起CPU程序出轨而误动,表现出非常高的可靠性。

文中用全新的CPLD状态机方法研究微机保护系统的控制可靠性问题,对于瞬变干扰信号有很强的滤波性。虽然从防范微机保护系统程序出轨采用一些软件措施有一定效果,但是并不能真正解决程序出轨期间控制口的失控问题,而文中提出的CPLD状态机控制接口真正解决了这一问题,可以推广到各种微机控制系统的抗干扰控制接口设计中去。

-

芯片

+关注

关注

457文章

51361浏览量

428312 -

cpld

+关注

关注

32文章

1257浏览量

169708 -

cpu

+关注

关注

68文章

10922浏览量

213300

发布评论请先 登录

相关推荐

状态机“毛刺”的产生及消除方法

如何设计自动驾驶系统的状态机

FPGA/CPLD状态机稳定性研究

微机控制系统抗干扰设计试题题型相关资料下载

PLC控制系统应用的抗干扰问题研究

利用状态机实现对tlc5620dac控制.

微机保护系统控制的CPLD状态机的抗干扰控制接口设计

微机保护系统控制的CPLD状态机的抗干扰控制接口设计

评论