曼彻斯特码编码、解码器是1553B总线接口中不可缺少的重要组成部分。曼彻斯特码编解码器设计的好坏直接影响总线接口的性能。本文介绍的是MIL-STD-1553B接口中最曼彻斯特码的编码和解码器的设计实现。

在电子设计领域,可编程器件的广泛应用为数字系统的设计带来极大的灵活性,1片FPGA/CPLD芯片可替代上百个IC电路。同时,Altera公司开发的MAX+PLUS II和QUARTUS II软件,是完全集成化的可编程逻辑设计环境;Synplicity公司的Synplify是专门用于FPGA和CPLD的一种优秀逻辑综合工具;VHDL更是一种功能强大的硬件设计语言,可用简洁的代码描述来进行复杂控制逻辑的设计。所这些使得硬件的设计如同软件那样方便,极大方便了数字电路的设计。所有这些条件都为在实验室开发实现MIL-STD-1553B协议接口提供了有利条件。文中所设计的编码、解码器就是采用硬件描述语言VHDL进行编程,用Synplify进行综合,以及采用MAX+PLUS II进行时序仿真,在FPGA上实现的MIL-STD-1553B总线接口中的曼彻斯特码编码、解码器。

1 1553B总线及其接口功能

MIL-STD-1553B的全称是:飞机内部时分制指令/响应式多路传输数据总线。它用可屏蔽双绞线进行数据传输,信号是以串行数字脉冲的形式进行传输,其数据代码用双相曼彻特码的形式来表示,其传输速率为1Mb/s。1553B数据总线上连接有三种类型的系统:①总线控制器(BC)——控制总线上的数据传输;②远程终端控制器(RT)——响应BC来的命令,执行数据传输;③总线监视器(BM)——有选择地接收数据总线上的信息并保存之。每个子系统可以通过1553B总线连接到任何一个子系统。数据就是在总线上进行传输的。

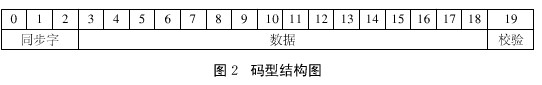

在总线上传输的有三种类型的字:命令字、状态字和数据字。每种字的字长为20位,有效信息位是16位每个字的前三位为同步字头,最后一位为奇校验位。有效信息(16位)及奇偶校验位在总线上以曼彻斯特码的形式进行传输,每位占的时间为1μs。同步字头占三位,或先正后负(命令字、状态字)或先负后正(数据字)。正/负电平各占1.5μs,即占同位场的一半。由于系统的类型不同,可辨别出命令字和状态字,命令字由现行的总线控制器发出,而状态字总是由远程终端RT发出。

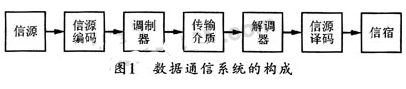

作为MIL-STD-1553B总线的接口应完成以下功能:①将总线上的串行信息流转换成处理机可以处理的并行信息或者与之相反;②接收或发送信息时,能够识别或生成标准的1553B信息字和消息;③完成与处理机之间的信息交换,包括1553B信息地址的分配,命令字(或状态字)的译码或返回状态字、发送数据字等。曼彻斯特码编解码器完成的是曼彻斯特码的编码及解码,并检测错误。它接收具有有效同步字的曼彻斯特码,并进行译码,

以及识别其类型和串/并转换、奇偶校验等;或者将处理器发出的并行二进制数据进行曼彻斯特码编码,再加上同步字头及奇偶位使之成为符合1553B标准的字进行输出。

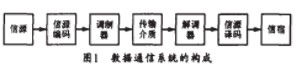

编解码器是总线接口的一部分。一般说来,1553B总线接口由电平转换电路、曼彻斯特码编解码器、命令字/状态字译码逻辑和CPU及相关电路组成,如图1所示。

除了编解码器可由FPGA来实现外,它与CPU之间的相关电路,如共享RAM、命令字/状态字译码和存储器管理、处理器与存储器接口逻辑等也可以由FPGA来实现;CPU可采用TMS320LF2407。本文所介绍的就是其中的编码和解码器的设计。

2 曼彻斯特码编解码器的总体设计

在介绍编解码器的设计之前,有必要了解曼彻斯特码的特征,以便在设计中对其加以利用,达到简化电路的效果。

曼彻斯特码是一种广泛应用于航空电子综合系统中的总线数据传输的双极性码。它在每个码位中点存在一个跳变。1信号是一个由1到0的负跳沿,而0信号是由0到1的正跳沿。它本身包含了自定时的信息。因此它不需要独立的信道来传输位定信息,它可以直接从数据中分离出定时时钟,同时还能与变压器耦合相协调,十分适合用在变压器耦合形式,长度为150m(500英尺)左右的场合,因此在航空电子综合系统中,它是最主要的形式。

在MIL-STD-1553B协议中其数据格式为如图2所示。

根据1553B的数据格式以及曼彻斯特码的特点,可采用状态机对其进行编码、解码的实现。状态机是一个广义的时序电路,像移位寄存器、计数器等都算是它的特殊功能类型中的一种。根据输入、输出及状态之间的关系,状态机可分为两类:一种是输出状态有关,而输入与状态无在的状态机类型,称为More状态机;另一种是输出及输入与状态皆有关系的状态机,称为Mealy状态机。本设计采用的是Mealy状态机。编码和解码是两个相互独立的模块。

2.1 解码

解码的过程可分为三部分:①同步字头检测,并辨别其为数据字还是命令字。②对曼码形式的数据进行解码。由于曼彻斯特码自带定时时钟,故可从数据中分离出同步时钟。本设计采用的是传统的用数字锁相环的方法来分离时钟;将时钟和数据进行处理使曼码数据转化为非归零二进制数据。③将串行数据转化为并行数据,并进行奇偶校验。解码器的逻辑图如图3所示。图中data为串行输入数据。当data开始发生跳变时进行同步头检测,若在data发生变化后检测到大于一个位时的高(或低)电平,则认为同步头有效,输出同步头类型(comnd)及同步头检测位(synerr)(为低电平,若为高电平则表示同步头有错)。在同步头有效后,进行时钟分离及码型变换及移位,移位完成后进行奇偶校验,并把数据定写入保持寄存器,此时rxrdy变为高电平,表示数据准备好可以读出数据。进入下一个解码周期,等待串行输入数据。

该逻辑可由状态机实现,可划分为四个状态进行:第一个状态是空闲状态,当检测到数据跳变沿时,进入第二个状态;第二个状态为有效同步字头检测状态;当检测到有效同步字头,启动第三个状态,用锁相环分离时钟,进行码型转换;当数据有效时进入第四个状态,进行并/串转换及奇偶校验。其状态机状态转换如图4所示,以下是具体实现过程。

①同步字头检测。当检测到数据跳变沿(下跳沿为命令字,上跳沿为数据字)时,用16MHz时钟对数据进行采集;当采集到大于一个位时的低电平或高电平时,认为同步字头有效,启动第二状态,进行处理。启动位产生的时间要注意选择,这对于消除数据中的毛刺和减少数据的延时都很重要。

②码型转换。检测到有效同步字后,启动锁相环开始分离时钟。此设计采用超前-滞后锁相环,锁相环如图5所示。

图5中边沿检测器的输出e是在u2(t)的跳变沿时产生的窄脉冲,d是c的反相,c、d、e经过与门后在f和g形式滞后和超前脉冲。h和g分别用来控制和扣除门和添加门,通过扣除门和除脉冲和通过添加门添加脉冲,它们的和输出经过分频器2得到c,也即u2(t)就能跟随u1(t)的相位了。

边沿检测器的工作原理是在u1(t)的上跳沿时放过一个16MHz的时钟脉冲,这样产生的边沿检测脉冲e只会在f和g中的一个产生脉冲,也就避免了超前一滞后型数字锁相环存在的相位模糊问题。该锁相环的相位锁定时间最大为42ns,因此在与数据进行模二加之前,应将数据进行延时,以便消除毛剌。要想完全将毛剌消除还要配合同步字头检测时,启动位产生时间的设置。这在后面毛剌处理中有详细的介绍。

③奇偶校验和串行并转换。用移位寄存器可实现数据的串/并转换。在设计移位寄存器时,要注意奇偶位的分离,因此在设计寄存器时需设置一定的标志位,其源代码如下:

if reset=‘0’then

rsr《=(others=》‘0’);

--全为零可确保在移位过程中idle为低电平;

rxparity《=‘1’;

--确保在移位过程中idle=0,而在移位结束时,idle=1;

tag《=‘0’;

--移位标志位设置,当tag=1时,移位完成;

paritygen《=paritymode;

--为奇校验时paritymode赋值为1,若为偶校验则设置为0;

elsif rxclk‘event and rxclk=’1‘then

if idle=’1‘then

rsr《=(others=》’0‘);

rxparity《=’1‘;

tag《=’0‘;

paritygen《=paritymode;

elsif hunt=’1‘then

tag《=rsr(15);

rsr(15 downto 1)《=rsr(14 downto 0);

rsr(0)《=rxparity;

rxparity《=data1;

--进行移位,为右移寄存器;

paritypen《=parityegen xor rxparity;

--进行奇偶校验;

end if;

end if;

至此曼彻斯特的解码就完成了,其时序仿真波形如图6所示。

畋6中data1.Q时,进行码型转换后的数据。由图中可以看出采用此种方法进行转换,数据没有毛刺,产生的数据完全正确。

2.2 编码

编码的过程也可分为三部分:①检测编码周期是否开始,产生同步字头;②进行串行转换,产生奇偶校验位;③对16位有效数据及奇偶位进行编码,编码周期结束。与解码同理,编码也由状态机来实现。

由此状态机可划分为四个状态进行实现,其状态机状态转换如图7所示。

编码器的输入时钟(mclk)为16MHz。当写信号(wr)为低电平时,同步头选择位(cmnd)为高是怦,开始产生命令字同步字头;反之,为同步字头。由于同步字头的高低电平各占1.5个位时,所以选取它的发送时钟为2MHz,该时钟由mclk八分频得到。同步字头产生完成,则发出控制信号开始移位。移位时钟(1MHz)由同步头生成时用的时钟两分频产生。在数据移位完成时自动添加厅偶位。曼码形成器对数据、奇偶位、同步头进行处理形成符合1553B标准的双极性字tx和ntx,完成后txrdy为高电平,等待下一个数据的写入开始再一次的编码过程,逻辑框图如图8所示。

编码其实是解码的逆过程,其工作原理非常相似,这里就不详细介绍了。编码的时序仿真波形如图9所示。

图9中tx为经过编码后的串行数据。采用此种方法进行编码,产生的数据完全正确,并且也不存在毛剌。

3 设计中存在的问题及解决办法

信号在FPGA器件内部通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关。由于这两方面的因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序。它们并不是同时变化,而且往往会出现一些不正确的类峰信号,这些类峰信号称为“毛刺”。另外,FPGA器件与分立元件不同,其内部不存在寄生电容电感,这些毛刺将被完整的保留并向下一级传递,因此毛刺现象在PLD、FPGA设计中尤为突出。消除数据中的毛剌是设计中的一个重要问题。如果毛刺处理不好,就会影响系统性能甚至引起逻辑错误。

本设计中消除毛剌采用的方法有:①在有毛剌的输出端加D触发器;②计数器采用格雷码计数器。采用D触发器是因为D触发器的D输入端对毛剌不敏感,只要毛刺不存时钟上跳沿时出现在D输入端,就不会对输出产生影响,这样就可以消除毛刺了。采用格雷码计数器代替普通的二进制计数器,是因为格雷码计数器的输出每次只有一位数据产生变化,这就消除了竞争冒险产生的条件,避免了毛刺的产生。例如在解码器的设计中,进行码型变换时,要将接收时钟与接收的串行数据进行模2加。因为时钟滞后于数据,为了消除毛刺要将数据进行延时再进行模2加;同时还要考虑到1553B对时间的要求(两个数据之间的间隔最小只有1.5μs),因此在时钟分离时就考虑提前进行他高。在检测同步头时,一旦其高(或低)电平大于1个位时的宽度就认为同步头有效,开始进行时钟分离,这样就减小了数据延时,可有效节省时间。进行模2加后,加一D触发器可确保完全将毛刺消除。在编码器设计中在串行数据输出端加一D触发器,数据的毛刺 也被了。另外,在电路的设计中尽可能地消除毛刺产生的条件,例如分频计数器采用格雷码计数器。

4 仿真及FPGA实现

为了确保设计的可行性,必须对设计进行时序仿真;为了提高芯片的性能及资源利用率,要采用专门的综合软件对设计进行优化、综合。由此采用Synplify7.1进行综合,采用MAX+PLUS II进行时序仿真。在Synplify中使用有效的代码,优化组合逻辑、减少逻辑延时等措施来提高整体性能,还进行了多个文件的分块设计,然后将这些文件映射到顶层文件进行综合,并运用VHDL对单个文件进行编写、仿真和优化。在用到组合逻辑时,Synplify会尽量避免锁存器的出现,节省逻辑单元。Synplify和其它综合软件一样,编译后生成的电子设计交换格式文件(EDIF)可以在MAX+PLUS II或Quartus II 3.0中进行编译、仿真、分配引脚和其它优化处理。因此,采用MAX+PLUS II和Synplify 7.1相结合对FPGA进行设计、优化、综合,可提高系统性能和芯片资源的利用率。

最后本设计在Altara公司ACEX1K系列的FPGA(EP1K100Q208-3)芯片上进行了实现。对于ACEX系列的芯片,它还支持寄存器配平技术、流水线操作、复制逻辑模块、使用LPM函数等技术来提高其整性性能,并针对其特点对设计进行了最后的优化。该编解码顺共占用了218个逻辑单元,占总逻辑资源的4%,这有利于今后对其进行完善和功能的添加。其输入时钟为16MHz,数据速率为1MHz,编码和解码时序波形分别如图6所示。

5 总结及设计通用性

该编码解码器采用自顶向下和自向上相结合的方法进行设计,用VHDL语言输入,用MAX+PLUS II和Synplify分别进行仿真、综合。在设计最后,针对器件进行了再一次的优化,缩短了设计周期,提高了系统性能,并且大大提高了芯片资源的利用率。

本设计具有一定的通用性,它的逻辑大部分只涉及到编、解码器本身;而它与外部的接口十分简单,只要对其读、写及同步字头选择信号进行有效控制,就能使其正常工作。它的设计是十分独立的。另外,由于选择器件资源比较丰富,故对其进行功能添加也十分方便,只需添加电路设计而不必对原有电路进行修改。

-

FPGA

+关注

关注

1638文章

21853浏览量

609245 -

vhdl

+关注

关注

30文章

819浏览量

128907 -

触发器

+关注

关注

14文章

2025浏览量

61563

发布评论请先 登录

相关推荐

采用复杂控制逻辑器件和VHDL语言实现曼彻斯特编解码器的设计

基于CPLD的卷积码编解码器的设计

EDA卷积码编解码器实现技术

高速并行RS编解码器

用CPLD控制曼彻斯特编解码器

基于FPGA的曼彻斯特编解码器设计

用FPGA器件与VHDL语言实现曼彻斯特码编解码器的设计

用FPGA器件与VHDL语言实现曼彻斯特码编解码器的设计

评论