图像处理系统多采用DSP阵列、DSP加FPGA/CPLD或单由FPGA/CPLD器件等方式构成。采用DSP阵列构成的图像处理系统,其优点是处理功能可以通过软件灵活修改,其缺点主要有功耗大、体积大、成本高;采用单由FPGA/CPLD等可编程器件构成的系统,可以避免DSP阵列系统功耗大、体积大的缺点,并可以根据系统要求,在硬件构造上作灵活的配置,但对于复杂的算法,其设计复杂度急剧上升。正因为如此,当前很多设计选择DSP加FPGA/CPLD的结构来构造图像处理系统。本空间太阳望远镜星载图像处理系统,正是一种基于DSP和FPGA构造的图像处理系统。本文讨论了系统的功能任务、系统结构、FPGA设计的逻辑模块、DSP的软件结构和原理样机的实验结果。

1 图像处理系统的功能和任务

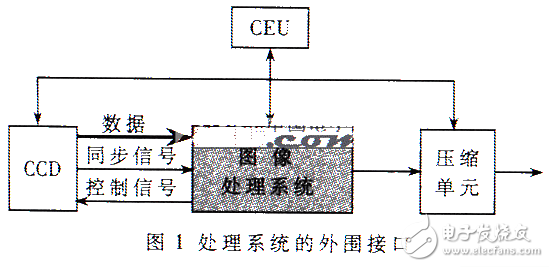

1.1 系统的外围接口

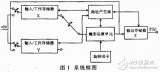

系统的外围接口如图1。处理系统接收来自CCD单元的图像数据和同步信号,同时向CCD单元提供复位、曝光开始、数据读出等控制信号;CEU是一个管理机,管理和控制CCD单元、图像处理单元和压缩单元,CEU单元向图像处理系统发送各种命令,如CCD标定、正常的观测测试及观测数据处理所需要的数据,如观测模式、时间等;系统将处理完成的数据送到压缩单元进一步压缩。

图1 处理系统的外围接口

1.2 系统的图像处理任务

图像处理系统的任务是接收CCD传来的图像和同步信号,进行图像积分、辐射校正、几何校正、磁图偏阵计算和图像格式化,然后把数据送到压缩单元进行压缩。

(1)图像积分:也就是图像的多帧叠加,其目的是提高信噪比和消除图像的时间相关性以压缩数据量。空间太阳望远镜有三个观测模式,分别是爆发模式、活动区模式和宁静态模式。经计算,三种观测模式下图像积分的帧数分别是:4帧、24帧、240帧;每个模式又顺次观测六个分量,六个分量分别是:SV1、SV2、SQ1、SQ2、SU1、SU2。爆发模式的观测时间是30s。30s的时间是这样安排的:每个分量连续采集4帧,每秒一帧,然后1s进行偏振光学元件的切换,如此直到六个分量观测完毕。活动区模式由6个连续的爆发周期构成,观测时间是3min;而宁静态模式又是10次活动区模式周期构成,观测周期是30min。

(2)图像的辐射校正:图像由于受到大气扰动、传感器自身特性、宇宙射线等辐射的影响,图像的质量会产生退化,必须进行辐射校正。主要考虑CCD的校正(暗流、偏置、平场)和条纹斑点的消除两个方面。

(3)图像的几何校正:图像的几何校正,成像过程中引起的几何畸变的校正;由于系统或随机因素造成图像产生几何畸变,必须进行校正。考虑图像漂移的校正,采用相关技术,求出活动图像相对于参考图像的的漂移量,再采用线性内插累加的方式,实现漂移前后图像的积分问题。根据太阳米粒的存活寿命,几何校正只对宁静模式观测进行,并且是以3min作为校正时间间隔。

(4)图像的偏振计算:空间太阳望远镜主要进行太阳磁场测量,磁图的偏振归算也是重要任务之一。磁场图像的归算还可以是数据量压缩1.5倍。

(5)图像格式化:给图像加上图像头,应包括:仪器号、时间、观测模式、观测分量等。

2 图像处理系统设计

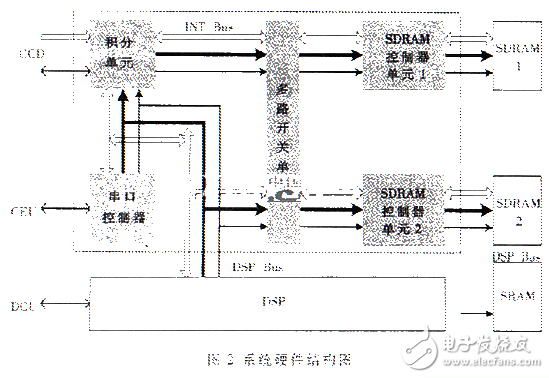

2.1 系统结构

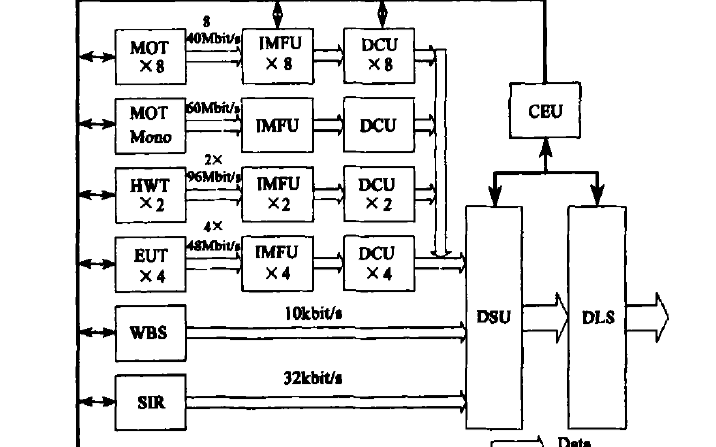

系统的硬件结构框图如图2。FPGA中的硬件模块,包括积分单元、多路开关单元、两个SDRAM控制器和串口控制器。DSP的所有总线都伸入到FPGA内部。存储器由两个SDRAM单元和一个SRAM单元构成,SRAM只供DSP使用。系统接收CCD传来的图像,在积分单元进行图像积分,积分就绪的图像再由DSP进行辐射校正、几何校正、偏振计算和图像格式化等操作,最后通过DSP的片上串口将图像送到压缩单元。通过串口单元系统与管理机单元通信,接受管理和控制。由于图像积分与DSP的数据处理、数据传送是同时并行进行的,因此积分器和DSP必须采用相互独立的存储区。为了避免图像在积分器和DSP的存储区之间来回进行图像传送,在设计中采用多路开关进行存储区乒乓方式切换。

2.2 FPGA逻辑模块

FPGA内部设计的逻辑模块主要包括图像积分单元、通路选择单元、异步通用串口(UART)单元、两个SDRAM控制和其它附加逻辑。下面分别介绍各块的结构,由于SDRAM控制器和串口单元(UART)均采用IP核实现,这里不作详细介绍。

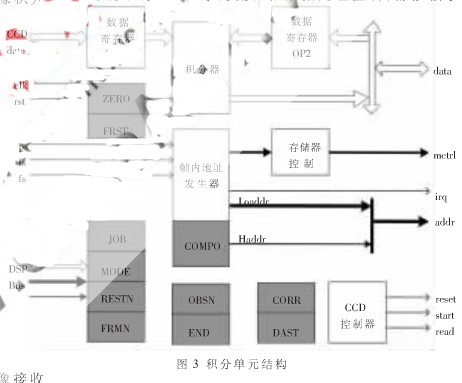

2.2.1 积分单元

积分单元主要完成如下功能:(1)按给定的时序接收CCD的图像,并保存在寄存器中;(2)积分地址产生;(3)存储器控制;(4)积分操作;(5)积分扩展位清零,当每个分量的第一帧图像接收时,无须积分,但必须把存储器的高位(积分扩展位)清零,其它情况不必清零;(6)每帧图像积分结束,产生Irq信号中断DSP,以便由DSP进行工作安排。

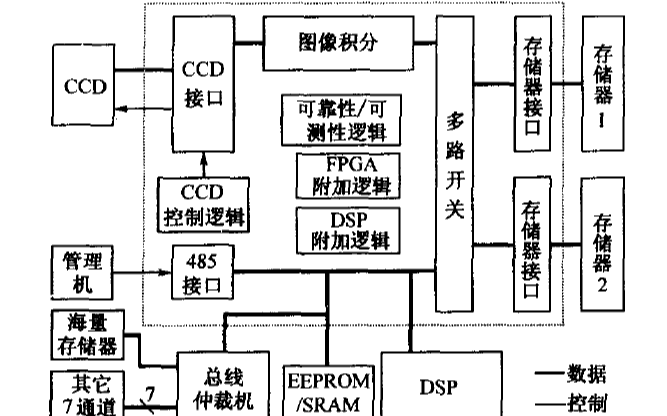

积分单元的逻辑框图如图3,其输入输出如下:(1)CCD输入数据(CCD data),同步信号——点同步(ps)、行同步(ls)、帧同步(fs);(2)DSP数据、地址和控制总线,irq是积分单元发给DSP的中断信号;(3)与存储器连接的数据、地址和存储器控制总线——data, mctrl, addr;(4)控制CCD的信号线——reset、start、read。

图3充色的方框是DSP存储器地址映射的寄存器,用于对积分单元进行控制和对DSP数据处理状态进行标识;无充色的方框则是积分单元的硬件结构,从CCD送来的数据通过数据寄存器(OP1),作为寄分的第一个操作数,从存储器送来的数据通过数据寄存器(OP2)作为积分的第二个操作数;从CCD送来的同步信号,送到帧内地址发生器,作为地址产生信号,并生成存储器需要的控制信号;CCD送来的OP1被寄存,同时产生地址从内存中取出要进行积分的操作数OP2,然后在点同步信号的下降沿,进行积分运算并存回存储器。

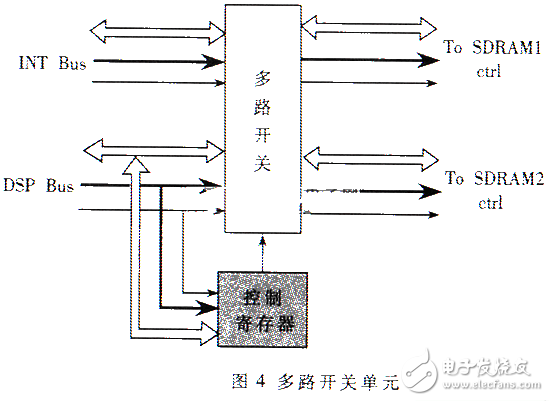

2.2.2 多路开关单元

多路开关单元如图4所示。本单元的功能是完成积分总线INT bus和DSP bus与SDRAM1和SDRAM2乒乓连接结构的切换。切换包括三大总线:数据、地址和控制总线。切换通过一位切换控制信号实现,控制信号是DSP地址映射的一个一位寄存器,由DSP控制乒乓切换。

2.3 DSP软件结构

软件部分包括系统软件框架和各处理软件模块、中断服务程序等;程序的流程和数据处理控制,都依赖于由DSP地址映射的寄存器的状态。

2.3.1 DSP在FPGA中的存储器映像寄存器及其作用

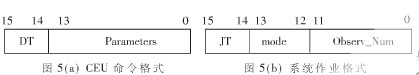

这一组寄存器都是在FPGA中实现的。作业(指令)采用16位寄存器,由于DSP地址空间较大,为了方便编程,寄存器不采用拼位的方法。系统的工作 受CEU的控制。CEU发送过来的指令格式如图5(a),其中DT表示CEU传来的数据类型,00表示数据、01表示观测指令、10表示CCD标定、11表示自测。接收时,若是命令则直接写到JOB或放入命令队列;若是数据,根据类型存放到相应的位置。Parameters是各种工作状态参数,如待机/自测要求的参数、测试的要求(内容、测试选择)、响应信息要求、观测模式和次数、CCD标定要求的参数、标定的内容等,以便于DSP查看。

如图5(b),当CEU送来命令DT=01时,即为观测命令。观测作业的格式如:00表示无作业待机、01表示观测指令、10表示CCD标定、JT=11表示自测;mode是当前观测模式标志,001表示爆发模式、010表示活动区模式、100表示宁静模式;Observ_Num是连续观测同一种模式的次数标志。

(1)作业类型寄存器(JOB):标识系统工作内容(作业类型),如CCD标定、观测、自测试等;(2)模式寄存器(MODE):标识观测的模式,爆发模式、活动区模式、宁静模式;(3)观测次数寄存器(OBSN):用于保存一次作业的观测次数;(4)宁静态的观测次数寄存器(RESTN):只用于宁静模式的观测,当为宁静态模式时,用它来标志3min观测的次数;(5)帧计数器(FRMN):用于计数爆发模式、活动区模式及宁静模式下的前24帧图像,以便用于高位清零信号生成和地址高位生成;(6)SW电路控制寄存器(SWCTRL):控制多路开关的切换;(7)reset寄存器(FRST):用于DSP控制FPGA中INT单元的时序逻辑复位,每次观测结束,必须复位一次;(8)清零标识寄存器(ZERO):由DSP根据FRMN的值修改它,以实现高位的清零任务;(9)分量寄存器(COMPO):由DSP根据FRMN的值修改它,以实现高位地址的形成;(10)作业结束寄存器(END):当一个作业结束时,用次寄存器进行标志,以便将程序的PC跳到作业检查入口;(11)数据状态寄存器(DAST):DSP存储区数据状态标识:没有数据、爆发模式的待处理数据、活动区模式的待处理数据、宁静模式的待处理数据、宁静模式处理好数据及待送出数据等。DSP根据数据状态和观测模式,可以进行相应的处理;(12)相关数据状态(CORR):标识相关运算用的数据的状态。

2.3.2 DSP的存储器空间分配

DSP的SYSCON寄存器的15~12位(MSIZE),可以设置以MS0~MS3作为片选信号时,每个分组的空间大小。其公式为:MSIZE=log2(块大小)-13;取每个块的大小为16MB,因此MSIZE=1011。

·片内空间:0000,0000H~0007,FFFFH;

·MS0——数据空间:0040,0000H~13F,FFFFH;数据是倒序放置的,最后一个单元放第一个数据;其中:

SQa:40,0000~5F,FFFF SQb:60,0000~7F,FFFF

SUa:80,0000~9F,FFFF SUb:a0,0000~bF,FFFF

SVa:c0,0000~dF,FFFF SVb:e0,0000~fF,FFFF

Rest2m:100,0000~11F,FFFF unused:120,0000~13F,FFFF

·MS1——SRAM空间:140,0000H~23F,FFFFH;

·MS2——CCD参数:240,0000H~33F,FFFFH;放置暗流、偏置和平场图像3帧2048×1024图像;

·MS3——未使用:340,0000H~43F,FFFFH;

·未分组空间:4040,0000~FFFF,FFFF所有存储器映射的寄存器。

2.3.3 DSP的软件结构

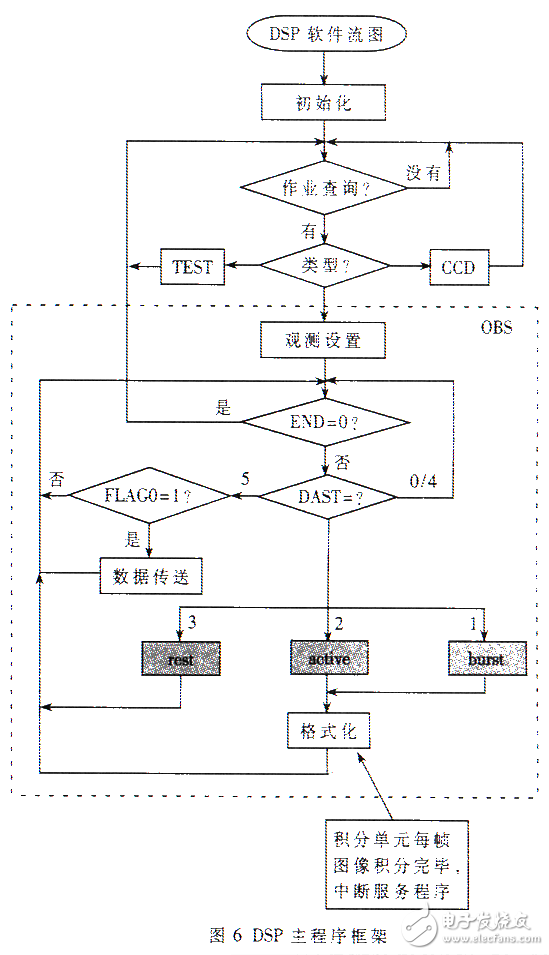

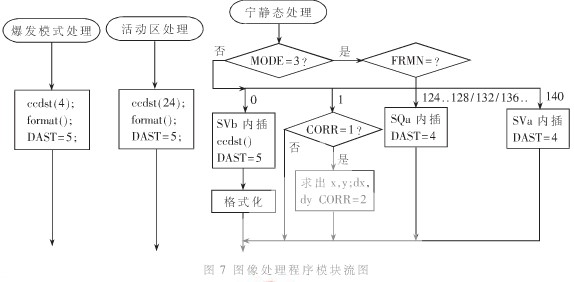

DSP的主程序框架如图6。系统初始化后,进行作业查询,根据查询结果,进行相应的处理任务(CCD标定、自测试、观测)。图6中仅以观测作业为例进行说明。进入观测后,首先由DSP对积分单元作相应的设置,设置完成后,积分器开始单独地积分工作;DSP接着查询本次观测是否结束,若结束回到作业查询,否则判断存储器中数据的 状态,根据数据状态,进行相应的处理;处理就绪的数据根据FLAG0的标志,可以向压缩单元传送数据。三种模式下的图像处理程序流图如图7,图7中ccdst( )是图像辐射标定子程序,format()是格式化子程序,内插运算采用线性内插方法,相关运算采用FFT和逆FFT方法。

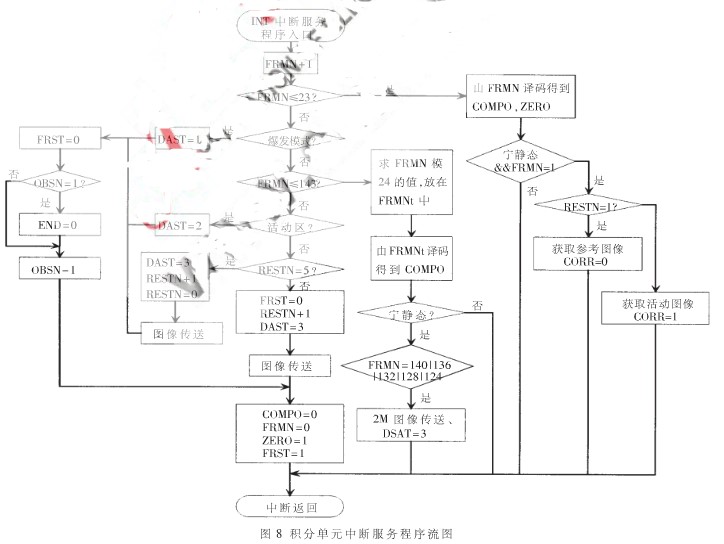

除了主程序和数据处理程序外,DSP还有一个重要的中断子服务,就是积分单元每帧图像积分完毕的中断服务程序,其流程框图如图8。它根据积分的图像帧数和观测模式,判断观测是否结束,根据不同的情况设置积分器中相应的寄存器,这些寄存器控制着积分器的工作行为和DSP的数据处理方法。图8中参考图像和活动图像的获取是在采集到的2048×1024图像的中心,获取256×256的子块,也就是说,相关运算是在两帧256×256的图像之间进行的;对于图像传送操作,考虑到宁静模式的数据处理,要求的存储器比爆发和活动区模式要大一倍。为了不把存储器设计得太大,对于宁静模式,不再采用乒乓存储器切换的结构,而是在数据就绪时,利用光学仪器调整的1s时间,将积分就绪的图像传到DSP的工作区内。

3 样机研制和实验结果

原理样机的研制过程中,DSP器件是AD公司ADSP21060,开发平台采用VisualDSP2.0。FPGA器件选用Xilinx公司100万门的Virtex II系列器件,开发平台采用ISE6.2。已完成的地面样机达到了合同的要求。用(接上页) DSP硬件仿真器对样机作了软硬件测试,首先对各接口进行了测试,在保证数据可以正确地接收和发送后,测试系统的功能。这些测试均在一个专门开发的地面支持系统测试平台上进行。经过单元测试,再与其它单元接在一起进行系统级的联调和系统级测试。结果表明达到设计目标,可以按要求完成系统的各项功能。

-

dsp

+关注

关注

561文章

8275浏览量

368230 -

FPGA

+关注

关注

1664文章

22502浏览量

639155 -

cpld

+关注

关注

32文章

1259浏览量

174162

发布评论请先 登录

操作天文望远镜哪这些必须注意

基于STM32的虚拟天文望远镜

基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统

基于FPGA的并行运算在空间间太阳望远镜图像锁定系统中的应用

分块式空间望远镜波前探测与控制

空间太阳望远镜FPGA星载图像压缩模块的设计与实现

空间太阳望远镜FPGA星载图像压缩模块的设计与实现

如何使用FPGA实现空间太阳望远镜星载偏振图像高速处理技术的设计

基于DSP技术和FPGA器件构造空间太阳望远镜星载图像处理系统

基于DSP技术和FPGA器件构造空间太阳望远镜星载图像处理系统

评论