随着器件集成工艺的发展和Soc器件的出现,现在的数字系统正在越来越多地采用可编程器件设计。这样,不仅开发周期短,而且在价格和使用难易度上也显示了很大的优势。更为重要的是,还能利用器件的现场可编程特性,根据应用的要求对器件进行动态配置,简便易行地完成功能的添加或变化。

在高速的数字信号处理系统中,要涉及到大量的计算,为了提高运算速度,正大量使用DSP器件。目前的可编程器件,其时钟频率可以很高,在高速数字信号处理系统中将发挥越来越大的作用。因此,DSP+FPGA的方案正越来越多地被电子工程师们采用。

在很多的实际数字系统中,往往需要良好的用户界面,其中LCD是被大量采用的显示器件。由于LCD是典型的慢速设备(相对于DSP来讲),在与高速微处理器接口时,会耗费大量时间,这在高速系统设计中是不允许的。如果DSP有不太富裕的处理余量,如何利用它对LCD完成控制呢?仅仅在两者之间加入锁存器之类的简单接口电路,往往不能对LCD完成控制。不过,有了FPGA,就可以在不增加成本的情况下,在DSP和LCD之间设计一条双向的快速通道。

1 DSP和LCD的时序

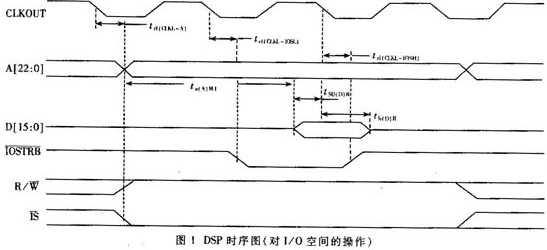

TI公司是DSP在全球的主要供应商,其低价位的TMS320VC54x系列DSP深受广大电子工程师的青睐。下面以TMS320VC5416为例介绍DSP的时序。TMS320VC5416将寻址范围分为存储器空间、程序空间和I/O空间。其中,对I/O空间的操作由地址线、数据线和三根信号线IOSTRB、R/W和IS来完成,其时序图如图1所示。

读操作和写操作由R/W信号线上的高低电平决定。如果不采用外部插入等待周期的方法,仅靠内部的等待周期设置寄存器,访问外部I/O空间时最多可以插入14个等待周期。如果DSP运行在100MHz的主频上(实际上TMS320VC16可以运行在最高160MHz的主频上),也只有0.14μs。这对于LCD来说来远远不够的。

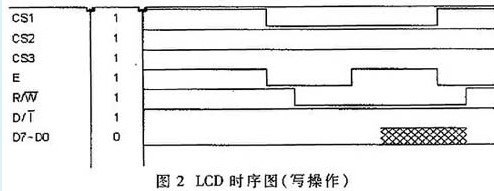

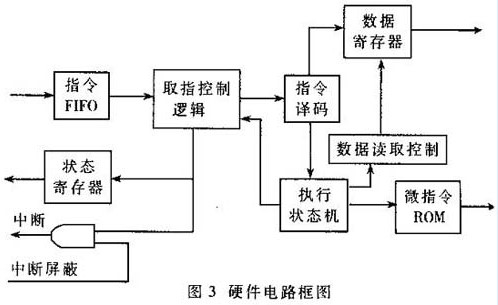

常见的192×64点阵的LCD(FM19264)实际上是由3块独立的64×64点阵LCD构成的,共享地址线和数据线,可由CS1、CS2和CS3分别选中。每小块LCD都有各自独立的指令寄存器和数据寄存器,由控制线D/I上的高低电平选择。数据的锁存或出现在数据线上由E信号决定。LCD主要控制管脚的功能如表1所示。对LCD写操作的时序图如图2所示。LCD的每次读写操作最少要1μs。如果能使DSP对LCD的访问象对高速设备访问一样,就能够最大限度地减小DSP资源的浪费,并且能够减少系统的复杂性,这就需要在FPGA中添加一个DSP与LCD之间的高速双向通道。

表1 LCD主要控制管脚功能

对每块LCD的控制,是通过操作指令寄存器和数据寄存器实现的。在屏幕指定位置写入数据,要分三步(①写入行地址,②写入列地址,③写入数据)才能完成,不但耗时而且增加了软件编程的复杂程度。如果能够将指令和数据合在一起作为一条指令,那么设计一套简单的指令译码电路执行电路就可完成这项任务。

2 硬件电路设计

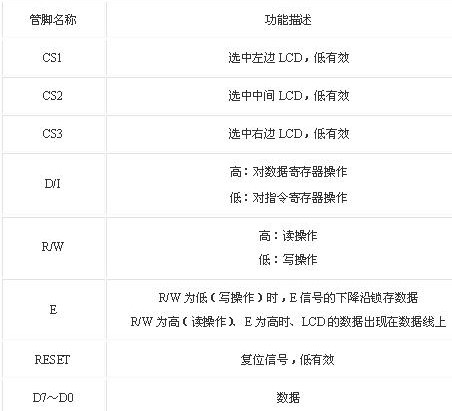

硬件框图如图3所示。LCD的原始控制指令如表2所示。

表2 LCD原始控制指令

LCD的显示画面按8行为一页的方式进行划分,共64行分成8页。LCD具有列循环寻址功能,如果第一步设定了页地址和列地址,那么以后每次向LCD写入显示数据,列地址计数器就自动加一。除非再设定列地址,否则列地址就一直累加下去,直到63。这样就简化了写入工作。

考虑到实际应用方便,可把一些常用的操作按指令的方式编码。所得到的DSP控制指令如下:

控制显示器开关:0010 0000 1111 111x

指定显示起始行:0100 0000 11xx xxxx

指定列地址和页地址:0110 0yyy yyyy yxxxy:

列地址(0~191)x:

行地址写入数据:1000 0000 xxxx xxxx

读显示器状态:1010 0000 0000 0000

读显示数据:1100 0000 0000 0000

框图中微指令ROM在接口控制中起着决定性的作用,每条指令的执行都被看作一系列单步时序操作的集合。如果从ROM的某一地址开始依次读出ROM里的数据,那么在每一个数据位上就会出现随时间变化的电平跳变。这样就可以用它作为控制信号进行控制操作。由于ROM是并行输出的,如果用不同的数据位代表不同的控制信号线,就能很容量地实现各个信号线之间的同步操作。这样就能很容易形成时序图中的时序逻辑,而且扩展方便。在上述的指令表示中,通过对高3位进行译码,可以得到ROM寻址时的起始地址。ROM各个数据位的含义如下:

[table][/table] 其中,低七位是控制LCD的接口线,FREE是微程序执行完标志,每条指令所对应的微程序分为招待状态(有多条微指令,FREE位为0)和闲置状态(一条指令,FREE位为1)。当指令执行状态机检测到FREE位的上跳沿时,加载下一条指令。LD是数字寄存器从DSP获得数据时的加载信号,微程序执行过程中,在某些指令执行时需要加载数据,可由该信号完成。RD是数据寄存器从LCD读入数据的加载信号,主要完成从LCD读入数据。

取指控制逻辑主要功能是根据FIFO的状态决定是否写入新的指令以及根据执行状态机的状态读入新的指令,填写状态寄存器,给出中断信号。

根据上述硬件设计,DSP的软件设计就大大简化了。以写入数据为例,在写入数据前先查询一下接口模块的状态,如果可以写入就写入数据;否则保持现有数据指针,等待下次写入。一读一写两次外部I/O操作,如果按7个等待周期、主频100MHz计算,只有140ns,加上判断所需时间,200ns内就可以完成写入数据。这里,7个等待周期是考虑到系统内还其它器件。如果只是对该接口模块操作,两三个等待周期是没有问题的。这样,100ns内就可完成写入数据。

在实际应用中,采用上述接口控制模块来完成LCD控制大大减轻了DSP的压力。推而广泛,这种方法还可以应用在其它慢速设备上,如打印机等,对于提高系统效率是比较有效的。需要指出的是,尽管这种方法能够建立双向快速通道,却是以占用可编程器件有限的资源为代价的。但是随着目前可编程器件容量的日益扩大,这个问题已不是很突出的了。

-

dsp

+关注

关注

553文章

8014浏览量

349191 -

FPGA

+关注

关注

1629文章

21748浏览量

603984 -

寄存器

+关注

关注

31文章

5356浏览量

120559

发布评论请先 登录

相关推荐

在高清晰LCD HDTV 中使用Cyclone III FPGA

基于DSP+FPGA多视频通道的切换控

DSP与FPGA之间的通信如何实现

采用FPGA实现直接数字频率合成器设计

如何利用DSP和FPGA技术检测低信噪比雷达信号?

实现CAN与串口UART之间的双向数据智能转换

利用Mentor高层次综合技术快速实现复杂DSP算法

基于DSP和FPGA的HDLC协议通讯电路设计

利用FPGA和DSP结合实现雷达多目标实时检测

TI中基于DSP和FPGA的三电平逆变器快速控制方法

微软面向Windows 10快速通道推送更新 默认应用配置界面新增搜索功能

在FPGA和DSP两种处理器之间实现SRIO协议的方法

NanoEdge AI studio-创建智能产品的快速通道

利用FPGA技术实现DSP和LCD之间双向快速通道的设计

利用FPGA技术实现DSP和LCD之间双向快速通道的设计

评论