1、 概述

在WCDMA中,加扰就是用一个伪随机码序列对扩频码进行相乘,对信号进行加密。上行链路物理信道加扰的作用是区分用户,下行链路加扰可以区分小区和信道。WCDMA采用Gold码作为扩频序列的扰码。Gold由两个M序列相加而成,且容易产生、自相关性优良的优点。本文介绍下行扰码的生成过程和如何用FPGA的实现。采用Verlog硬件描述语言进行功能描述,在写信号的作用下,予付扰码初值,在时钟信号的作用下,产生下行扰码的I,Q序列。

2 、下行扰码的结构

下行链路有18比特的初始值,可产生218-1 = 262 143个扰码,标以号码0…262 142。但并不是所有的扰码都可用。扰码分为512组,每组包括1个基本扰码和15个辅助扰码。

基本扰码由码号为n=16*i的码组成,其中i=0…511。第i组辅助扰码由码号为16*i+k的码组成,其中k=1…15。

每个基本扰码和同一组内的15个辅助扰码有一一对应关系,第i个基本扰码对应于第i组扰码。

基本扰码组又分为64个扰码组,每个包括8个主扰码。第j个扰码组由基本扰码16*8*j+16*k组成,其中j=0.63;k=0.7。

每个小区有且仅有一个基本扰码。基本CCPCH和基本CPICH总是用基本扰码传送。其余的下行物理信道可以用基本扰码或伴随于此小区的基本扰码的辅助扰码发送。

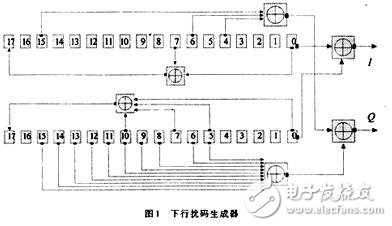

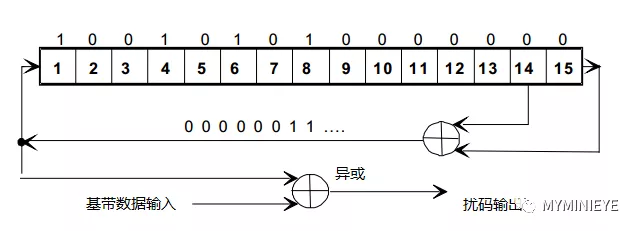

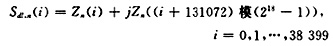

扰码序列通过把两个实数序列组合成一个复数序列生成。这两个实数序列都由两个生成多项式为18阶的 ,截断长度为38 400的m序列模2加生成。这样结果序列就由截断的Gold序列组成。扰码以10ms的无线帧为周期重复。用x和y分别表示这两个序列,x序列用本原多项式1+X7+X18(在GF(2)域上)生成;y序列由本原多项式1+X5+X7+ X10+X18生成。

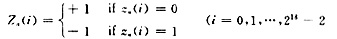

用zn表示由选定的扰码号n决定的序列,用x(i),y(i)和zn(i)分别表示序列x,y,和zn的第i个符号,m序列x和y生成方法如下:

初始状态:

序列符号的递归定义为:

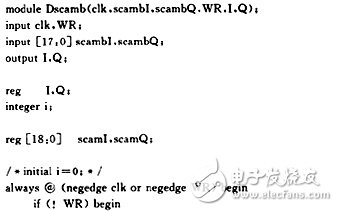

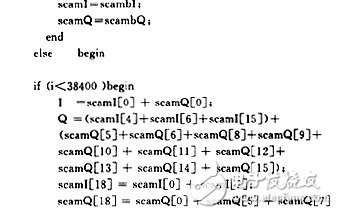

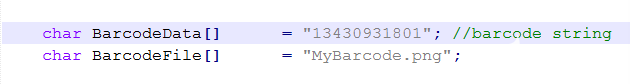

3 、生成代码

-

FPGA

+关注

关注

1625文章

21665浏览量

601767 -

硬件

+关注

关注

11文章

3251浏览量

66108

发布评论请先 登录

相关推荐

如何在FPGA内实现扰码过程

通信中扰码器与并行扰码器设计

[Mill]FPGA无线通信课程连载——扰码的原理及实现

无线通信中的扰码

Turbo码及交织技术在WCDMA的信道编码方案中的应用

浅析WCDMA下行发射分集技术

WCDMA下行专用物理信道的FPGA实现

在WCDMA中如何用FPGA生成下行扰码

在WCDMA中如何用FPGA生成下行扰码

评论