概述

E1是ITU-T制定并由欧洲邮政与电信协会(CEPT)命名的数字传输系统一次群(即PCM30)标准,由32个64kbps的PCM话路经过分时复用形成,其传输速率为2.048Mbps,其中30个话路传输语音等用户信息,另两个话路作为系统开销,传输同步码、信令码及其他辅助信号。E1接口的物理及电特性符合CCITT的G.703标准。我国也采用E1标准作为PCM系统和N-ISDN的基群。目前,建立在G.703基础上的E1接口在分组网、帧中继网、GSM移动基站及军事通信中得到广泛的应用,传送语音信号、数据、图像等业务。E1接口主要由线路接口单元和成帧器组成。本文介绍一种E1收发器芯片DS21Q59的基本原理及其在数字程控用户交换机中的应用。

DS21Q59的性能与特点

DS21Q59是美国MAXIM公司出品的单片四路E1收发器芯片,是一种优化的高密度E1线路终端。它包含四个由线路接口单元(LIU)和成帧器组成的完全独立的收发器,具备了连接四条E1线路所需的各种功能,并且还有一个TDM背板接口,用于在片内进行多路E1信号的交叉复用。该芯片是制作四路E1数字中继接口的极佳选择,可广泛用于路由器、复用器、接入设备、数字程控交换机及信道服务单元(CSU)与数据服务单元(DSU)中。

DS21Q59具有以下的性能及特点:

·有4个完整的E1收发器; ·远程及近程LIU,且接收灵敏度可调,最低为-43dB,最高为0dB;

·32/128位的无晶振抖动抑制器,用于消除时钟或数据的相位抖动;

· 片内的系统时钟合成器能够产生2.048MHz、4.096MHz、8.192MHz及16.384MHz等几种时钟,用于多路E1信号的交叉式PCM总线工作(IBO)方式;

·支持随路信令(CAS)和公共信道信令(CCS);

·接收通路有两帧容量的滑动缓冲存储器,用于消除接收数据与背板异步时钟之间的相位差和频率差;

·具备循环冗余校验(CRC)及伪随机序列(PRBS)的产生与检测功能;

·能够检测并产生远端告警及AIS告警;

·四个收发器具有独立的环回诊断能力,包括远端环回、本地环回与帧环回;

·多达59个寄存器可由用户根据使用情况进行相关配置;

·器件配置和功能实现可由外部处理器通过并口或SPI串口进行;

·附加的8根输出引脚(每个收发器2根)可由用户灵活配置使用;

·采用低功耗CMOS工艺,+3.3V单电源供电;

·封装形式采用100引脚的引线四边扁平塑料(LQFP)封装;

·符合ITU-T的G.703、G.704以及G.732等E1标准。

DS21Q59的基本工作原理

DS21Q59芯片主要集成了线路接口单元和成帧器功能,由外部的控制器或处理器通过串口或并口总线对芯片实施控制与功能配置。图1是DS21Q59内部功能框图(图中只画出了四个收发器中的一个)。“TSER1”是发送串行数据流的输入端,“RSER1”是接收串行数据流的输出端。

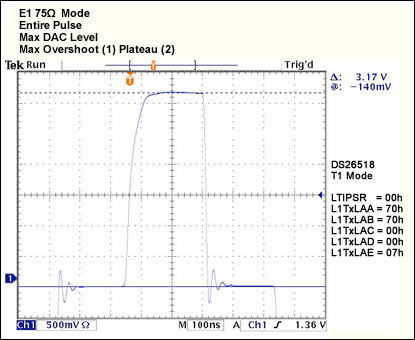

线路接口单元包括发送接口、接收接口和抖动抑制器,由“LICR”寄存器控制。发送数据时,发送成帧器提供E1传输所必须的帧和复帧数据开销,背板接口部分为成帧器提供时钟、数据和帧同步信号,由成帧器插入适当的帧同步码型和告警信息,并通过计算插入CRC码字,然后完成AMI和HDB3编码;最后利用一组经过激光修整的延迟线和一个精密的D/A转换器产生波形,发送到E1线路上去。波形的产生要根据使用的传输介质的情况,产生相应的驱动波形,分别用于75 的同轴电缆或120 的双绞线对传输。发送波形通常通过一个1:2的升压变压器耦合到同轴线或屏蔽的双绞线对上去。

接收时,E1波形从“RRING”和“RTIP”引脚进入芯片,首先进行时钟和数据恢复,经过抖动抑制器送到接收成帧器;接收成帧器完成对AMI和HDB3线路码的解码及数据流的同步,确定帧和复帧的码型,同时完成CRC码字的错误计数,检测接收到的AIS、同步丢失以及对端告警等各种告警信号,并为背板接口部分提供时钟、数据和帧同步信号。接收通路有两帧容量的滑动缓冲存储器,可通过“RCR”寄存器控制启用,用于消除接收数据与背板异步时钟“SYSCLK”之间的相位差和频率差。

用户通过设置“CCR5”寄存器的“IRTSEL”位(CCR5.4),即可实现DS21Q59芯片与75 或120 接收终端的匹配。也可以使用内部的终端功能,此时,外部终接电阻为120 (一般为两只60 电阻串联),将“IRTSEL”位置为“1”,使DS21Q59的内部电阻与外部电阻相并联,从而将端接电阻调整到75 。

每个收发器都有一个时钟与数据抖动抑制器,通过“LICR”寄存器的“JAS”位(即D3位),可以将其配置到发送通路中,也可以配置到接收通路中,用于从发送或接收信号中消除相位抖动。也可以选择不用此项功能。

“OUTA”和“OUTB”是用户选用输出口,根据需要可灵活配置。通过控制“OUTAC”寄存器,可以使OUTA口输出CMI码,用于直接驱动光接口。

寄存器SA1~SA16用于存储发送和接收信令。接收信令时,信令数据从接收的E1数据流TS16时隙取样得到,暂存到接收信令缓冲器,主机通过对SA1~SA16的读操作,得到信令数据。发送信令时,往SA1~SA16中写入数据,在控制寄存器“CCR6”的D3位为“1”时,将发送缓冲器的信令数据插入到发送数据流的TS16时隙中。

片内的系统时钟合成器能够产生2.048MHz、4.096MHz、8.192MHz及16.384MHz等频率的时钟,既为每个收发器提供时钟,还可以为多路E1信号的交叉总线(Interleave Bus Operation-简称IBO)方式提供时钟。以IBO方式工作时,每个收发器的接收缓冲存储器都必须启用,系统时钟合成器允许任意一条E1线路被选中作为系统的参考时钟源,16.384MHz的系统时钟支持最多8个E1数据流复用到单条高速PCM总线上(用两片DS21Q59实现),高速的PCM串行数据流?quot;TSER1“引脚输入、从”RSER1“输出。实现这个功能不需要附加其他的外部逻辑。这样,可以减少外部硬件,节省印刷板空间,并降低成本。

外部处理器通过对DS21Q59控制寄存器的操作完成芯片的初始化,即功能配置。DS21Q59的用户可用寄存器多达59个,分为控制寄存器、状态寄存器和数据寄存器等几类。状态寄存器用于存储E1线路的状态信息;而数据寄存器主要用于信令存储。

DS21Q59在数字程控交换机中的应用

DS21Q59适合作为程控交换机的数字中继接口,能够提供120路数字中继,它既支持中国1号信令,也支持国际7号信令。图2给出了一种在数字程控交换机上使用的电路连接框图。

本应用中,DS21Q59工作在IBO方式,这样可以减少背板的连线,使印制板布线简单。CPU的工作时钟为16.384MHz,DS21Q59芯片内合成器产生的8.192MHz时钟输出到各收发器的”SYSCLK“,既作为发送成帧器的时钟,又作为接收滑动缓冲器的时钟,片内的锁相环路能够保证收发时钟的同步。可编程芯片EPM7032为DS21Q59提供2.048MHz的主时钟MCLK,同时提供总线驱动和其他控制信号,并对输入输出的PCM信号进行驱动。信令使用中国1号信令,信令模块为MFC模块。由于DS21Q59本身不含HDLC协议控制器,若使用国际7号信令,需要外加HDLC协议控制器,进行HDLC协议管理。

-

芯片

+关注

关注

463文章

54443浏览量

469446 -

收发器

+关注

关注

10文章

3839浏览量

111463 -

交换机

+关注

关注

23文章

2933浏览量

104890

发布评论请先 登录

E1收发器DS2153Q的工作原理及应用

DS26518 T1/E1/J1收发器中的发射脉冲控制

E1收发器芯片DS21Q59的原理及交换机中的应用

E1收发器芯片DS21Q59的原理及交换机中的应用

评论