1、引 言

电子记帐控税终端机属于高度安全和可靠的产品,关系到信息安全和金融安全,长期使用国外的核心器件将给国家安全带来严重隐患。拥有自主知识产权的嵌入式处理器、专用芯片及其嵌入式操作系统已成为振兴我国电子行业的当务之急。

2、总体方案

本SoC芯片是面向电子记帐终端设备而设计的符合国家电子记帐终端设备标准的高性能嵌入式的系统芯片,其中以32位的SPARC V8架构的处理器为内核,集成了符合ISO7816标准的智能卡控制器和符合ISO7811/2标准的磁卡控制器接口等外围设备。他的应用既降低了电子记帐终端设备的成本,又大大提高了系统的可靠性。

2.1 SoC的结构

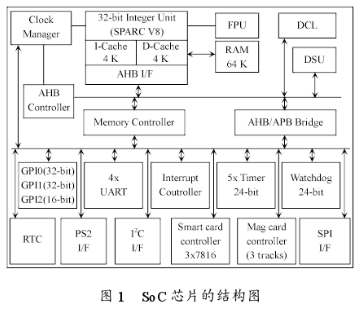

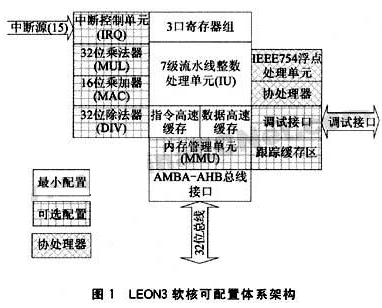

本SoC芯片内部采用可裁减的总线式结构,选用ARM公司的AMBA总线作为SoC内部总线,总线上各个模块采用统一的接口方式和总线连接,从而实现了模块开发的标准化,降低了开发的工作量。本SoC芯片的结构如图1所示。

本SoC采用“Harvard”结构,地址总线和数据总线分开,分别连接到独立的“cache”控制器上。指令cache和数据cache均为直接映射cache,配置各为4 kB;各部分的功能简述如下:

(1)32位整型数处理单元(Integer Unit,IU)支持SPARC V8指令集。IU的主要功能是执行整数运算、计算要访问的存储器的地址,另外他也支持指令计数器和控制指令的执行。

IU具有以下特点:

①5级单一指令流水;

②单独的指令cache和数据cache;

③标准的8个寄存器窗口;

④硬件乘法、除法器;

⑤带40位累加器的16×16位MAC;

(2)浮点运算单元(Floating Point Unit,FPU)提供遵循SPARC V8标准的全部浮点指令,其浮点数据的格式和浮点指令遵循ANSI/IEEE 754-1985标准,FPU连接在IU上。FPU有32个32 b的浮点寄存器。芯片使用标准的LD/ST指令在FPU和存储器之间移动数据。存储器地址由IU计算,浮点操作指令完成浮点算术运算。

内部的AMBA总线包括2种总线:AHB和APB。APB总线用来访问片内外设的寄存器;AHB总线用作高速数据传输。AHB总线连接处理器cache控制器和其他的高速单元,IU是总线上惟一的主控单元。AHB总线从属单元有:存储器控制器、AHB/APB转换桥等。AHB/APB转换桥作为一个从属设备连接在AHB总线上,是APB总线惟一的主控单元,处理器通过AHB/APB桥访问大部分片内外设。

(3)SoC的片上外设

智能卡控制器(Smartcard controller):符合ISO7816标准;

磁条卡控制(magnetic stripe card Controller):符合ISO7811/2标准;

通用输入输出接口(GPIO):共80个GPIO端口;

通用异步串口(UART):一个16550UART和3个普通UART;

中断控制器(Interrupt Controller):支持16个一级中断源,32个二级中断源;

定时器(Timer):5个24位的通用目的定时器;

看门狗(Watch Dog):24位看门狗定时器;

实时时钟(RTC):计算秒、分、小时、天、月、年,具有润月补偿功能,计时可至2100年,通过后备电源使实时时钟工作在低功率模式;

PS/2控制器(PS/2 I/F):符合PS/2标准,支持第一套和第二套扫描码集;

I2C控制器(I2C I/F):兼容Phillips公司的I2C标准;

SPI控制器(SPI I/F):兼容SPI和Microwire/Plus两个企业标准。

2.2 SoC芯片的设计要点

在SoC的体系架构、逻辑设计和电路设计中采用正向设计方法;

建立深亚微米自顶向下设计流程,实现硬/软件协同仿真、设计、验证技术,建立芯片正向设计平台;

低功耗设计技术,包括对RTC及SRAM的低功耗优化设计;

采用深亚微米(0.18μm)必须解决的设计问题,包括。EMI,CrOSS talk,天线效应和热电子效应等;

采用现代SoC设计技术,实现片上外设包括IC卡、磁卡、I2C、SPI、PS/2等功能接口的高度集成设计和测试;

高可靠、实时多任务处理平台技术,支持嵌入式操作系统及其任务调度管理;

支持ANSIC的标准应用,实现底层驱动软件的模块化、标准化设计。

同时,针对以上技术挑战必须实现如下技术创新:

该项目为自主知识产权的内嵌32位RISC处理器以及大量功能接口模块的SoC设计,突破嵌入式SoC的高度集成、高可靠、低功耗、实时多任务处理等关键技术;

建立自顶向下的深亚微米设计流程,实现硬、软件协同设计、仿真、综合、验证技术;采用大容量FPGA和嵌入式操作系的统功能验证平台;应用样机对SoC进行全面验证,确保了该项目的技术路线实施及产品的实际应用;

支持多任务实时嵌入式操作系统。

3、功能验证

在集成电路的设计过程中,需要进行大量的验证工作,SoC功能验证采用专门的开发软件把设计模型转换成相应的配置文件,下载到硬件平台的FPGA或CPLD芯片中,在实际的应用系统中来验证SoC功能的正确性。

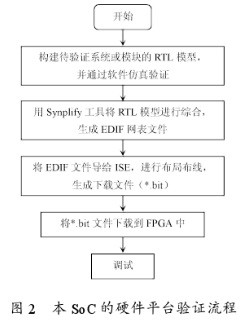

在对本SoC进行硬件平台验证过程中,采用的FPGA综合工具是Synplicity公司的Synplify Pro 7.7,FPGA布线工具选用的是Xilinx公司的ISE 5.0,硬件平台的核心FPGA芯片选用的是Xilinx公司的Virtex II系列的XC2V2000。验证流程如图2所示。

3.1 验证平台的设计

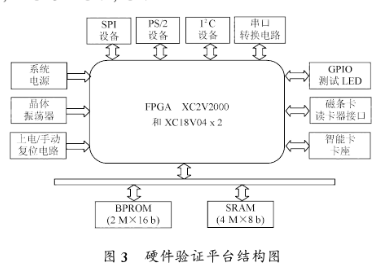

本SoC芯片内部采用AMBA总线,内嵌32 b整数处理单元,优化的32/64 b浮点数处理单元,并且内嵌了大量的外设,主要包括:80位GPIO口、4路UART控制器、5个24 b定时器、看门狗、.PS/2控制器、I2C总线控制器、SPI总线控制器、1个三磁道磁卡控制器,3个智能卡控制器等。为了完整地测试本SoC的所有功能,硬件测试平台如图3所示,包含下列基本组成部分:

FPGA芯片;配置PROM;程序BPROM;SRAM;串口转换芯片;I2C总线设备;SPI总线设备;磁卡读卡器接口;智能卡及卡座;GPIO测试点;PS/2设备;系统时钟发生设备;上电复位电路;电源。

3.2 FPGA平台验证结果

将由SoC的RTL模型产生的FPGA下载文件(*.bit文件)下载到FPGA中,在Unix环境下,用SPARC-GCC编译器编译测试程序(标准C程序),然后观察程序运行结果,就可以验证整个SoC系统或某一模块功能的正确性。

下面以获取智能卡复位应答(Answer To Reset,ATR)字节为例,阐述此过程。

事先知道待测智能卡的ATR字节为:3b,7a,18,0,0,21,8,11,12,13,14,15,16,17,18。

测试结果为:

Smartcard controller testing…

3b,7a,18,0,0,21,8,11,12,13,14,15,16,17,18

以上结果说明,智能卡控制器可以接收到卡的复位应答字节,SoC的此功能正确。采用同样的方法及过程可以验证其他功能的正确性。

4、结 语

该SoC芯片如今已经成功应用到了多种电子记帐终端设备中,为国内外的电子记帐终端设备制造商们提供了一种高性价比的选择,为“中国芯”家族又增添了一位新成员。所以,可以认为该SoC芯片的设计还是非常成功的。

设计中存在的主要问题就是内置的RAM空间还不够大,对于高端的电子记帐终端设备,必须外扩一定容量的RAM存储器,希望在下一款同类芯片设计中加以改进。

责任编辑:gt

-

处理器

+关注

关注

68文章

19313浏览量

230068 -

嵌入式

+关注

关注

5085文章

19138浏览量

305777 -

总线

+关注

关注

10文章

2888浏览量

88143

发布评论请先 登录

相关推荐

爱特梅尔推出SPARC V8处理器系列ATF697FF

欧空局为何从SPARC换成了RISC-V

云终端、瘦终端和胖终端三者之间有什么区别

Powerpc架构与X86架构的区别

在ARM64架构下为啥没有OpenJDK8的镜像

SPARC V8结构嵌入式微处理器的软件集成开发环境总体设计

Zen 3架构的移动处理器为何值得期待?

基于LEON开源微处理器IP软核实现SoC系统基本平台的构建

SPARC V8架构处理器应用于电子记帐终端设备中的探索分析

SPARC V8架构处理器应用于电子记帐终端设备中的探索分析

评论