引言

同步动态随机存储器(SDRAM),在同一个CPU时钟周期内即可完成数据的访问和刷新,其数据传输速度远远大于传统的数据存储器(DRAM),被广泛的应用于高速数据传输系统中。基于FPGA的SDRAM控制器,以其可靠性高、可移植性强、易于集成的特点,已逐渐取代了以往的专用控制器芯片而成为主流解决方案。然而,SDRAM复杂的控制逻辑和要求严格的时序,成为开发过程中困扰设计人员主要因素,进而降低了开发速度,而且大多数的基于FPGA的SDRAM控制器都是针对特定的SDRAM芯片进行设计,无法实现控制器的通用性。本文介绍一种通用SDRAM控制器的FPGA模块化解决方案。

SDRAM及其控制过程

SDRAM控制逻辑复杂,命令种类多样,需要周期性刷新操作、行列管理的等多重操作。

SDRAM首先要进行初始化操作。在上电后等待100ns,至少执行1条空操作,然后对所有页执行预充电操作,接着向各页发出两条刷新操作指令,最后执行SDRAM工作模式的设定LMR命令用来配置SDRAM工作模式寄存器。SDRAM工作寄存器可以根据具体应用的需要进行设置。

初始后的SDRAM在得到了RAS、CAS、WE的值后开始执行相应的命令。在对SDRAM进行读、写过程中,必须要先进行页激活ACT操作,保证存储单元是打开的,以便从中读取地址或者写入地址,然后通过预充电PHC命令实现来关闭存储单元。在进行写操作时,内部的列地址和数据都会被寄存,而进行读操作时,内部地址被寄存,数据的存储则发生在CAS 延迟时间(通常为1~3个时钟周期)后。最后,操作终止:当SDRAM顺次的进行读、写操作后,当到达到突发长度或者突发终止指令BT出现时,SDRAM将终止其操作。

模块化的SDRAM控制器设计

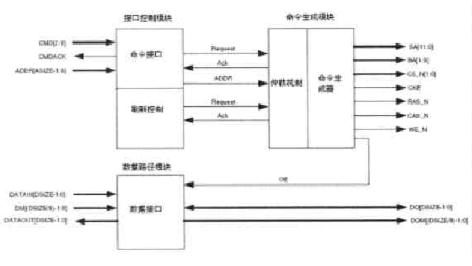

在SDRAM控制器的FPGA实现方案中,采用了FPGA的自底向上的模块化设计思想,首先分析顶层模块的功能,再将其功能分类细化,分配到不同的子模块去实现,然后自底向上的先逐步完成各个子模块的设计,最后将子模块相互连接生成顶层模块。经过分析,SDRAM控制器应实现的功能有:为SDRAM提供刷新控制以保持SDRAM中的数据;对主机的命令进行仲裁,将下一步要执行的命令翻译成可与SDRAM连接的信号;为SDRAM的读、写生成数据路径。因此,根据SDRAM的指令操作特点将SDRAM控制器划分为接口控制模块、命令生成模块和数据路径模块三个主要模块(图1)。

图1 SDRAM控制器的FPGA模块化设计方案

下面,对其接口信号进行介绍,需要注意的是,为了实现该控制器的通用性,ADDR、DATAIN、DATAOUT、DQ、DOM信号设计成可根据SDRAM的容量改变的形式。

与主机接口信号:CLK(系统时钟);RESET(系统复位);CMD[2:0](译码指令);CMDACK(指令应答信号);ADDR[ASIZE-1:0](地址线);DATAIN/DATAOU[DSIZE-1:0](输入、输出数据总线);DM[(DSIZE/8)-1:0](数据掩码)。

与SDRAM接口信号:SA(地址线);BA(页地址);CS_N(片选信号);CKE(时钟使能信号);RAS、CAS、WE(命令控制信号);DQM[(DSIZE/8)-1:0](SDRAM数据掩码);DQ[DSIZE-1:0](双向数据线)。

各个模块的设计与实现

接口控制模块

接口控制模块主要实现的功能是将CMD[2:0]翻译成接口指令和对刷新计数器的控制指令。接口模块在工作过程中首先通过要通过状态机来完成对CMD[2:0]的翻译。在VHDL程序中声明一个用户自定义类型states,根据CMD[2:0]输入来决定状态的转移,完成对CMD[2:0]的解码,部分代码如下:

type states is(nop,reada,writea,refresh,

precharge,load_mode);

signal state : states ;

………………

case cmd is

when “011” =》 state《=refresh;

when “111” =》 state《=nop;

………………

另外,SDRAM需要周期性刷新操作以保持数据。在模块的程序设计中,刷新周期的控制通过一个计数器来完成,到达规定的计数周期数时,接口模块通过REF_REQ信号向SDRAM发出刷新请求。直到SDRAM完成刷新操作,发出REF_ACK刷新应答信号,计数器才重新赋值,开始下一次的计数。

命令生成模块

命令生成模块实现对输入的SDRAM指令请求进行仲裁判断的功能,并将仲裁后要执行的指令解码成SDRAM需要的RAS、CAS等信号,从而实现指令对SDRAM的控制。仲裁机制是SDRAM控制器设计不可或缺的一个环节。仲裁机制实现要遵循如下规则:

*SDRAM在每一刻只有一个指令在执行;

*先到的指令先执行,如果刷新请求到来时,其它命令正在执行中,要等到当前命令执行完成后,才能执行刷新指令;

*其它指令和刷新请求同时到来时刷新操作先执行。

经过仲裁判断后,指令将传入命令生成器。命令生成器不仅要把指令解码成SDRAM需要的RAS、CAS等信号,同时还要对命令执行的时间进行控制。下面的例程仅供参考。

if (do_state=refresh or do_state=reada or

do_state=writea

or do_state=precharge or

do_state=load_mode)then

command_delay(7 downto

0)《=“11111111”;

------移位寄存器初值

command_done《=‘1’;

………………

else

command_done《=command_delay(0);

移位操作

command_delay(6 downto 0)《=

command_delay(7 downto 1);

command_delay(7)《=‘0’;

end if;

下面介绍输入的指令为writea和reada指令时模块所进行的操作。当SDRAM的writea和reada指令到来时,将引发一系列指令的执行,和其它指令相比需要更多的附加时间。所以,在这种情况下需要声明第二个移位寄存器rw_shift来完成这两个指令的附加时间的实现。rw_shift的工作原理和第一个移位寄存器command_delay是一样的,需根据读、写的时间决定rw_shift的位数。

最后一个移位寄存器oe_shift用来为数据通道生成数据输入、输出使能信号oe。对于非页模式的读写来说,oe保持有效的时间取决于突发长度,需要注意的是,读操作时,oe有效的起始时间取决于CAS延时时间,而对于写操作,则在写指令开始时oe就是有效的。

数据路径模块

数据路径模块的作用是在writea和reada命令期间生成数据的路径。在用VHDL语言程序中,用简单的赋值语句就可以实现数据路径模块。

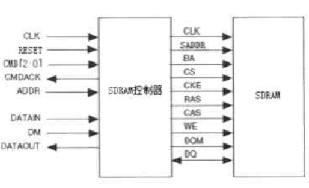

通用性的实现

根据SDRAM控制器的FPGA模块化设计方案生成的FPGA控制器易于修改和扩展,具有可通用的特性。在具体的应用中,针对不同的SDRAM,并不需要更改SDRAM控制器结构,只要根据datasheet中的SDRAM的容量将地址线数和数据的位数做相应修改,再依据SDRAM的时序和读、写速度更改接口控制模块中的时间信号的周期,如刷新周期、命令生成模块中移位寄存器的位数和初值等,这样就可以对不同的SDRAM进行控制。最后,生成的SDRAM控制器顶层模块如图2所示。为了证明该控制器设计方案的可行性和通用性,在Altera公司的Cyclone系列FPGA——EP1C6Q240C8中生成SDRAM控制器,根据数据手册中SDRAM的参数对控制器各模块的VHDL语言程序做相应的改动,实现了对三星公司的8MByte SDRAM K4S641632E和2MByte SDRAM K4S161622D的控制,均达到了100MHz的读、写速度。

图2 SDRAM控制器接口

结语

本方案采用的模块化思想为SDRAM控制器的开发提供了一种层次分明、易于扩展的设计思路。实验结果表明,该控制器设计紧凑,维护升级方便,易于实现对SDRAM的通用化控制,这无疑将极大的提高SDRAM应用的开发速度。

责任编辑:gt

-

控制器

+关注

关注

114文章

17909浏览量

195723 -

SDRAM

+关注

关注

7文章

460浏览量

57892 -

FPG

+关注

关注

1文章

54浏览量

80605

发布评论请先 登录

如何使用Verilog实现基于FPGA的SDRAM控制器?

SDRAM控制器的设备与VHDL实现

使用Verilog实现基于FPGA的SDRAM控制器

SDRAM控制器的设计

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文

DDR SDRAM控制器的设计与实现

基于FPGA的DDR3SDRAM控制器设计及实现简介

基于FPGA的DDR3SDRAM控制器设计及实现

基于SDRAM控制器实现FPGA模块化和通用性的解决方案设计

基于SDRAM控制器实现FPGA模块化和通用性的解决方案设计

评论