引言

SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCLK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。Altera公司的EDA设计工具中有自带的SPI总线控制IP核,但目前介绍该IP核具体应用的文献不多,本文结合我们在微投影系统研究中的需求,给出了该SPI IP核的应用实例。

1、 SPI核的工作原理

1.1 硬件结构

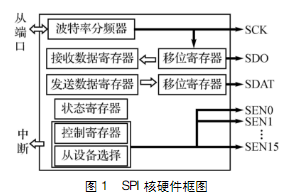

SPI核的硬件结构如图1所示,主要由波特率分频器、发送数据寄存器、接收数据寄存器、状态寄存器和控制寄存器组成。波特率分频器主要将Avalon的系统时钟进行分频,SCK可以配置的频率=Avalon系统时钟频率/(2的倍数)。

该IP核可以配置为主和从两种模式。本设计为嵌入在FPGA中SPI核为主工作模式,可以控制最多16个从设备,如图1所示的SEN0~SENl5。只有一个器件时,默认为SEN0信号。SPI核传输的数据宽度是由用户配置的,可在1~32位之间,当一次数据传输结束之后SPI核发出一个中断请求。

主要实现两种传输逻辑(以主模式为例):

①发送逻辑。待发送的数据由Avalon从端口送入发送数据寄存器,再移入移位寄存器中,SCK跳变沿到来时开始数据传输(经SDAT信号线发出,先移入的数据是高位还是低位,取决于SOPC Builder的配置)。

②接收逻辑。移位寄存器捕获到完整的数据后,再将其移入接收数据寄存器中(由SDO信号线捕获数据)。

1.2 软件结构

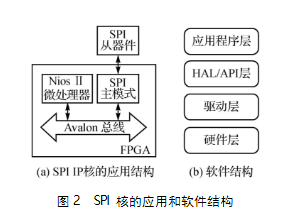

目前,在采用32位的软核Nios II处理器中,提供了4层软件开发模式:Nios II系统硬件,驱动程序层,硬件抽象层应用程序接口(HAL API),应用程序层。SPI核的应用和软件结构如图2所示。

2 、SPI核的库函数及其使用

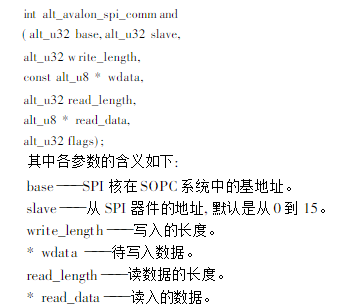

该IP核的APl函数为alt_avalon_spi_command(),其原型为:

flags——置1时表示执行完该函数后,SS_N保持写/读操作相同的电平;置0时表示执行完该函数后,SS_N为写/读操作相反的电平。

alt u8、alt u32分别是Altera系统中定义的8位、32位无符号数。

3、应用实例

微投影光机得以量产化以来,其所应用的相关技术也越受关注。这些技术可按照显示元件的不同约分为三大类别,一为德州仪器(TI)所主导的DLP;二为以3M为代表的LCOS;三为以Microvision 为主导的MEMS激光扫描。

本设计使用的是镁光公司的MT7DPWV2F铁电硅基液晶(FLCOS),FLCOS比一般的LCOS在色彩对比度、液晶像素响应时间方面更为出色。该芯片的主要参数:像素分辨率为852×480,颜色深度24位,对比度300:1,光学镜面反射率63%,尺寸23.4mm×9.8 mm×3.6 mm,功耗仅为75 mW。

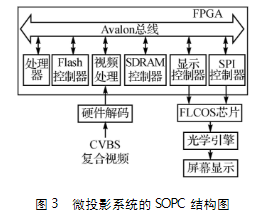

图3为微投影系统视频处理与控制SOPC系统示意图,总线上挂接了包括微处理器、Flash控制器、SDRAM控制器等。复合视频信号经过硬件解码后进入视频处理模块(完成去隔行处理、色空间转换等功能),SPI控制器模块和显示控制器模块一起控制片外的FLCOS芯片。FLCOS产生的图像经过光学引擎放大,投影到屏幕上面来。

该FLCOS芯片有数十个可配置的内部寄存器,根据具体应用的需求,有4个寄存器是必须初始化配置的。

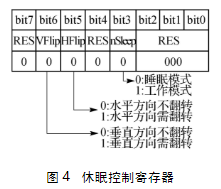

①休眠控制寄存器(地址为0x06)。如图4所示,该寄存器默认值为00H,需要将bit3位改为1,芯片才能从睡眠模式进入工作模式。

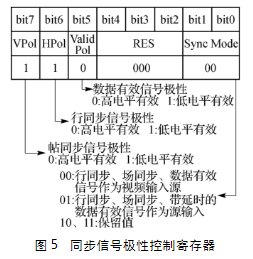

②同步信号极性控制寄存器(地址为0x02)。如图5所示,该寄存器默认值为C0h,将其bit7、bit6两位改为0,以符合显示时序控制器同步信号高电平有效的时序要求。

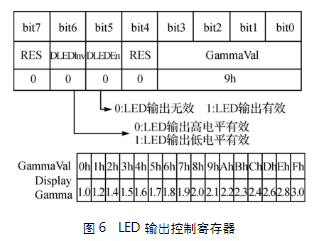

③LED输出控制寄存器(地址为0x05)。如图6所示,该寄存器默认值为09h,需要将bit5、bit6改为1,从而芯片能发出高电平有效的LED驱动信号,bit3到bit0默认为9h表示图像的伽马值为2.1。

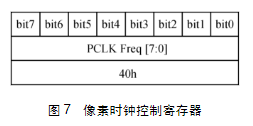

④像素时钟控制寄存器(地址为0x0f)。如图7所示,默认值为40h,该寄存器需要配置为像素时钟大小的2倍。由于本设计使用的像素时钟为27 MHz,27×2=54,转为十六进制数即为36h。

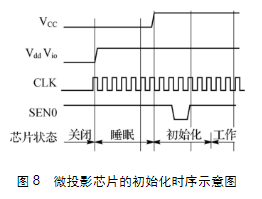

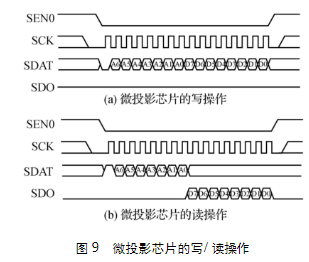

FLCOS芯片的初始化过程如图8所示。上电后,芯片进入睡眠状态,就需要对芯片进行SPI初始化配置,即对微投影寄存器进行写操作,其时序如图9所示。读操作时要求器件地址(共8位)的最高位为1,写操作时要求器件地址(共8位)的最高位为0。

作为SPI验证的例子,先向微投影芯片地址为0x06的存储单元写入数据0x08后再从中读出,并通过QuartusII内嵌的SignalTap II逻辑分析工具捕获如下信号,依次为SPI片选信号SEN0、时钟信号SCK和数据信号SDAT、SD0。结果显示,所得到的这一写入、读出过程时序与图9要求的芯片写入、读出时序一致。

芯片的初始化代码如下:

4、结语

SPI IP核作为自定义组件加载到SOPC系统中,应用于微投影芯片上并实现其初始化。SPI接口十分广泛,本文着重讲解了如何配置芯片的寄存器使其工作,并通过实例清楚的阐述,实验表明该IP核配置灵活,便于移植。

责任编辑:gt

-

驱动器

+关注

关注

53文章

8256浏览量

146584 -

控制器

+关注

关注

112文章

16396浏览量

178486 -

总线

+关注

关注

10文章

2891浏览量

88162

发布评论请先 登录

相关推荐

基于SPI总线控制器IP核的硬件结构及实现微投影系统的设计

基于SPI总线控制器IP核的硬件结构及实现微投影系统的设计

评论