引言

近年来,为了提高信息传输速率,增强通信抗干扰能力,飞行器测控通信系统已从统一载波体制向扩频统一测控通信体制发展。但是,这种宽带扩频测控技术的应用使得同步设计成为系统实现的难点,尤其对于多频率源系统,信号之间的严格同步更为困难。一般情况下,为了获得多路DDS的同步,设计者往往会使用多种手段对参考时钟、数据刷新、锁相倍频等步骤小心处理,这样不但耗费了大量的精力物力,而且效果往往不尽如人意。

美国ADI公司推出的高性能4通道直接数字式频率合成器AD9959,在单芯片上集成了4个独立的DDS核,通过一个公用参考频率内部同步4个DDS通道,避免了多个DDS同步过程中由于器件特性差异造成同步困难的问题,在降低同步设计难度的同时,还提供了灵活的控制能力。

AD9959

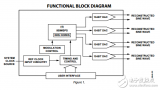

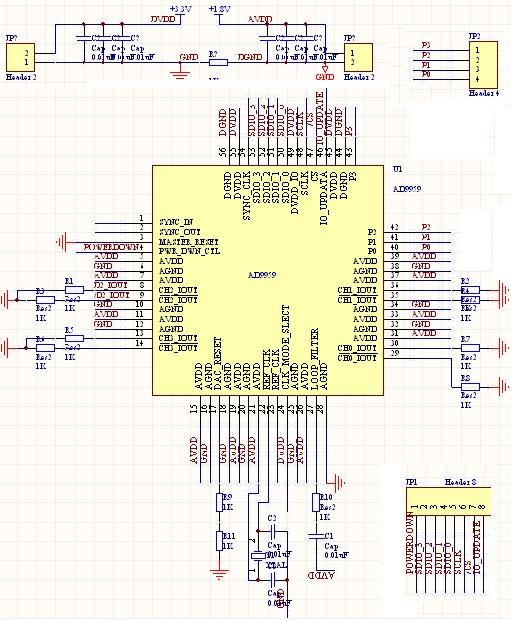

AD9959是美国ADI公司的多通道DDS器件,内部包含4个同步的10bit 500MHz DDS。每个DDS通道拥有独立的32bit频率分辨率控制、14bit相位偏移控制及10bit 输出幅度控制,输出经过10bit DAC转化为标准正弦信号。采用这种独立控制方式便于校正模拟滤波、放大或PCB布线引起的I/Q信号失配。AD9959拥有16级幅度、频率或相位调制(ASK、FSK、PSK),支持线性扫频、扫相、扫幅等功能,具有良好的宽带、窄带无杂散噪声(SFDR)性能。高速串行I/O端口兼容早期ADI DDS产品的SPI串行通信方式,通过4个串行数据引脚SDIO[3..0]可方便对芯片进行编程操作,具有良好的多通道同步性能。亦可采用菊花链方式用一个主控芯片(DSP或FPGA)同步多个AD9959器件以获得更多同步DDS通道。

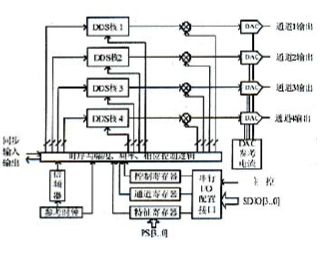

AD9959内部结构如图1所示。

图1 AD9959内部结构

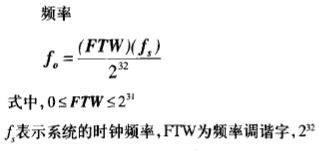

AD9959内部的每个DDS通道都拥有独立的32bit相位累加器和相位-幅度转换器。当相位累加开始计时并且相位增量(频率调谐字FTW)大于0时,相位累加器的输出数据作为波形存储器的取样地址,输出数字化的正弦波形(梯形正弦波)。相位-幅度装换器同时将相位信息通过运算转化为幅度信息。每个通道的输出频率(fo)是相位累加器翻转率的函数。频率、相位及幅度关系由下面的公式表示:

AD9959具有多种工作模式:单频(Single Tone)、调制(Modulation)和线扫(Linear Sweep)3种模式。

AD9959串行1/O提供多种配置工作方式,串口兼容ADI早期DDS采用的SPI串行方式。

AD9959的运行是主控芯片(单片机、DSP或可编程逻辑)通过串行I/O改写其内部寄存器值来实现的。因此,寄存器是AD9959的控制核心。控制寄存器主要完成通道选择,多设备同步及相位累加器清零等功能;通道控制寄存器主要完成各通道功能的选择,频率、相位、幅度的设置。各寄存器的使用是通过不同地址的8位数据值来决定。

AD9959在测控通信系统中的应用

多进制正交扩频信号产生

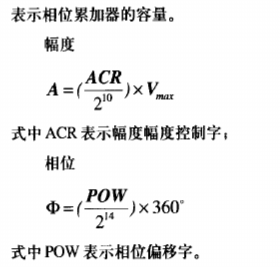

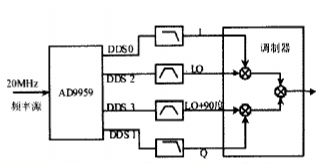

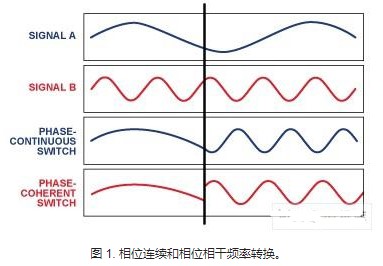

在测控通信系统的设计中系统的可靠性尤为重要,特别是同步不好轻则误码率高,重则系统无法正常工作。如图2所示,在以往的设计中,要成功地同步各路DDS首先要将参考时钟的相位差最小化,且时钟边沿要足够的陡,以免增加时钟的相位误差。其次,数据刷新时钟(I/O _Update)决定了DDS内部寄存器值的改变时间,多路DDS必须同步改变工作寄存器的值。再次,DDS所需频率由频率源经过倍频锁相后提供,但这样会带来倍频锁相后时间信号相位延迟等问题。此外,由于滤波器特性的不一致,也往往会造成已经同步的DDS输出信号经过滤波平滑处理后进入调制器的信号却发生失配。因此需要不断地对FPGA中的控制时序做反复调整。但由于器件之间的差异性与温度特定的不同,调整好的时序控制程序往往不适用于另一个同样的电路。诸多因素为信号同步带来很多麻烦。

图2 原正交扩频信号产生方案

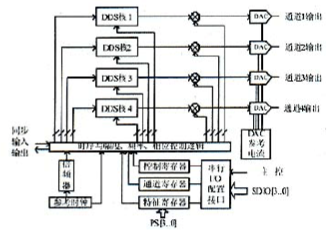

在新方案中,由于单片AD9959集成了4个DDS通道,无需4片AD9852及其外部电路,大大减小了PCB面积。单片AD9959由一组共享的参考时钟频率在内部同步4个独立的DDS通道,在线可编程的通道控制信号随时调整由外部路径产生的不均衡性。I、Q数据流可实现良好的正交。即时正交关系和幅度匹配发生轻微的变化,由于其14bit的相位调整和32bit的幅度调整,误差将保持在很小的可容许的范围内。上电后FPGA从配置芯片中加载程序,完成发送时序及系统的控制,PN码和Walsh函数的产生也是由FPGA实现。在FPGA的控制下,4路DDS输出同步正交信号到专用调制芯片,可产生QPSK、16QAM等多种调制信号,各项指标满足系统要求,性能稳定。

基于正交信号的上变频

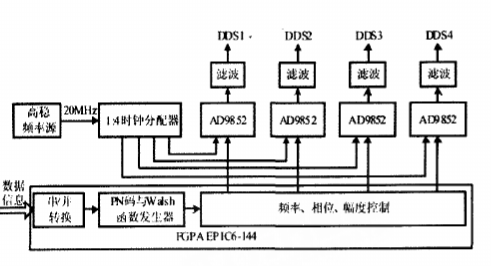

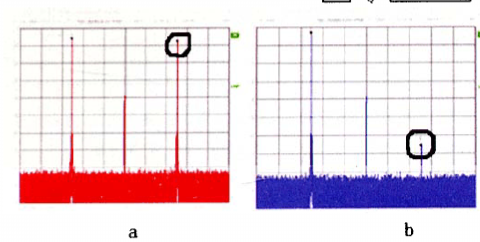

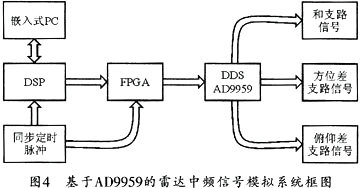

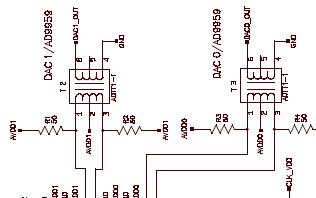

如图3所示,虽然DDS具有良好的频率特性和相位特定,但在测控通信系统中设备往往工作在VHF、UHF、L/S/C等频率较高的频段,而DDS无法直接满足UHF频段以上的频率要求,必须进行上变频。通常用锁相环(PLL)反馈环路中的DDS进行上变频,但受到PLL的锁定时间及带宽的影响,这种方式不适合频率高速变化的场合。此时,采用AD9959,对两个正交的DDS通道进行单边带上变频,其中两路DDS作为I/Q通路,另两路DDS作为相位相差90度的本振信号源,这种方法非常适合快速跳频系统,不但保证了本振与I/Q数据的同步而且有效地抑止了冗余边带的产生。由于冗余边带的显著减小,滤波器设计难度也大大降低。图4 比较了采用DDS正交上变频方案与PLL上变频的冗余边带抑制能力。

图3 DDS单边带抑制载波上变频

图4 a 没有采用正交上变频的单音频谱

b 采用DDS正交上变频的单音频谱

结语

以4通道DDS芯片AD9959为核心的测控通信电路已应用于某无人机测控通信系统中,无论是正交扩频中还是DDS上变频都有出色的性能表现。4个DDS核天生同步的特性不仅降低了系统的成本,减小了PCB面积,而且大大简化了系统同步设计的复杂度,缩短了研发周期。

责任编辑:gt

-

转换器

+关注

关注

27文章

8741浏览量

147712 -

分辨率

+关注

关注

2文章

1071浏览量

41993 -

DDS

+关注

关注

21文章

636浏览量

152834

发布评论请先 登录

相关推荐

AD9959控制时序问题

AD9959输出通道外接电路连接,请问AD9959输出端口外围电路如何设计?

请问AD9959 SYNC_CLK能实现输出信号同步吗

AD9959调试的相关资料分享

AD9959,pdf datasheet (4-Channe

ad9959应用控制电路

基于AD9959的高精度多通道雷达信号源设计

4通道500MSPS DDS 10位数模转换器AD9959数据表

利用AD9958/AD9959多通道DDS实现相位相干FSK调制器的设计

基于AD9959多通道DDS器件实现测控通信电路的设计及应用研究

基于AD9959多通道DDS器件实现测控通信电路的设计及应用研究

评论