基于DSP方案

目前的视频监控行业,基于DSP的H.264编码器解决方案占有绝对优势的市场份额,这是由DSP方案开发周期相对较短的特性决定的。在ASIC或FPGA方案仍处于研发阶段时,DSP方案已捷足先登,并较好地解决了视频监控行业中H.264编码器方案从无到有的过程,为H.264在监控应用中走向成熟立下了汗马功劳。但是由于DSP运算能力本身的制约,考虑到H.264标准实现的高复杂度,要达到未来对编码器高性价比的要求,DSP方案会非常困难。为从低码率的实时通信系统或无线环境到高码率的HDTV和数字存储系统提供一个优良的视频压缩编码通用工具。但H.264标准优异的性能表现是以编码运算复杂度和运算量大为代价,在通用的PC机平台实现会占用较大的CPU和内存资源。随着数字信号处理器(DSP)技术的高速发展,DSP的处理速度和能力飞速提高。同时,虽然DSP方案具有非常好的可编程性能,但由于其硬件接口和架构均已固定,很难满足产品架构灵活性的要求,也相对增加了灵活提供对多通道编码支持的实现难度。

基于ASIC方案

在目前阶段基于ASIC的H.264编码成熟方案在监控领域的应用还相对较少,这和芯片设计研发周期较长,成本较高的特点紧密相关。ASIC方案的最大优势就是一旦量产后,成本和其他方案相比将非常低廉,同时由于是硬件编码实现,通常可以较容易满足行业对高编码性能的要求。同时一款成熟的ASIC芯片和DSP实现方案相比通常具有更高的稳定性。监控市场相对多变的客户需求则使得建立在ASIC平台上的产品方案在未来有着更大的产品不确定性和市场风险。

基于FPGA方案

FPGA作为一个可编程的硬件逻辑实现平台很好地融合了DSP架构的可编程可升级性和ASIC架构的由硬件实现方式而带来的高编码性能。FGPA方案的灵活性不仅仅体现在具有和DSP平台一样的可编程性和可升级性,而且还体现在可以提供更高的系统架构上的灵活性。以XilinxSpartan3系列芯片为例,首先提供了不同规格能力的芯片选择,其次对于同一规格的芯片又提供了不同的封装,以提供不同的管脚数目的选择,同时,每一款FPGA芯片其管脚都可以根据用户的要求重新定义功能,提供非常灵活的接口控制。通过和系统设计的有效配合,基于FPGA的方案有可能大幅降低产品的BOM成本。FPGA这种架构上的灵活性非常有利于采用同一个H.264编码内核灵活支持不同应用、不同规格的产品方向。同时架构上的灵活性使得设计者可以充分发挥创造性,开发出个性化风格的产品,这是基于DSP或ASIC的方案难以做到的。

FPGA是现场编程门阵列器件。它和DSP集成在一块芯片上,可实现宽带信号处理,大大提高信号处理速度。据报道,Xilinx 公司的Virtex-II FPGA对快速傅立叶变换(FFT)的处理可提高30倍以上。它的芯片中有自由的FPGA可供编程。Xilinx公司开发出一种称作Turbo卷积编译码器的高性能内核。设计者可以在FPGA中集成一个或多个Turbo内核,它支持多路大数据流,以满足第三代(3G)WCDMA无线基站和手机的需要,同时大大WCDMA无线基站节省开发时间,使功能的增加或性能的改善非常容易。因此在无线通信、多媒体等领域将有广泛应用。

FPGA方案与前两种方案相比,其结合DSP方案和ASIC方案的部分优势,弥补一些固有不足。如FGPA方案的可编程可升级性能大大降低了系统集成商在选用ASIC芯片方案时可能会遇到的一些后期风险,同时FPGA接近ASIC的强运算能力则有效弥补了DSP方案在编码性能上的瓶颈。另一方面,FPGA类似于ASIC的实现方式也使得FPGA平台有可能提供比DSP方案更高的产品稳定性。

FPGA方案从产品角度来考量的话,最主要的难度是如何既考虑到产品的成本需要,又考虑其性能需求,为市场提供高性价比的编码解决方案。

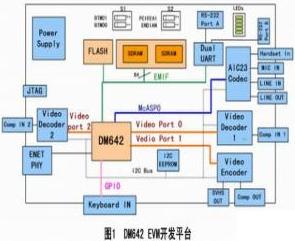

目前市场上针对以上三种产品平台的都已有成熟的编码器方案,其中基于DSP的主要是TI的DM642和DAVINCI媒体处理器,以及NXP的PNX15xx和PNX17xx。基于ASIC方案的相对较少,主要用的比较多的是海思的HI3510。基于FPGA的目前主要是XILINXSPARTAN3ADSP3400采用DVMICRO硬件IP核提供的编码器方案。

H.264在监控的应用

TOYA SDVR 7IV 是采用止前最为先进H.264视频压缩算法的专业数字监控产品,具有强大的视频/音频压缩引擎,与MPEG-4压缩方式的硬盘录像机相比,压缩比可提高近30%,大大提高了存储和网络传输带宽,同理采用新的算法极大地抑制了由于摄像机噪声导致的图像失真,背景流动现象,便图像质量更加清晰。H.264产品的推出无疑又使我国的数字监控技术上了一个新的台阶。

系统采用最先进的H264视频压缩技术和G。729的音频压缩技术,实现超大无损压缩。具备本地实时监视、音视频同步压缩存储、组合报警、有线或无线网络传输、管理权限设置等多种功能,单个本地系统可完成显示16路监控画面、每路可单独放大和切换,查询录象记录及进行回放。每个本地系统均可通过不同的网络方式组成有线或无线数字监控系统。

2 TOYA SDVR 7IV 系统主要特点:

采用时间最先进的H.264视频编码技术,具有高清晰度的画质;

在压缩处理过程中使用多种专用技术,保证以最低码流达到最佳画质,采用帧内压缩,绝无马赛克出现;

提供多种图象处理方法,加强噪音信号的过滤,画面更平滑。

可同时支持H.264、MPEG-4压缩格式;

实时压缩、实时预览、实时回放;

支持I\B\P帧多种组合/量化模式,图象压缩比更大;

在压缩过程中,可动态抽帧,可随时恢复,进一步减少存储空间;

预览、压缩不占用CPU时间,互不干扰;

可动态精确设置多种视音频压缩参数,达到最佳视听效果;

码流可调,占用硬盘空间最少可达40兆每小时;

工艺精良,结构稳定;低功耗,发热少,系统可靠性、稳定性高;

3 主要技术规格

压缩画面以及分辨,支持CIF/QCIF,图象分辨率352X288,图象压缩

压缩格式:支持H.264、MPEG-4压缩格式;

压缩帧率:1-25帧可调

压缩码率:64K~2Mbit/秒,支持CBR\VBR\Hybrid

三种码率控制方式:变码流、动码流、混合码流

网络传输

支持PSTN/DDN/LAN/WAN等网络远程传输与控制

每个服务器支持32路TCP/UDP传输,组播无限制

4系统功能

多画面分割:单路、四路、九路、十六路、全屏显示等多种画面分割;

采用录象方式;常规录象,动态录象,视频移动报警录象,定时录象;

字符/时间叠加功能:可以在每一路视频上叠加地点信息,便于查询;

多用户管理:可设置多级管理员权限;

工作日志:详细记录系统工作状态,方便用户管理;

报警:具有报警输入/输出功能,单独设置报警区域和灵敏度

图象亮度/对比度/色度/饱和度随时可调

支持G.729标准音频压缩,线性音频输入,音质好,占硬盘空间少

回放检索:根据时间、日期、摄象机编号分别回放检索

5 TOYA SDVR 7IV系统应用

技术的成熟和不断人性化的设计,使得本系统得以全方位进入金融、保险等特殊领域,而且在全能楼宇、文化教育、医学研究、交通指挥管制、在建工程管理、恶劣工况管理、海关及公、检、法商业贸易等诸多领域得到了广泛的应用。

-

处理器

+关注

关注

68文章

19293浏览量

229927 -

FPGA

+关注

关注

1629文章

21744浏览量

603595 -

编码器

+关注

关注

45文章

3645浏览量

134564

发布评论请先 登录

相关推荐

h.264编码器下载

H.264三大开源编码器的评测报告

H.264视频编码在DM642上的实现与优化

一种基于DSP平台的快速H.264编码算法的设计

基于ASIC的H.264编码器设计及其ADSP验证策略

基于TMS320DM642平台的H.264编码器优化

基于ADSP-BF561的H.264视频编码器的实现

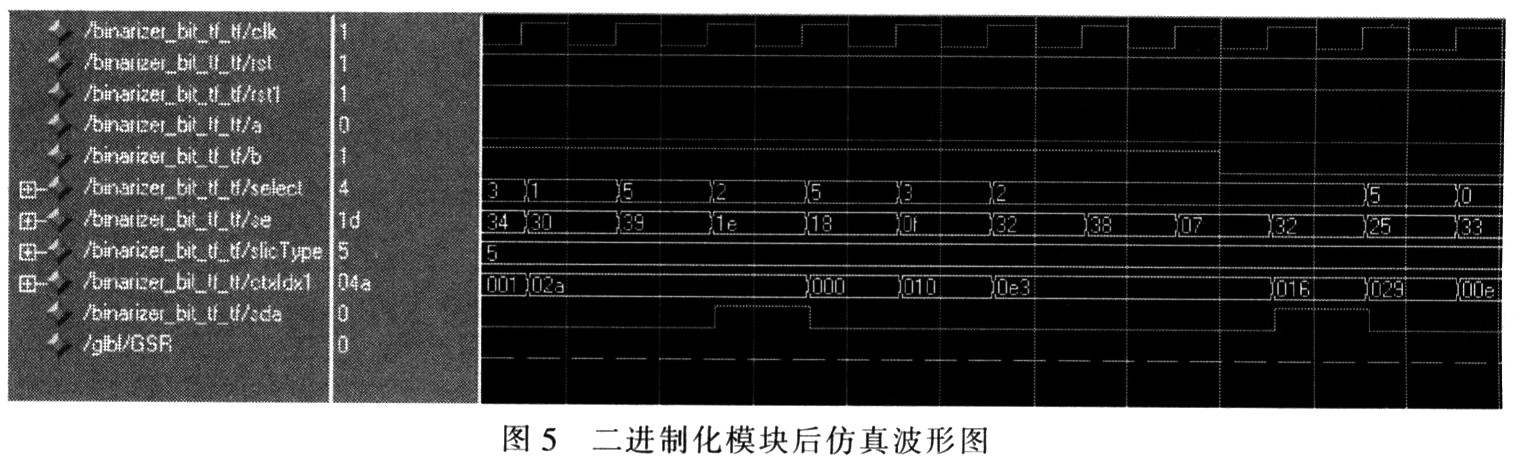

H.264中二进制化编码器的FPGA实现

Jointwave发布的H.264编码器可实现1080p

H.264视频编码器在DSP上的实现与优化

针对DSP、ASIC与FPGA三种产品平台的H.264编码器方案

针对DSP、ASIC与FPGA三种产品平台的H.264编码器方案

评论