差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计,什么另它这么倍受青睐呢?接下来本文对其在电路板中体现的优点进行讨论。

布线非常靠近的差分信号对相互之间也会互相紧密耦合,这种互相之间的耦合会减小EMI发射,所谓EMI即是Electro Magnetic Interference的缩写,有传导干扰和辐射干扰两种。传导干扰是指通过导电介质把一个电网络上的信号耦合(干扰)到另一个电网络。辐射干扰是指干扰源通过空间把其信号耦合(干扰)到另一个电网络。在高速PCB及系统设计中,高频信号线、集成电路的引脚、各类接插件等都可能成为具有天线特性的辐射干扰源,能发射电磁波并影响其他系统或本系统内其他子系统的正常工作。但是差分信号线的主要缺点是增加了PCB的面积,这是本文将讨论的另一个问题——介绍电路板设计过程中采用差分信号线布线的布线策略。

众所周知,信号存在沿信号线或者PCB线下面传输的特性,即便我们可能并不熟悉单端模式布线策略,单端这个术语将信号的这种传输特性与差模和共模种信号传输方式区别开来,后面这两种信号传输方式通常更为复杂。(顺便介绍单端这个术语,从严格意义上来讲,所有电压信号都是差分的,因为一个电压只能是相对于另一个电压而言的。在某些系统里,“系统地”被用作电压基准点。当“地”当作电压测量基准时,这种信号规划被称之为单端的。)

差分和共模方式

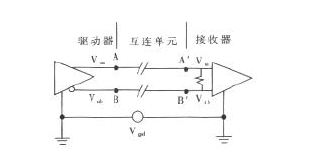

差模信号通过一对信号线来传输。一个信号线上传输我们通常所理解的信号;另一个信号线上则传输一个等值而方向相反(至少在理论上是这样)的信号。然后接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”。差分和单端模式最初出现时差异不大,因为所有的信号都存在回路。

单端模式的信号通常经由一个零电压的电路(或者称为地)来返回。差分信号中的每一个信号都要通过地电路来返回。由于每一个信号对实际上是等值而反向的,所以返回电路就简单地互相抵消了,因此在零电压或者是地电路上就不会出现差分信号返回的成分。

共模方式是指信号出现在一个(差分)信号线对的两个信号线上,或者是同时出现在单端信号线和地上。对这个概念的理解并不直观,因为很难想象如何产生这样的信号。这主要是因为通常我们并不生成共模信号的缘故。共模信号绝大多数都是根据假想情况在电路中产生或者由邻近的或外界的信号源耦合进来的噪声信号。共模信号几乎总是“有害的”,许多设计规则就是专为预防共模信号出现而设计的。

差分信号线的布线

一般来说(当然也有一些例外)差分信号也是高速信号,所以高速设计规则通常也都适用于差分信号的布线,特别是设计传输线1这样的信号线时更是如此。这就意味着我们必须非常谨慎地设计信号线的布线,以确保信号线的特征阻抗沿信号线各处连续并且保持一个常数。

对于 PCB工程师来说,最关注的还是如何确保在实际走线中能完全发挥差分走线的这些优势。在差分线对的布局布线过程中,我们希望差分线对中的两个PCB线完全一致,以保证两个差分信号时刻保持相反极性,减少共模分量及反射。这就意味着,在实际应用中应该尽最大的努力来确保差分线对中的PCB线具有完全一样的阻抗并且布线的长度也完全一致。差分PCB线通常总是成对布线,而且它们之间的距离沿线对的方向在任意位置都保持为一个常数不变。通常情况下,差分线对的布局布线总是尽可能地靠近。

差分信号的优势

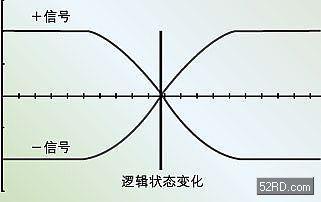

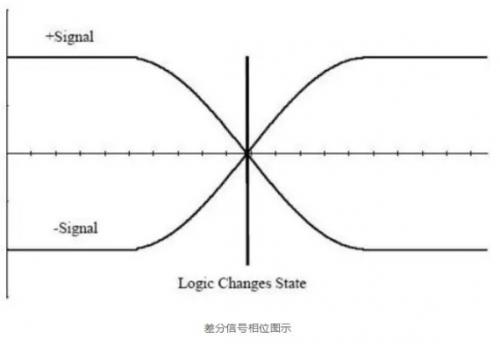

单端信号通常总是参照某种“参考”电平。这种“参考”电平可能是一个正值电压也可能是地电压、一个器件的阈值电压、或者是其它什么地方的另外一个信号。而另一方面差分信号则总是参照该差分线对中的另一方。也就是说,如果一个信号线(+信号)上的电压高于另一个信号线(-信号)上的电压,那么我们就可以得到一种逻辑状态;而如果前者低于后者那么我们就可以得到另外的一种逻辑状态,参见图1。

与单端信号相比,差分信号具有以下几个优点:

时序得到精确的定义,这是由于控制信号线对的交叉点要比控制信号相对于一个参考电平的绝对电压值来得简单。这也是需要精确实现差分线对等长布线的一个理由。如果信号不能同时到达差分线对的另一端的话,那么源端所能够提供的任何时序的控制都会大打折扣。此外,如果差分线对远端的信号并非严格意义上的等值而反向,那么就会出现共模噪声,所谓共模噪声,又称为非对称噪声或线路对地的噪声,在使用交流电源的电气设备的输入端(输电线和中线)都存在这种噪声,两者对地的相位保持相同。共模噪声的电流在两个输电线上以相同的方向流动并通过地线返回。共模噪声可以通过在电磁干扰滤波器中放置与每条输电线串联的电感,并在两个输电线和地之间使用Y电容进行连接,来予以抑制。而这将导致出现信号时序和EMI方面的问题。由于差分信号并不参照它们自身以外的任何信号,并且可以更加严格地控制信号交叉点的时序,所以差分电路同常规的单端信号电路相比通常可以以更高的速度工作。

由于差分电路的工作取决于两个信号线(它们的信号等值而反向)上信号之间的差值,同周围的噪声相比,得到的信号就是任何一个单端信号的两倍大小。所以,在其它所有情况都一样的条件下,差分信号能够很容易的识别小信号,总是具有更高的信噪比,因而提供更高的性能。

差分电路对于差分对上的信号电平之间的差异非常灵敏。但是相对于一些其它的参考(尤其是地)来说,它们对于差分线上的绝对电压值却不敏感。相对来说,差分电路对于类似地弹反射和其它可能存在于电源和地平面上的噪声信号等这样的问题是不敏感的,而对共模信号来说,它们则会完全一致地出现在每一条信号线上。

差分信号对EMI和信号之间的串扰耦合也具有一定的免疫能力。如果一对差分信号线对的布线非常紧凑,那么任何外部耦合的噪声都会相同程度地耦合到线对中的每一条信号线上,所以耦合的噪声就成为“共模”噪声,而差分信号电路对这种信号具有非常完美的免疫能力。如果线对是绞合在一起的(比如双绞线),那么信号线对耦合噪声的免疫能力会更强。由于不可能在PCB上很方便地实现差分信号的绞合,那么尽可能地将它们的布线靠近在一起就成为实际应用中一种非常好的办法。

布线非常靠近的差分信号对相互之间也会互相紧密耦合。这种互相之间的耦合会减小EMI发射,特别是同单端PCB信号线相比。可以这样想象,差分信号中每一条信号线对外的辐射是大小相等而方向相反,因此会相互抵消,就像信号在双绞线中的情况一样。差分信号在布线时靠得越近,相互之间的耦合也就越强,因而对外的EMI辐射也就越小。

若电路板的面积非常紧张,单端信号可以只有一根信号线,地线走地平面,而差分信号一定要走两根等长、等宽、紧密靠近、且在同一层面的线。因此差分电路的主要缺点就是增加了PCB线。所以,如果应用过程中不能发挥差分信号的优点的话,那么不值得增加PCB面积。但是如果设计出的电路性能方面有重大改进的话,那么增加的布线面积所付出的代价就是值得的。

本文总结

信号线的外在阻抗会由于差分信号线之间的互相耦合而受影响,因此必须采用终端匹配策略。差分阻抗的计算很困难,美国的国家半导体公司在这个领域提供了一些参考。Polar Instruments也提供一个独立的可以计算许多种不同的差分信号结构3的差分阻抗计算器(需要一些费用)。高端的设计工具包也可以计算差分阻抗。

但是要注意差分线之间的相互耦合将直接影响差分阻抗的计算。差分线之间的耦合必须保证沿整个差分线都保持为一个常数或者确保阻抗的连续性。这也是差分线之间必须保持“恒定间距”设计规则的原因。

-

集成电路

+关注

关注

5387文章

11530浏览量

361630 -

pcb

+关注

关注

4319文章

23080浏览量

397494 -

差分信号

+关注

关注

3文章

367浏览量

27676

发布评论请先 登录

相关推荐

基于差分信号的PCB布线优点和策略简析

差分信号线的原理和优缺点分析

在PCB板中进行差分信号线布线的优势分析

在PCB板中进行差分信号线布线的优势分析

评论