将近一半的嵌入式设计用到FPGA,仅次于微控制器。FPGA可用于执行任何胶合逻辑、自定义IP 、计算密集型算法加速器。通过采取一些处理任务, FPGA可以帮助提高系统性能,从而使单片机从周期密集的任务中腾出部分时间。FPGA还提供优良的性能特点和更的灵活性,以适应不断变化的标准。

基于FPGA的MCU设计有两种基本实现方式:一种是在FPGA逻辑结构中内置MCU软核;一种是使用基于离散FPGA的标准MCU产品。FPGA内置软核有效果,但与标准MCU相比,该方式实现一个微控制器是比较昂贵和耗电的。尤其是使用基于32位ARM的内核。结果,基于FPGA内置软核的FPGA MCU设计只占三分之一。其余的三分之二是基于离散FPGA的标准微控制器产品。

标准微控制器产品和FPGA都没有有效的发展两者之间的通信,甚至使用不同的语言。因此,它们之间的接口将是一种挑战。FPGA的没有任何专门的逻辑电路来与微控制器通讯。首先,这种逻辑模块的设计必须从零开始。其次,微控制器和FPGA之间的通信是异步的。特别是需要使单片机与FPGA时钟域同步。最后,无论是接口,还是微控制器总线,都存在瓶颈问题。MCU和FPGA之间的信息传递通常需要在MCU总线上循环,且通常占用资源(PIO or EBI)影响传递速度。因此必须注意避免与外部SRAM或闪存和微控制器总线的瓶颈问题。

MCU的FPGA接口基本上有三种硬件选择:可编程的I / O(PIO);外部总线接口( EBI的),如果有的话;最后,MCU之间的一个专门的接口,先进的高速总线( AHB )和FPGA 。该方法的使用依赖于高端应用和市场期望。

PIO接口

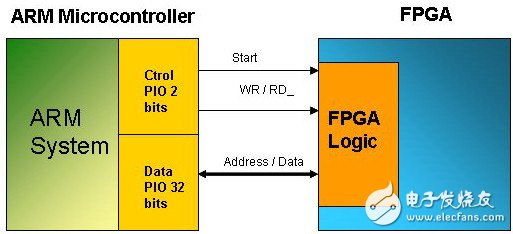

通过PIO 连接MCU和FPGA相对简单数据传输来说比较简单,包括传输32位的地址, 32位数据,还有一些控制信号的控制。这就需要一个32位的PIO和一个2位PIO(图1) 。

图1 PIO连接FPGA

为了将数据传输到FPGA,PIO中的双向缓冲器方向必须设置为输出。数据传输到FPGA的软件算法实现如下:

PIO_DATA = ADDRESS; // Pass the address to write

PIO_CTROL = START | WR; // Send start of address cycle

PIO_CTROL = CLEAR; // Clear PIO ctrl, this ends the address cycle

PIO_DATA = DATA; // Set data to transfer

PIO_CTROL = START; // Data is ready in PIO

PIO_CTROL = CLEAR; // This ends the data cycle

从FPGA读取数据的方法相似。同样,PIO中的缓冲区首先必须设置为输出,然后改变方向为输入从FPGA读取数据,下面是执行代码:

PIO_DATA = ADDRESS; // Set the address to read

PIO_CTROL = START | RD; // Send start of address cycle

PIO_CTROL = CLEAR; // Clear PIO ctrl, this ends the address cycle

PIO_DATA_DIR = INPUT; // Set PIO-Data direction as input to receive the data

DELAY(WAIT_FOR_FPGA); // wait for the FPGA to send the data

DATA_FROM_FPGA = *PIO_DATA; // Read data from FPGA

上述算法是一个基本的传输,更先进的算法是必要在ARM微控制器和FPGA之间建立适当的通信。特别要注意的是,确保数据的可靠性,例如没有因高速或等待周期造成资料遗失等。

访问时间计算的总和:

T访问-PIO=t1+处理阶段+t2+数据阶段

使用最大优化的GCC编译器,系统大约需要55个AHB周期向FPGA执行写操作(图2)。

图2 PIO向FPGA 写数据

假设t2(FPGA的等待响应时间)也大约是25个 AHB周期,系统大约需要85个AHB周期从FPGA进行读操作(图3)。

图3 PIO从FPGA读取数据

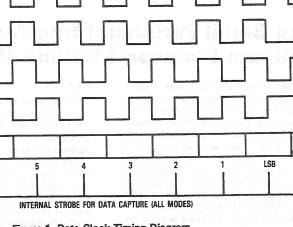

MCU自身接口连接非常简单和直截了当。然而,在FPGA里必须用特殊的逻辑来解码所有的由PIO生成的业务流。在大多数情况下,微控制器的业务流是完全异步。因此,FPGA必须能够从微控制器中过采样控制信号;否则,FPGA将错过时间窗口且业务流将不会最终到达FPGA内。

因为处理器专门负责维持PIO工作,所以处理时间消耗很大。虽然CPU是从事数据传输,它还是不能做别的事了。因此,这一解决方案有可能使系统处理陷入瘫痪。DMA不可能使用的PIO接口,所以程序员必须限制的数据带宽,以便其他任务能够与MCU进行通讯。例如,如果有一个常规的进程要求100 %的处理器运行周期,同时又要与FPGA进行串行(SPI,USART或TWI)通信(读或写),那么这两个进程必须有一个要等待。如果发送到或接受来自FPGA的数据没有及时的存进缓冲区,那么到下一个字节/字数据时可能会溢出。从本质上讲,嵌入式处理器成为受邤赖的数据移动硬盘。

通过外部总线接口连接(EIB)

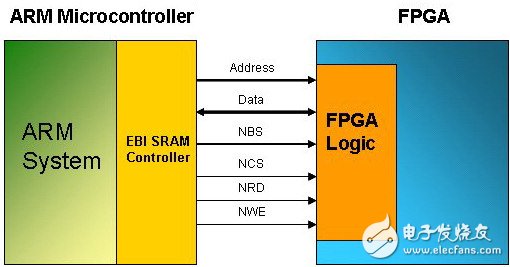

许多32位微控制器有一个外部总线接口(EBI)模块,它是为外部设备和基于ARM设备的存储控制器之间传输数据而设计的。这些外部存储控制器能够处理几种类型的外部存储器和外围设备,如SRAM,PROM,EPROM,EEPROM,flash和SDRAM。只要FPGA可以处理预定义存储器接口,EBI也可用于FPGA的接口。在EBI中使用静态存储器接口(SRAM)对于FPGA通信来说是最好的,因为它设计简单,且大多数设计者都熟悉它。至于PIO接口, FPGA不得不包含一个模块,用来理解SRAM时间,并能产生一个响应返回微控制器(图4)。

图4 EBI-SMC接口

图5显示了EBI读SMC存储器接口的标准时间,而图6显示了其标准写周期。

图5 EBI-SMC读周期

图6 EBI-SMC写周期

注意:这些时间波形是默认的SMC规格。所有可编程参数显示都基于外部设备的速度。

EBI的接口速度比PIO块,是因为EBI有其自己的I / O,且大部分的信号是并行的。但是,如果外部设备很慢或引入等待状态, EBI的速度优势可能会受到损害。

跟PIO接口一样, EBI接口必须由处理器或其他的主AHB来驱动。因此,实现带宽的EBI的还依赖于软件,并取决于它可以利用多少处理器时间。当然,可能受到带宽的限制。这又可能限制了嵌入式处理器旨在实现的其他系统功能。

在MCU中使用专用的FPGA接口

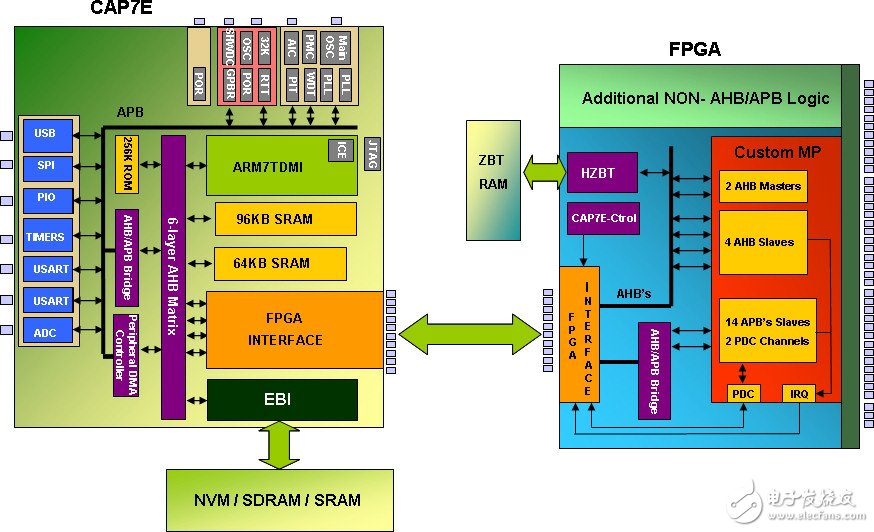

基于ARM7的微控制器提供一个特殊接口,它允许FPGA通过DMA存取2个主AHB和四个副AHB直接接入MCU的内部AHB总线。在启动时,一个外加的副AHB可用于重新映射ROM,它通过使用外部ZBT RAM具有PROM重新映射功能的FPGA来实现。

该接口还提供了FPGA接入14个副先进外围总线(APB)、两个全双工的DMA通道、多达13个中断优先编码(IRQs)、两个DMA传输的非编码IRQs和32位共享可编程I/O。该FPGA接口通过微控制器接入预先定义的主副AHB(图7)。

图7 MCU专用的FPGA接口

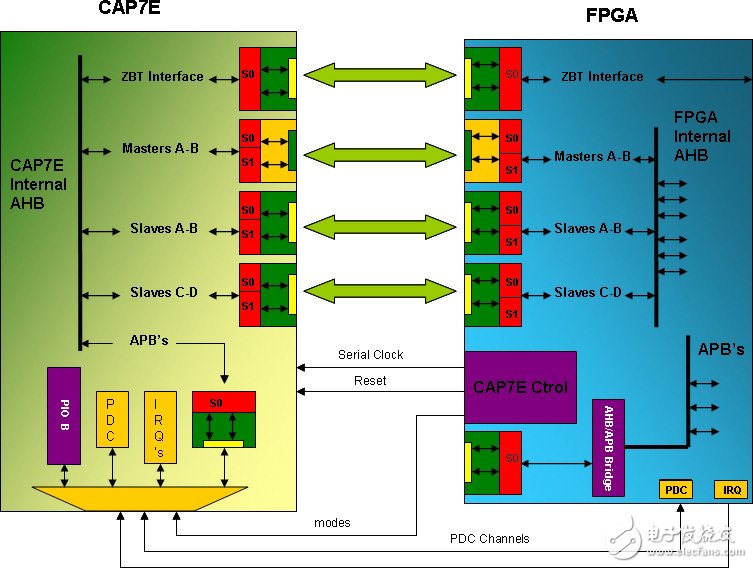

FPGA接口是基于多个并串行转换器来编码和解码所有微控制器和FPGA之间的业务流。为了使两个不同设备之间能进行有效的同步通信,必须满足以下要求:

在FPGA必须能够处理时钟偏斜平衡和时延消除。赛灵思的FPGA采用DCM(数字时钟管理器)强制性处理所有时延消除,且要求产生时钟。Altera的器件需要使用锁相环电路。该FPGA还必须为微控制器的内置接口提供配置和复位方式。它必须为微控制器提供的串行通信时钟,频率范围应在100兆赫以上。ARM7的内部时钟和串行时钟之间的比率应为0.8或更低(ARM的时钟/串行时钟)。

FPGA接口是基于一套编码和解码AHB内部业务流的单元。各主从AHB编码/解码的数据传输通过使用专用并串行转换器的MPIO来实行。由于传送大量数据,一个单一的传输就消耗多个AHB总线时钟周期。具体所需的时钟周期取决于ARM7中的AHB时钟、串行时钟和FPGA中的AHB时钟之间的比例。由于微控制器的AHB时钟与FPGA中的AHB时钟之间相互独立, FPGA和微控制器可以在不同的频率运行。甚是FPGA内的主或副AHB时钟可以在不同的频率运行。

微控制器和FPGA上的每个并串行转换器阻滞都有一个互补的有限状态机(FSM)与AHB总线打交道。因此,该接口可以借鉴EBI或PIO消除共同接口瓶颈的技术来处理同步传输问题。

带有直接FPGA接口的微控制器几乎所有的外围都有DMA通道,有几个DMA通道专用于FPGA的接口。多通道外围DMA控制器( PDC )支持该DMAs,像其他两种方法一样,在FPGA、外设和存储器之间传输数据时通过CPU卸荷。这避免了普通ARM7的带宽限制,它被只有4万比特每秒(Mbps)数据传输速率完全垄断。

通过从CPU中卸下这一任务, PDC可以实现处理时间占85 %CPU周期,数据传输率12 Mbps。多重DMA通道是专为FPGA接口连接PDC多个特定应用的外设和接口而设的,不受微控制器的任何干预。在PDC中使用DMA专用通道,可以使ARM处理器有时间把重点放在处理器的繁重任务上,提高系统的总体性能和数据带宽(图8)。

图8 ARM7与FPGA接口

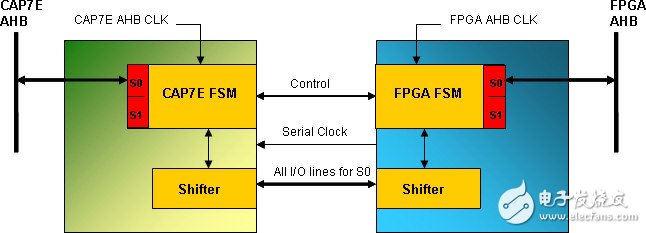

该并串行转换器模块能处理所有的AHB和串行通讯。它由一个有限状态机(FSM)和移位器组成。有限状态机解读AHB,并与AHB对话。当主AHB初始化一个传输(读/写操作)时,FSM通过使用遵守的AHB协议的HREADY来引入等待状态。FSM直接根据AHB时钟和串行时钟之间的比例来自动处理引入等待周期的数量。比例越小,引入的等待周期就越少。

FSM控制移位器,负责处理所有微控制器和FPGA之间的数据转移(序列化),每周期传输在2个bits的数据。如果串行时钟速率为100兆赫,移位器的传输速度为200 Mbps。

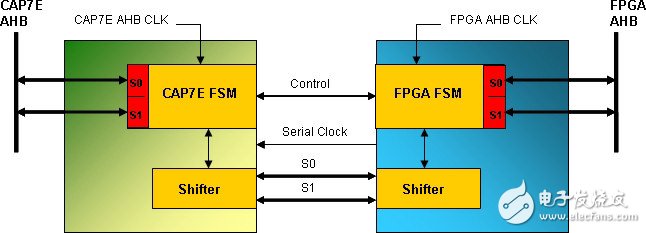

这些并串行转换器模块处理主口A / B、副口A / B和副口C/D,通过FPGA 内的“模式”模块在复位时程序化,使可用的I / O数量尽可能多。设计者可以为一个单一的串行配置选择使用所有的10个I / O线。在这种情况下,串行模块将只处理一个的AHB接口。例如,如果用户仅想使用AHB主口A,串行模块将所有主口设定为“串行单配置” 。这种配置将改善转换器之间的传输速度,从而加快了微控制器和FPGA之间的传输速度(图9)。

图9 串行单配置

另一种选择是配置串行模块为“双串行配置”使其能处理2个AHB接口,2个AHB (主/副)之间共用10个I / O线。在这种情况下,微控制器和FPGA之间的数据传输速率较低,但数据带宽更高,因为有2个AHB接口可用。双配置给另一个AHB接口重新使用一半以上的专用I / O(图10)。

图10 双串行配置

FPGA的接口逻辑

当通过EBI或PIOs执行一个FPGA接口时,工程师必须写RTL代码,让FPGA与MCU进行沟通。直接FPGA接口微控制器供应商提供的所有RTL需要为每个具体的FPGA供应商建立适当的编码和解码通信限制。这种逻辑模块产生一个重置,并提供不同模式下的重置条件。供应商提供的RTL可让用户来决定选择哪些功能来。默认情况下,所有的模式位0 (表1)。

表1 模式位

一个供应商提供的模板可用于FPGA接口的主从AHB实例。提供具体的例子。在FPGA模板,一个模块所谓的“自定义MP”不费力的整合AHB / APB外设。因为系统将使用FPGA逻辑,此模板让设计师使用迁移的两片MCU加FPGA毫不费力的实现单芯片可定制微控制器。

外部ZBT-RAM和NVM/SDRAM/SRAM是可选的,它基于应用程序和系统要求。

设计人员还可以在FPGA添加非AHB逻辑,为添加与AHB总线无关的功能提供了灵活性。

在单一配置模式下,单一AHB接口从微控制器传输所有的AHB信息到FPGA需要4个AHB时钟周期,反之亦然(图11 ) 。在双配置模式下,双AHB接口从微控制器传输所有的AHB信息到FPGA需要8个AHB时钟周期,反之亦然。

图11 通过直接FPGA接口传输的读/写时间

发生在ARM7 MCU和FPGA之间的相关传输时间如下:

t1:标准时间——2个AHB周期;

t2:FPGA传输所需时间(单一AHB接口4个周期,双AHB接口8个周期);

t3:FPGA的外设响应时间;

t4:传输响应返回CAP7E的时间(单一AHB接口4个周期,双AHB接口8个周期);

t5:从FPGA到CAP7E AHB总线内部读取响应/数据时间;

t6:引入等待周期时间。

下面的公式是用来近似从ARM到FPGA外设的存取时间:

注: t1和的t5相对于PIO和EBI是可以忽视的的AHB周期时间。

在数据传输速率低的情况下,如点阵式液晶显示器,MCU到FPGA通过PIO或EBI接口就足够了。然而,FPGA和MCU之间或其他一些外设和存储器的高数据传输率可以完全占用CPU周期和给外设创造瓶颈。举例来说, TFT液晶彩色图形将需要传输大量的数据到液晶显示器帧缓冲区,这最有可能完全占用CPU和EBI。这种应用将更好地执行从微控制器到FPGA的直接接口连接,而允许液晶数据通过DMA传输,使处理器空出时间处理其他事和使EBI空出时间传输其他数据,如从闪存运行主要应用软件,或TFT液晶显示器为单个或多个帧缓冲区使用SDRAM。

此外, FPGA中的AHB逻辑定义类似MCU,犹如它在微控制器“内部”。这使得未来设计路线很容易就转移到可定制微控制器。

直接FPGA接口的发展时间也较短,因为接口已经在微控制器内部定义且逻MCU供应商提供了FPGA的辑模块。设计者不需要写入任何接口RTL 。带专用FPGA接口的微控制器将会提高整个系统的性能和设计的易用性。

-

微控制器

+关注

关注

48文章

7557浏览量

151453 -

FPGA

+关注

关注

1629文章

21743浏览量

603556 -

液晶显示器

+关注

关注

11文章

576浏览量

43648

发布评论请先 登录

相关推荐

怎么通过FPGA实现微控制器?

基于XCCV3004HQ240芯片的8051微控制器接口设计

MAX1169 ADC与PIC微控制器的接口

可不使用微控制器配置Dallas Semiconductor

基于FPGA的PCI接口控制器的设计与实现

针对微控制器应用的FPGA实现

基于FPGA中实现微控制器

微控制器的FPGA接口的设计与实现方案介绍

微控制器的FPGA接口的设计与实现方案介绍

评论