引 言

随着电子技术的发展,对现代有源相控阵雷达的要求越来越高,而T/R组件是构成有源相控阵雷达的核心部件之一,因此对T/R组件的各个性能提出了更高的要求。同时微电子技术和MMIC电路的发展为T/R组件的设计提供了良好的基础,当前组件技术的发展趋势是在利用HTCC,LTCC等多层微带基板的基础上,集成了一片或数片多功能MMIC电路,再经过微电子互连而成。而这种组件具有体积小、重量轻、性能指标高、一致性好的特点。

在数量相同的一组T/R组件中合成发射功率越大,其雷达照射的范围则越大,所以研究高功率T/R组件显得非常重要。而在T/R组件设计时,最关键的是功率放大模块。该组件运用了混合集成电路(HMIC)和多芯片组装(MCM)相结合的技术,根据现有的制造工艺,设计出一种平衡放大器作为发射通道的末级功放部分,该放大器是两只功放裸芯片和一个Wilkinson功分器组成的,最终提高了功率的输出。

1 T/R组件的原理与组成

T/R组件原理框图如图1所示,在发射通道,由激励信号源送来的信号送入组件发射通道经过功率放大器使信号放大后馈至天线辐射单元;在接收通道,从天线收到的微弱信号经接收通道传到接收机。

组件接收通道包括限幅器、低噪声放大器和数字衰减器。在组件发射期间,若天线有很大的功率反射,此时限幅器能起到保护低噪声放大器的作用。组件发射通道则是两级功放链路组成,前两级采用芯片,而末级高功率放大器为下文重点设计介绍的。控制电路部分由数字移相器、数字可变衰减器、数字开关和驱动控制芯片组成。为了设计的需要运用了正反向的环形器,一个当作隔离器用,另外一个作环形器用。对于电源部分,因为组件发射功率器件为GaAs器件,其必须要先加负压(Vgs),后加正压(Vds,加负压保护电路就行。

2 设计思路与设计过程

设计T/R组件时,考虑最关键的就是末级功放部分,因此本文将对末级功放部分展开详细探讨。

2.1 设计思路

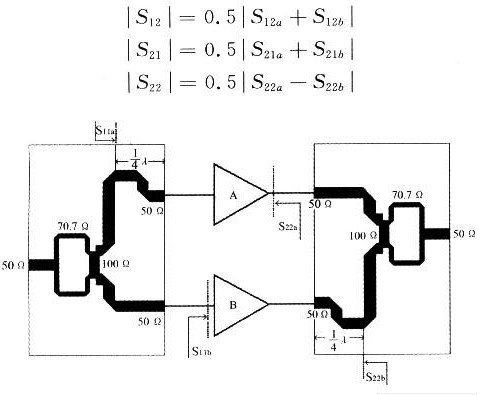

设计一个Wilkinson功分器,采用两个10 W功率放大器裸芯片进行合成,组成一个平衡放大器。Wil-kinson功分器采用了二等分功分器,原理框图如图2所示。因为信号在输入功分器的输出端是同相位的,所以,注入放大器A之前的信号和放大器B之后的信号需要相移,将其中的一臂增加了λ/4的线长,这样可以利用如下公式:

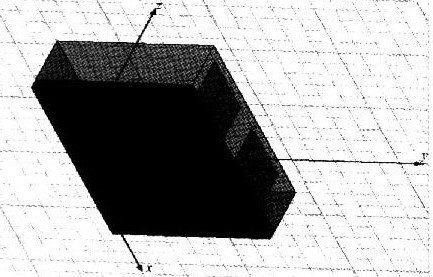

如果两个放大器完全相同,那么,S11=0,且S22=0,而且增益S21(S12也如此)等于耦合器的单边增益。2.2 Wilkinson功分器的设计与仿真基于现有的工艺水平,选用的导体为金,其厚度为0.01 mm,由于LTCC基板的工艺精度不佳,插损比较大,故而利用陶瓷作为介质,其介电常数εr=9.9,厚度为0.635 mm,损耗角正切值为0.006。通过软件仿真可以计算出两段50 Ω的线宽为W1=0.6 mm,70.7 Ω的线宽为W2=0.23 mm。电阻选为100 Ω的薄膜电阻。

按照上面的初始参数,利用HFSS仿真的结果计算,在X波段,三个端口的驻波均在1.19以下,两臂的公分比:端口二约为-3.1 dB,端口三约为-3.5 dB、两臂的隔离度在-27 dB以下和两端口的相位差为90°±5°。

2.3 x波段T/R组件的电磁兼容分析

T/R组件中存在着数字信号、模拟信号、微波信号、直流信号和脉冲信号等。因此,电磁兼容设计将是工程实现,调机联试中的难点,在设计阶段,必须充分认识到电磁兼容性设计的重要性。

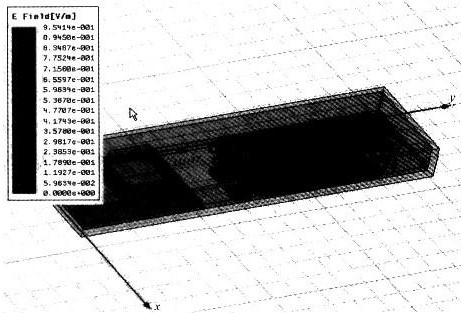

2.3.1 腔体效应

腔体效应是组件EMC设计中的一个重要环节,除了谐振频率和相应的Q值会导致组件的不稳定工作以外,腔体内部具体场分布特征也可能导致组件整体性能上的失败或成品率的下降。这里设计优化的目标是尽量降低腔体内部场分布强度。另外,在热耗严重地方(末级功率放大器芯片)不能有高强度的的场分布,如图4所示。同时,末级功率放大器的抗失配比对整个支路的稳定性也具有实际意义,而加上吸波材料来解决腔体自激现象也非常有用。

2.3.2 电源完整性

电源的完整性设计对T/R组件的正常稳定工作至关重要,造成电源不稳定的根源主要在于两个方面:一是器件高速开关状态下,瞬态交变电流过大;二是电流回路上存在的电感。

通过改变T/R组件内部接地方式,尤其LTCC内部接地方式,可以在多层布线结构要求和地平面阻抗之间找到平衡点,对各种电源之间进行地的隔离等来改善电源之间的干扰等。

3 功率放大器设计的制造工艺

采用中国电子科技集团第55研究所的两只WFD0049型号GaAs功率管和加工的Wilkinson功分器,此功率管主要参数为:具有高功率输出(Pout=40.0 dBm@8.5~10.5 GHz)、高增益(Gain=26 dB@8.5~10.5 GHz)、高效率(ηadd=35%)、带高集成内匹配等优点。准备好后采用如下工艺安装:

3.1 芯片安装

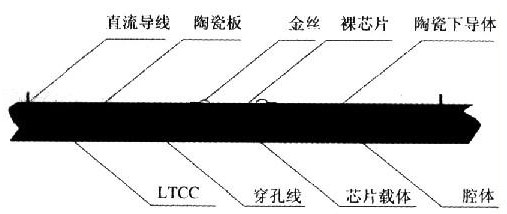

针对X波段高功率T/R组件来说,末级功放是发热较大的功率器件,因此采用的共晶焊,就是通过金锡焊料将裸芯片焊接于芯片载体上,装配时基板相应位置开孔,带载体再通过其他方式固定于盒体底部。

3.2 电路互连

末级放大电路互连时,芯片采用金丝热压焊,而基板之间的互连以及芯片电容与基板之间的互连都采用金丝球焊,为了改善微波传输性能,射频输入输出金丝应该尽量短,尽量使用两根金丝互连;电源馈电旁路电容离芯片距离应尽量短;大电流馈电焊点应采用两根或三根金丝,以防单根金丝过流熔断;馈电焊点可以采用金丝球焊,能够增加金丝的可靠性;射频传输也采用金丝球焊,同样增加了金丝的可靠性,射频传输采用金丝压焊性能更好。结构示意图如图5所示。

4 X波段高功率T/R组件的分析

如图6所示,为X波段高功率T/R组件设计的电路布局总体版图。

根据分析,Wilkinson功分器的插损以0.6 dB来计算,通过计算得到输出功率达到42.4dBm,即为17.8 W,而实际制造中考虑到加工工艺水平,结果要差一些,但完全可以达到16 W。

接收系统的增益大于25 dB,噪声系数小于4 dB,移相精度为4°(RMS),衰减精度为0.5°(RMS)。

5 结 语

对基于X波段T/R组件的末级功放的理论设计,能满足高功率的要求。该设计方案正在投版,由于生产周期原因,还要一段时间才能加工出实物,从而进行验证,并用于正在研制的X波段T/R组件上。同时今后仍将对此改进,如进一步缩小体积,减少插损,及提高隔离度等,将来研制的方向是将所有芯片直接设计在同一块LTCC基板上,并能达到高性能的T/R组件。

-

芯片

+关注

关注

456文章

50968浏览量

425036 -

集成电路

+关注

关注

5389文章

11576浏览量

362413 -

功率

+关注

关注

14文章

2069浏览量

69941

发布评论请先 登录

相关推荐

混合集成电路的EMC设计

薄厚膜混合集成电路前景怎么样

混合集成电路EMC设计产生的原因阐述

混合集成电路电磁干扰产生的原因是什么

混合集成电路,混合集成电路是什么意思

混合集成电路,什么是混合集成电路

芯片设计中数模混合集成电路的设计流程是怎么样的

多芯片组件的特点_多芯片组件的分类

混合集成电路的EMC设计详细说明

微波混合集成电路射频裸芯片的应用设计和封装方法介绍

如何设计混合集成电路的电磁兼容

使用混合集成电路和多芯片组装设计了高功率的T/R组件

使用混合集成电路和多芯片组装设计了高功率的T/R组件

评论