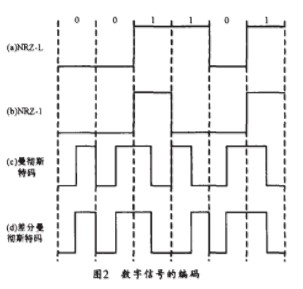

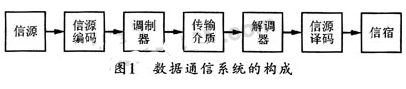

图1所示是数据通信系统的基本构成。在计算机通信中,通信双方传递的信息必须进行量化并以某种形式进行编码后才能进行传输。机内信号不论采用哪一种编码方法,它们的基本信号都是脉冲信号,为了减少信号在传输媒质上的通信带宽限制,以及噪音、衰减、时延等影响,也由于同步技术的需要,操作时都需要对简单的脉冲信号进行一些不同的变换,以适合传输的需要。这样就会产生许多不同的代码,通常有不归零电平(NRZ-L)码,逢“1”反转(NRZ-1)码,曼彻斯特码和差分曼彻斯特等。图2所示是部分编码方式的波形图。

由图2可知,不归零码的制码原理是用负电平表示“0”,正电平表示“1”,其缺点是难以分辨一位的结束和另一位的开始;发送方和接收方必须有时钟同步;若信号中“0”或“1”连续出现,信号直流分量将累加。这样就容易产生传播错误。曼彻斯特码(Manchester)的原理是每一位中间都有一个跳变,从低跳到高表示“0”,从高跳到低表示“1”。这种编码方式克服了NRZ码的不足。每位中间的跳变即可作为数据,又可作为时钟,因而能够自同步。曼彻斯特编码特点是每传输一位数据都对应一次跳变,因而利于同步信号的提取,而且直流分量恒定不变。缺点是数据编码后,脉冲频率为数据传输速度的2倍。差分曼彻斯特码(Differential Manchester)的原理是每一位中间都有一个跳变,每位开始时有跳变表示“0”,无跳变表示“1”。位中间跳变表示时钟,位前跳变表示数据。这种方式的优点是时钟、数据分离,便于提取。

2 曼彻斯特编解码器的设计

可编程逻辑器件的出现为数字系统的设计带来了很大的灵活性.而VHDL (VHSIC HardwareDescription Language)是一种功能强大的硬件设计语言,可用简洁的代码来进行复杂控制逻辑的设计。为此,本文采用VHDL语言来对曼彻斯特编解码器进行描述,并用Active-HDL进行编译,最后用Synplify进行综合。

2.1 解码

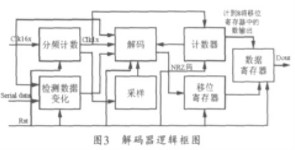

根据曼彻斯特码的特点,可将该码的解码过程分成三部分:一是启动解码时钟,即通过检测一个数据跳变沿来使能时钟。二是对曼彻斯特码形式的数据进行解码。三是将串行数据转换成并行数据。解码器的逻辑框图如图3所示。

该逻辑可南进程实现。输人的时钟为clkl6x的时钟,串行的曼彻斯特码的数据与单倍的时钟相对应。首先,串行的曼码由clk16x的时钟采样,之后再将采样到的数据先后存放在两个寄存器中,当两个寄存器中的值不一致时,即开始解码过程,从而完成检测数据变化的进程。分频计数进程用来产生clklx,并用分频计数的结果来实现1/4和3/4点的采样。根据曼彻斯特码的性质,对1/4和3/4点采样可以准确的恢复成NRZ码。此后在clklx的驱动下,控制字计数器开始计数,直到8个clklx之后,计数器归零。解码进程则在clkl6x的驱动下,对1/4和3/4采样点的数据进行解码,从而得到曼码相对应的NRZ码。紧接着将解码得到的每一位NRZ码移入8位的移位寄存器,当控制字寄存器计到8时(即8位移位寄存器溢出的时候),再将8位NRZ码一起输出到数据寄存器,最后输出数据寄存器中被解码好的NRZ码。

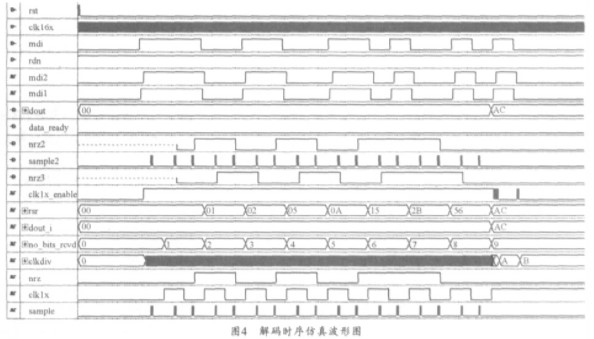

图4所示是采用该设计的曼彻斯特码的时序仿真波形,clkl6x采用16 MHz的时钟,mdi为输入的曼码(10101100)。最后输出dout为十六进制AC,这说明该解码过程是正确的。

2.2 编码

编码是解码的逆过程。编码的过程也可以分为两部分:一是检测编码周期是否开始,以决定产生正跳变沿;二是对串行的数据进行编码,之后编码周期结束。编码器的输入时钟(clk2x)为2MHz。当写信号(wr)为高电平时,开始产生正跳变沿,并使clklx-enable为高电平,这样,正跳变沿产生完成即开始编码过程。将clk2x进行二分频可得到clklx,这样可使归零制的数据(nrz)与clklx相对应。此后再在clklx_enable高电平和clk2x正跳变的情况下,将归零制码(nrz)转换成相应的曼彻斯特码(meo)。最后,当写信号(wr)为低电平时,以使clklx_enable为低电平,结束编码过程。

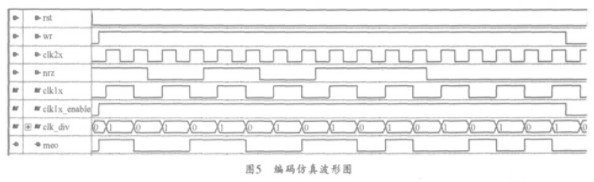

图5所示其编码时序仿真波形图,图中,clk2x采用2MHz的时钟,nrz为串行输入的归零制码(10101100),meo为串行输出的曼彻斯特码。由图可见,从刚开始的跳变沿之后,输出meo也为10101100,证明编码过程正确。

3 基于CPLD的曼彻斯特码实现

为了确保设计的可行性,操作时必须对设计进行时序仿真。为了提高CPLD芯片的性能及资源利用率,应采用专门的综合软件来对设计进行优化和综合。本设计采用Synplify7.3进行综合,并采用Active-HDL6.1进行时序仿真。在Synplify中使用有效的代码可以优化组合逻辑、减少逻辑延时,从而提高整体性能。此外,本设计还进行了多个文件的分块设计,然后将这些文件映射到顶层文件进行综合,并运用VHDL对单个文件进行编写、仿真和优化。在用到组合逻辑时,Syn-plify会尽量避免锁存器的出现,节省逻辑单元。Synplify和其它综合软件一样,编译后所生成的电子设计交换格式文件(EDIF)可以在Active-HDL中进行编译、仿真、分配引脚和其它优化处理。因此,采用Active-HDL6.1和Synplify7.3相结合对CPLD进行设计、优化、综合,可以提高系统性能和

芯片资源的利用率。

CPLD(Complex Programmable Logic Device复杂可编程逻辑器件)的内部结构为“与或阵列”。该结构来自于典型的PAL、GAL器件结构。由于任意一个组合逻辑都可以用“与一或”表达式来描述,所以该“与或阵列”结构能实现大量的组合逻辑功能。CPLD和FPGA的主要区别如下:

(1) 布线能力

CPLD内连率高,不需要人工布局布线来优化速度和面积,较FPGA更适合于EDA芯片设计的可编程验证;

(2) 延迟可预测能力

CPLD连续式布线结构决定了时序延时是均匀的和可预测的,而FPGA的分段式布线结构则决定了其不可预测时间延迟;

(3) 集成度的不同

CPLD的集成度一般在500~50000门。而FP-GA的集成度一般在1K~10M门;

(4) 应用范围的不同

CPLD逻辑能力强而寄存器少,适用于控制密集型系统,而FPGA逻辑能力较弱但寄存器多,适于数据密集型系统。

CPLD和FPGA的共同优点一是规模越来越大,实现功能越来越强,同时可以实现系统集成。二是研制开发费用低,不承担投片风险,使用方便。三是通过开发工具在计算机上完成设计,电路设计周期短,同时不需要设计人员了解很深的IC知识,EDA软件易学易用。此外通过FPGA和CPLD开发的系统成熟后,还可以进行A-SIC设计,以形成批量生产。

事实上,本设计在Xilinx公司的XC9500系列CPLD(xc95108pq100-7)芯片上进行了实现。并针对其特点对设计进行了最后的优化。该编解码器共占用了149个逻辑单元,占总逻辑资源的8%,因此,十分有利于今后对其进行完善和功能的添加。

4 结束语

本设计具有一定的通用性,它的逻辑大部分只涉及到编、解码器本身;而它与外部的接口十分简单,只要对其读、写并对跳变沿信号进行有效控制,就能使其正常工作。本设计十分独立,由于选用器件资源比较丰富,故对其进行功能添加也十分方便,只需添加电路设计而不必对原有电路进行修改。

-

芯片

+关注

关注

455文章

50791浏览量

423491 -

解码器

+关注

关注

9文章

1143浏览量

40738 -

cpld

+关注

关注

32文章

1248浏览量

169353

发布评论请先 登录

相关推荐

采用复杂控制逻辑器件和VHDL语言实现曼彻斯特编解码器的设计

CPLD XC9500是否有任何序列?

XC9500系列CPLD遥控编程该怎么设计?

编解码器的工作原理是什么?

基于CPLD的卷积码编解码器的设计

EDA卷积码编解码器实现技术

用FPGA实现1553B总线接口中的曼码编解码器

基于FPGA的曼彻斯特编解码器设计

在XC9500系列CPLD芯片上实现曼彻斯特码编解码器的设计

在XC9500系列CPLD芯片上实现曼彻斯特码编解码器的设计

评论