设计结束了专用电路板试验台测试结果表明功能完全正常设计小组的工作人员不约而同地长舒了一口气每个人都认为最艰苦的阶段已经过去了专用系统板的最终集成开始进行性能可靠的线性试验台电源很快将被高效的开关电源所取代试验室基准时钟现已被低成本解决方案取而代之在最初的专用电路板测试结果显示有望获得极佳性能的同时无法预知的逻辑器件失效正在系统中悄然滋生在无计可施的情况下只好在背板上插拔电路板人们发现只有某些插槽组合能够正常工作这纯粹是一个逻辑问题吗系统电源上的负载是否包含在计算公式中电路板彼此靠近有没有产生问题时钟抖动是否关闭了定时容限窗口如何才能对问题实施隔离以便开始试验的正确设计这些问题均难以回答但是在系统设计的整个过程中我们当中的大多数人都将会至少一次向这些问题妥协摆脱这种无奈困境的方法是求助于工程SWAT小组这是由一些具有多年丰富维修经验的优秀工程师所组成的团队来解决问题SWAT小组带着一连串的问题深入到试验室中进行调查至关重要的每个人都必需尝试回答一个根本题试验台与系统设置之间的区别是什么

当处理复杂问题时时常回过头去对子系统之间的依存性重新进行分析和思考往往能够得出令人惊讶的结果这样做的道理在于在某种场合起作用的东西未必会在其他场合自动生效当遇到系统依存性问题时系统时钟通常成为人们的重点怀疑对象将系统故障归咎于时钟固然不难但根本原因何在时钟究竟是引发故障的罪魁祸首还是周围环境的替罪羊虽然本文并不能够针对系统细节专门作答但的确对存在有噪基准时钟脉冲源时的抖动衰减方法进行了研究这并不是寻求最小衰减的另一种尝试而是要弄清楚显著衰减会产生什么样的后果此项工作在很大程度上来说就是众所周知的FailSafeTM时钟架构的一个特殊研究分支在时钟冗余系统中FailSafeTM的作用是在基准时钟脉冲源消失的情况下简化开关操作并维持时钟的存在试验室分析表明FailSafe架构能够在原有应用范围的基础上自然地扩展到用于对付严重的时钟修整问题保持同步自然是必需的而FailSafe也能够做到这一点

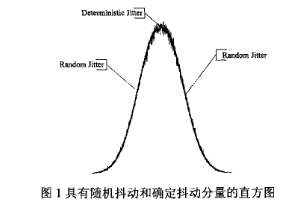

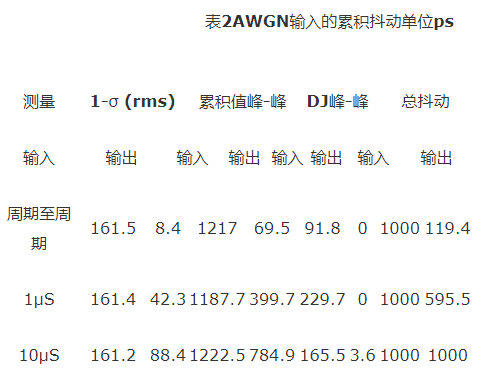

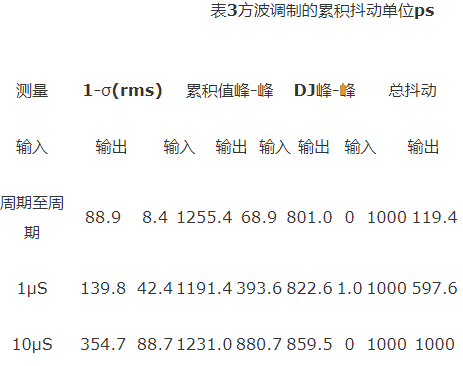

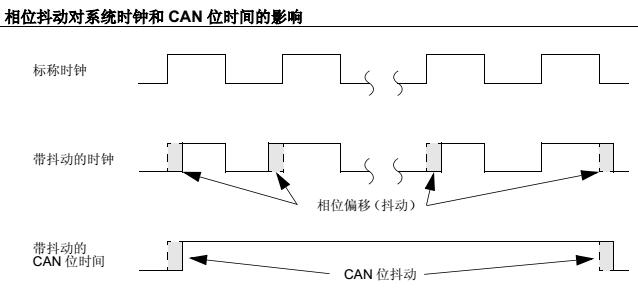

抖动有多重含义而对时钟抖动的要求与系统规范具有很大的相关性为完成这项工作需要关注三个主要的测量条件包括周期至周期抖动有时称为周期抖动以及1s和10s时间间隔内的累积抖动抖动信息的统计累积随后以随机抖动RJ和确定抖动DJ给出通常用直方图来表示

随机抖动和确定抖动一种不受欢迎的组合

虽然系统中的自然高斯噪声发生元件始终会引发抖动但如果存在DJ则清楚地表明一个调制信号源正在向定时系统注入能量从直方图的角度来看DJ充斥于中间部分从而扩展了直方图左侧和右侧的自然高斯响应图1示出了该原理由于数字系统是有限系统就是说不应存在调幅信息而是在恰好正确的时刻获得一个0或1因此边缘布局信息的收集和分析过程正是抖动分析的切入点因为直方图是边缘的统计集合所以良好的测量需要大量的采样信息组合来获得必要的+/-6统计数据抽取这样做是有道理的由此可实现最高的测量精度

噪声条件下的时钟信号修整

系统中的噪声能量的影响似乎总会不可思议地侵入时钟脉冲源时钟脉冲源遭受传导噪声或辐射噪声影响的可能性大致相同虽然大多数工程师在工作实践中均采用容性旁路技术来对付传导噪声但辐射噪声却往往更加难以定位和矫正串扰即属此类这是因为电气孔隙通常足以成为代人受过的时钟脉冲源至吸收辐射能量的轨迹其他一些常常被忽略的因素是由磁感应所耦合的能量捕获到一个与电源开关速率奇迹般地保持同步的时钟调制频率的情况并不鲜见

减少时钟走线孔隙有利于吸收辐射能量由于互易定律有效因此能够容易地吸收辐射能量的时钟线同样也会容易地辐射能量这将在进行EMI辐射测试时产生不良影响随着近期ZDB即零延迟缓冲器的普及定时分配正在变得更加局部化了这是一件好事除了时钟缓冲机制外ZDB还能够利用PLL技术来提供零延迟甚至负延迟以克服时钟传播虽然能够进行一些抖动衰减但总的说来ZDB器件并不提供使一个器件能够完成很大的抖动衰减所需的编程参数

利用模拟技术来进行信号修整

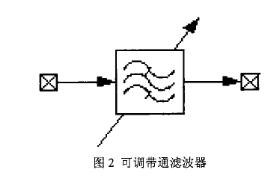

由于抖动对载频或以最佳单位间隔UI运行的纯时钟基频进行调制因此从理论上说布设一个频带极窄的带通滤波器应该有助于衰减调制分量由于尖锐响应具有高Q值所以必须小心地将带通滤波器置于载波的中心以确保基频不被衰减否则载频随着时间的长期推移而发生的自然漂移将导致显著衰减理想的情况是滤波器应跟踪载波的变化在我们所举的简单示例中需要进行时钟信号的再整形以重新生成一个方波信号原因是带通滤波器有可能除去谐波分量虽然以这种方式来减轻抖动是合理的但是要想以较低的成本和较小的占用空间来实现具有所需Q值的有效解决方案则很困难

采用PLL来减轻抖动的技术

由于PLL在时钟发生和分配中所起的作用持续增长因此将PLL转移函数用作减轻抖动的方法是值得考虑的这种采用PLL来减轻抖动的处理过程要求对其实现方法假定有一个可提供满足设计目标的足够编程选项的器件有一个全面深入的了解

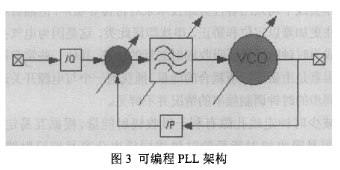

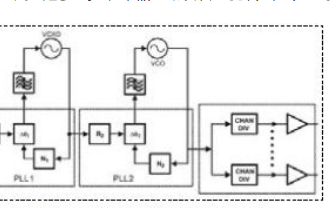

PLL具有可为上述采用带通滤波器来减轻抖动的方法提供跟踪功能的优点环路内部的增益和环路带宽组合通过改变响应来改变转移函数在处理高集成度的低成本PLL解决方案时通常会牺牲编程方面的灵活性包括更改常常是集成化的环路滤波器图3描绘了一种理想的PLL编程方案在该方案中电荷泵环路滤波器和VCO增益均可在一个扩展范围内进行修改然而如果没有仔细的分析以及准确的实验室结果则PLL实际上有可能造成系统的噪声增加这首先就从本质上使采用PLL的做法变得毫无意义

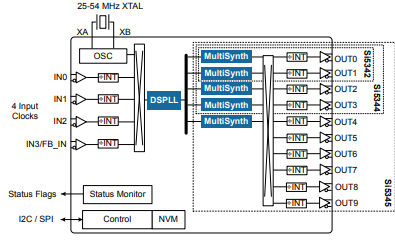

所需要的东西等效于一个频带非常窄的跟踪滤波器该滤波器接受一个具有RJ和DJ的输入且最终输出只产生尽可能低的本征RJ为此人们发现FailSafe架构具有那些饱受系统DJ困扰的系统所追寻的特性虽然RJ始终存在但减轻RJ被证明同样是值得考虑的FailSafeTM还根据高抖动衰减提出了大时钟倍频比的概念而这在采用标准PLL器件时是非常难以实现的由于我们正在处理的是如何减轻抖动因而此类应用完全有理由使用一个更加合适的名称在下文中所讨论的器件被称为带宽可调抖动衰减器或BAJA芯片

BAJA架构概述

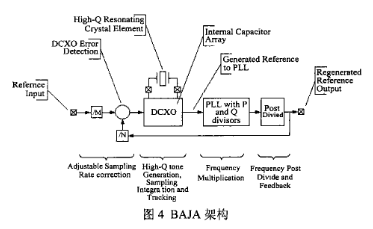

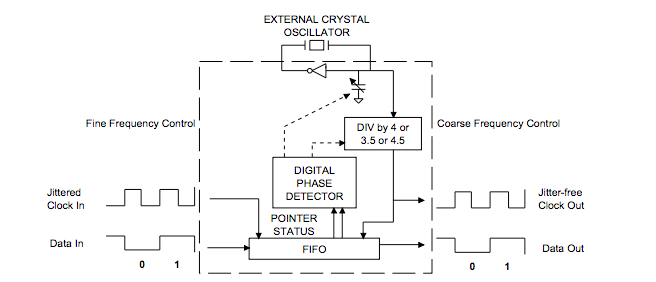

BAJA包括两个通过前馈和反馈通路进行通信的独立本征功能电路第一项主要功能是对只能被缓冲或以这样或那样的方式校正至可用电容器所允许的最大偏移量的时钟发生提供支持即VCXO作用校正需要一个基准输入以及来自BAJA输出的反馈信号然而在没有基准输入的情况下操作将继续进行这就是最初采用FailSafe架构的主要原因之一采用时钟发生这一称谓是准确的因为它并不涉及合成一个晶体用于生成被用来满足同步要求的基准频率该功能被称为DCXO因为它起着数字受控晶体振荡器的作用由于采用了内部晶体容性阵列设计因此晶体的推挽操作原理与模-数转换器相似由于高频颤动具有提高编解码器的信噪比SNR的作用所以存在于基准输入上的噪声也会使DCXO响应产生高频颤动

DCXO的作用是产生一个相位噪声非常低的振荡器高Q值该振荡器能够通过反馈来在一个有限的频偏范围内对输入进行跟踪从本质上说这仿效的是跟踪滤波器的原理应当了解的是基准时钟与晶体频率之间不必有任何的共同之处这就为基准频率走低至8kHz以控制BAJA并在具有极低抖动的器件中生成一个频率达数百赫兹的输出创造了条件这种做法与能够进行倍频但抖动往往会因PLL环路更新速率较低而有所增加的传统PLL设计存在着很大的差异在BAJA架构中倍频比可以达到几个数量级而不会使抖动响应发生劣化

在DCXO输出之后是采用传统PLL技术的时钟合成及倍频现在提供给PLL的是一个抖动较低与原始基准无关而与跟踪DXCO密切相关的高基准频率高PLL基准频率会转化为用于前馈和反馈除法器的高校正速率BAJA的编程涉及到频率比的选择图4示出了BAJA架构输入定时脉冲源基准信号通过M分频器之后可与通过N除法器的器件输出进行比较产生于M和N除法器之间差异的校正信息指示DCXO改变晶体频率通过一个内部PLL所进行的倍频操作的作用是提供一个可编程输出频率和一个直接取自晶体信号源的基准后置分频和通过N除法器所进行的反馈的目的在于使器件与基准输入相同步

旨在实现最佳抖动衰减的BAJA调整

虽然尚有大量的实验室分析工作有待完成但早期的经验数据表明输出DJ在存在输入DJ的情况下会发生显著的衰减为获得最佳响应而对BAJA所进行的编程将需要做一些实验这是由于每个系统都会因其配置的不同而呈现出一组或多组独特的噪声分布一般而言人们首选的做法是维持PLL部分中的高校正速率即通过保持尽可能小的P和Q除数值来使PLL以尽可能高的速率运行并让后置分频器提供正确的输出频率M和N的最佳设置在满足能够最大限度地减少输入DJ分量的DCXO采样频率的条件下进行由于至BAJA输入的PLL输出是相关的如果需要实现同步的话所以之后需要对设置比进行增减以达到上述目的实验室分析在采用了能够精确测量抖动分布信息的仪表的情况下开始进行

其他一些具有次要影响但迄今为止几乎未引起人们关注的因素存在于晶体部分与我们的窄带滤波器非常相似晶体的Q值开始成为藉以生成一个无噪声的基准时钟脉冲源并在DCXO高频颤动时设定频率变换速率的方法就我们目前业已完成的有限工作台试验而言采用的是Q值略高于100K的晶体做出这种选择纯粹是基于这样的考虑即当与该器件一道工作时最高的晶体Q值可能并不是唯一的目标对BAJA转移函数进行整形可能需要关注一些Q值较低的器件比如陶瓷谐振器以提供一种不同的响应分布这种概念也许会被用于降低EMI的扩频系统所接受在这种系统中允许BAJA对响应曲线进行整形以便让特定的DJ信息通过

BAJA架构还支持一项额外功能该功能允许在器件中设置16种不同的抖动衰减模式模式的选择是通过外部引脚配置来完成的对于动态可重构系统来说这种方法被证明是极为有用的当在系统上进行电路板的插拔操作时噪声分布会发生改变BAJA的作用是为现有的特定电路板配置提供优化的抖动衰减可对一个FailSafe输出系统锁定进行逻辑监控以确保获得完全的器件同步

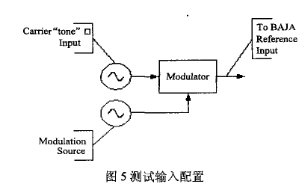

实验的设计

最为困难的工作之一是如何定义一组能够满足某些常见系统表示法的噪声条件选择了两种受控噪声注入分布该过程包括增加平均高斯白噪声我们的RJ影响以及通过对一个方波进行微分处理以抽取边缘速率信息的方法来进行脉冲调制后者的目的是在信号上生成一个DJ分量载波音输入由一个噪声层特性远远低于噪声调制分布的无干扰型音频发生器提供的该载频的漂移也非常低于是长期抖动特性保持稳定载频和调制信号源输入均被馈入调制器而调制器的输出则被传递给至BAJA器件的基准输入

由于噪声测量从很大程度上来说是一种统计特性测量因此我们的实验设计要求采用归一化常数来获得一个基准点在这种场合调制指数将被增加直到一个1ns峰-峰测量结果能够在10s的最大时间窗口间隔上保持一致为止从统计的立场出发我们的分析捕获了至少6的采样内容

我们所做的第一个试验是采用一个具有良好工作性能的白高斯噪声信号源来对一个音调进行调制对于脉冲系统必须规定重复频率和占空比的选择依据对于脉冲频率研究了100kHz和33kHz两种设计依据其中100kHz用于模拟一个开关模式电源而33kHz则用于受EMI影响的系统和扩频定时解决方案中的典型调制频率当占空比被选为50%时脉冲频率即被选定为33kHz调制信号源的频率被增加直至观测到一个1ns的峰-峰输出调制幅度为止

试验结果

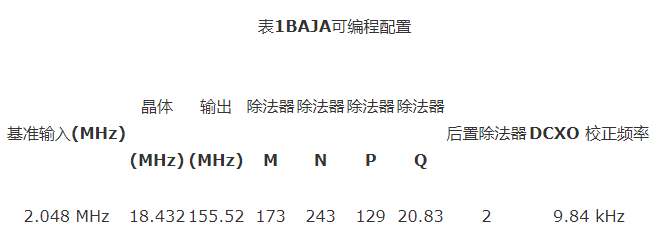

表1罗列了针对BAJA配置的编程参数设置由于BAJA是可编程的故可以选用多种系统专用频率本次试验的目的在于将一个分别满足2.048MHz和155.52MHz的输入和输出标准的晶体用作通用通信频率并未尝试针对输入DJ来优化校正速率

表2至表4 汇总了实验室数据结果针对AWGN输入条件进行了三项测量并采用脉冲注入对DJ进行了相同项目的测量每组测量均包括周期至周期以及1s和10s间隔这三个项目对各个BAJA输入至输出做了比较表4包括了本征测量以便于对实验室设置的噪声层有一个更好的认识虽然本征噪声层看上去并不令人满意今后还需在某些方面加以改进但毋庸置疑的是BAJA在未调制条件下将继续展现优良的工作性能

从以上的表格可见在最小抖动注入为42psRMS的情况下实现了8.4psRMS的BAJA噪声层在标准的实验室试验条件下周期至周期抖动至少降低了4倍而且长期测量结果显示时间间隔为1s时抖动至少衰减4倍而在时间间隔为10s的极端条件下的抖动衰减倍数为2不包括表4

表中还列出了相同设置条件下的峰-峰累积抖动和DJ令人惊讶的是BAJA的运用使得DJ显著下降达到了仪表的分辨率水平当我发现DJ几乎为零时一度感到难以相信但最终还是接受了事实是当下一次您的系统中充斥了DJ时不管在什么情况下BAJA都会为您提供一个值得认真研究的衰减DJ响应

总结

对于需要考虑DJ的系统BAJA可以提供帮助虽然从本质上说噪声是任何系统的一部分但是如果您想大幅度地减少重新设计的工作量则噪声衰减机制或许就是至关重要的一环就DCXO校正速率在优化抖动衰减以及晶体Q值的选择依据方面所起的作用而言BAJA还有许多工作要做然而根据最新的实验室信息以及所提供的一致性数值当下一次时钟脉冲源上需要进行严格的信号修整时BAJA或许就是能够满足您要求的解决方案

责任编辑:gt

-

噪声

+关注

关注

13文章

1118浏览量

47369 -

pll

+关注

关注

6文章

774浏览量

135046 -

测量

+关注

关注

10文章

4766浏览量

111131

发布评论请先 登录

相关推荐

采用片内PLL实现实速扫描测试的方案

评估低抖动PLL时钟发生器的电源噪声抑制性能

MAX3625B 抖动仅为0.36ps的PLL时钟发生器

可再配置PLL的最佳配置

PLL抖动及其对ECAN™技术通信的影响

Si5345和SI5344及SI5342系列抖动衰减时钟倍增器的数据手册免费下载

级联式PLL时钟抖动滤除技术实现的设计说明

抖动衰减时钟设计与应用技巧资料下载

评估低抖动PLL时钟发生器的电源噪声抑制

采用PLL技术实现最佳抖动衰减的BAJA调整

采用PLL技术实现最佳抖动衰减的BAJA调整

评论