1 引言

随着人类对空间探索的深入,空间环境对空间飞行器的电子设备和器件的影响逐渐显现 出来。空间辐射效应,特别是单粒子效应,对空间任务的完成具有潜在的巨大危害。星载计 算机是卫星的核心部件,在空间辐照环境下,必须充分考虑单粒子翻转现象对星载计算机程 控功能的破坏或影响。针对该问题, 目前普遍采用纠错检错(EDAC)设计对星载计算机的RAM 存储单元进行纠错检错处理来消除SEU故障。

EDAC功能可采用硬件和软件两种手段来实现。采用软件手段实现,需要在读写RAM存储 单元时,对存储数据和冗余信息进行计算,因而要占用大量的CPU时间。对于星载计算机而 言,由于CPU器件选型的局限,限制了CPU的性能,使CPU资源非常宝贵,因此目前普遍采用 的是硬件手段来实现EDAC功能。随着FPGA在通信信息特别是在航天领域的广泛应用,FPGA 已成为EDAC功能实现的最佳硬件手段。从目前可获得的资料看,近些年欧美发射的卫星均采 用了FPGA作为星载计算机的核心器件。

2 基于汉明码的传统EDAC设计

2.1汉明编码

目前有许多编码可以用来作为抗SEU的纠错码使用,汉明编码是最常用的EDAC编码,由 Hamming于1950年构造。这种编码可以进行检错和纠错,可以检测1比特和2比特错误,只能 纠正1比特错误,因此适用于单组数据中出现多个错误位概率较低的情况,这恰与SEU经常会 修改星上RAM存储单元1比特信息的情况相符。

汉明编码的实现增加的硬件资源主要是存储器单元,用来存储冗余数据,另外还增加了 编码和解码电路,参加编码和解码的异或门电路随着原始数据位数的增加而线性增加。在处 理性能方面,编码和解码造成一定的延时,增加了存储器的读写时间。

2.2传统的EDAC电路设计

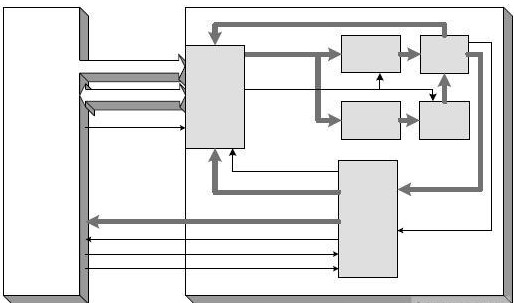

传统的EDAC电路设计仅实现读写功能,基本原理框图如图1所示.写操作时,CPU将数据送入EDAC编码模块中,EDAC编码模块根据该数据生成校验码,并将原始数据和校验码分别写 入数据RAM和校验RAM中;读操作时,CPU将数据RAM和校验RAM中的数据取出,送入EDAC纠错模 块中,EDAC纠错模块将正确的数据送至CPU。这里EDAC编码\纠错模块的硬件实现可以是专用 芯片,也可以采用通用的中小规模集成电路搭建。

SEU造成的RAM单元1比特错误如果不定时清除,就会产生累积,使计算机由此处理的结 果产生出2比特甚至更多比特错误,这种情况下将无法采用EDAC功能进行数据纠错,导致系 统错误操作甚至任务失败。因此定时对RAM存储单元进行更新是必要的,但在传统EDAC电路 设计下,对RAM存储单元的更新只能由计算机的CPU(单片机)进行,其操作流程如下:

(1) 从存储单元读出数据;

(2) 将读出数据重写入;

(3) 重复(1)~(2),直至全部单元更新完。

以航天计算机常用的80C32单片机为例,CPU对外部存储单元的读或写操作需要2个指令 周期,读完再写入需要4个指令周期,每个指令周期包含12个时钟。假设CPU时钟为20MHz, 更新1M个RAM存储单元需要的CPU时间为:4×12×1M 20MHz = 2.4s。

对于星上非常紧张的CPU资源来说,这是难以接受的,大大增加了星上CPU软件的设计难 度。这种方法的另一个大的缺点是无法获得数据错误信息,因为CPU直接读取的是纠错后的 数据,所以无法对星上SEU造成RAM单元出错的概率和错误模式进行统计。

3 基于FPGA的自检EDAC设计

3.1 功能分析

由于FPGA的内部大量的逻辑资源,使EDAC电路设计可以实现更加复杂的功能。在星载计 算机中,为了提高效率并节省CPU资源,一个理想的EDAC电路设计,应具有以下三部分功能:

(1)数据读写功能。在CPU写操作时,对原始数据进行编码,生成校验码,并将原始数 据和校验码存储;在CPU读操作时,从存储器中取出原始数据和校验码,进行计算,如有错 误,将错误纠正后输出,如无错误,直接将原始数据输出。

(2)自检、自纠错功能。在CPU控制要求下,可自动对所有EDAC保护的RAM存储区进行 顺序读取和校验,检测出错误数据或校验码。在自检状态下,如果由CPU配置为自纠错状态, 当某一RAM单元检测出单比特错误后,自动将正确数据和校验码重新写入该RAM单元。该项功 能的实施,基本上可保证SEU对计算机RAM区造成的影响及时得到修复。

(3)错误信息处理功能。在CPU读操作或者自检状态下,通过输出错误标志信号,对CPU 产生中断,对产生的错误进行相应处理。在CPU读操作或者自检状态下,如果检测出错误, 将出错的地址、原始数据和校验码进行暂存,可由CPU读取,进行相应处理。

3.2 设计与实现

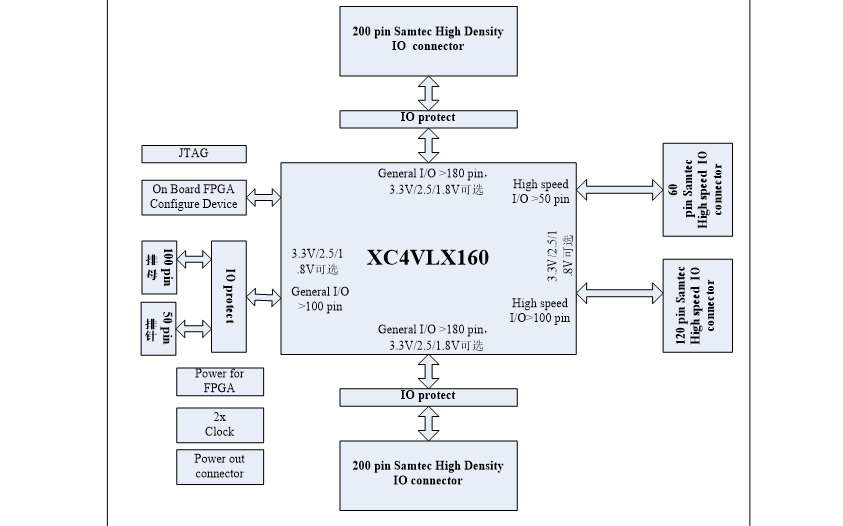

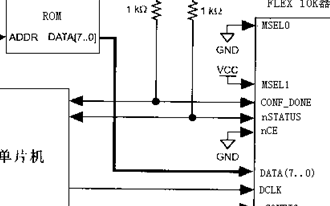

根据以上分析,笔者设计了如图2所示的自检EDAC电路,EDAC的功能主要由FPGA来实现。 到目前为止,具有航天等级的FPGA芯片已经具有内置的CPU硬核以及高达2.5Mbit的RAM资源, 因此该设计中的CPU和RAM模块均可以是FPGA内部资源,当内部资源无法满足设计要求时,也 可以采用外置CPU芯片或外置RAM芯片。

在本设计中,我们采用外置的CPU芯片和内置的RAM单元,作为自检EDAC电路的硬件平台 (或环境、资源)。CPU芯片在这里起到的作用是启动EDAC自检,处理错误中断,向地面传 送错误信息,并根据地面要求对错误信息进行处理。

在该设计中,检测一个存储单元地址仅需要4个时钟周期,如果开启自纠错功能,并且 检测到单比特错误,再增加2个时钟周期用来纠错。因此如果时钟为20MHz,并且错误数据较 少,则更新1M个RAM存储单元需要的时间约为:4×1M 20MHz = 0.2s。

更重要的是,在这0.2s的时间里,仅在出现错误时需要向计算机产生中断,进行相应处 理,对地面进行错误报告,因而CPU处理时间很短,节省了宝贵的CPU资源。

3.3 仿真与验证

在空间环境下普遍存在的SEU,在地面环境下是很难获得的,为了在地面对该EDAC电路 设计进行验证,需要采取故障注入手段。由于在本例中RAM存储单元采用FPGA内部资源,因 此故障注入变得相对简单。在FPGA进行程序综合时,可将预先编制好的RAM存储单元初始化 文件一起综合。因此我们可在编制RAM存储单元初始化文件时,对某些比特位进行修改,以 模拟空间环境下SEU对RAM存储单元的影响。

在这里采用Xilinx公司的XQRV300为硬件载体,该型号FPGA芯片在航天领域内被广泛使 用。为节省仿真时间,数据RAM存储单元采用256*8bit,检验RAM存储单元采用25*bit。在 RAM存储单元初始化文件中,人工加入了12个单比特错误,以及1个两比特错误,如下表所示。

为仿真简便起见,向存储单元存放的正确数据与存储单元地址相同。

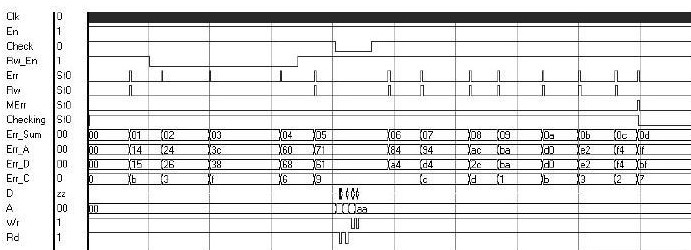

时钟选择为20MHz,通过采用ModelSim软件进行布线后仿真,我们可以得到图3所示结果。

图中: Clk — 系统时钟;

En — EDAC 模块使能控制;

Check — 自检启动/使能信号(信号上升沿触发一次巡检,信号为低暂停巡检);

Rw_En — 自纠错使能信号(为高允许纠错);

Err — 错误中断(标志)信号;

Rw — 自纠错标志信号(为高表示正在进行自纠错操作);

MErr — 多比特错误中断(标志)信号;

Checking — 自检标志(为高表示尚未完成本次巡检操作);

Err_Sum,Err_A,Err_D,Err_C — 错误计数,错误地址,原始数据,原始校验码;

D,A,Wr,Rd — 单片机数据、地址、写操作、读操作信号;

从图中可以看出,启动EDAC自检后,EDAC开始巡检RAM存储单元,产生错误中断(标志) 信号,给出错误信息。当单片机需要处理中断时,将Check信号置‘0’,可暂时停止巡检, 此时单片机可对RAM存储单元进行正常读写操作。等中断处理完后,单片机将Check信号置 ‘1’,恢复RAM巡检操作。

另外可通过Rw_En的置‘0’或‘1’,来控制禁止或允许进行自纠错操作。

当出现可识别的多位错误时,产生Err和MErr两个错误中断(标志)信号,但由于汉明码仅能纠正单比特错误,因此不进行自纠错操作。

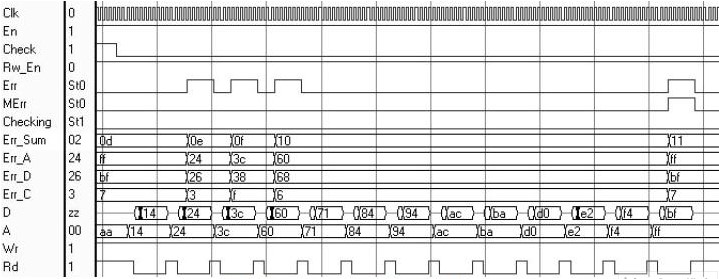

从原注入错误数据对应的地址读出数据,仿真输出结果如图4所示。

可以看出除最后一个地址(FFH)由于两位错仍输出错误外,其他地址输出数据均与地址相同,即为正确数据。

其中,24H、3CH、60H三个地址虽然输出正确数据,但仍报错,表明存储器内数据仍然 为错误数据,在输出时进行了纠错。这是由于在上次巡检到这部分地址空间时,通过把Rw_En 信号拉低,从而禁止了自动纠错,导致这三个地址错误数据未被纠正。而在对其他地址进行 数据读取时,未产生错误标志,证明其他错误数据已被纠错。

4 结论

本文在采用FPGA芯片实现基本EDAC读写功能的设计思路基础上,创建了一种新型的可对 RAM存储单元进行自检的EDAC功能模块。该模块不但可以对RAM存储单元进行快速巡检,巡检 时间仅为传统EDAC方法的十二分之一,还可以自动纠正已发现的错误。该模块最大的优点在 于节省了单片机资源,几乎不需要单片机的参与即可完成所有自检功能,从而使基于FPGA 的星载计算机对SEU事件防护能力得到较大的提升。本文中该模块采用Verilog硬件描述语言 编程,具有可移植性,这种设计方法可用于各种体系结构的星载计算机中。

-

FPGA

+关注

关注

1629文章

21729浏览量

602998 -

RAM

+关注

关注

8文章

1368浏览量

114641 -

计算机

+关注

关注

19文章

7488浏览量

87850

发布评论请先 登录

相关推荐

移动通信中变速率自纠错解码器设计

S698M SoC芯片中EDAC模块的设计与实现

基于FPGA的星载计算机自检EDAC电路设计

计算机RAM检错纠错电路的设计与实现

基于FPGA的检纠错逻辑算法的实现

用FPGA实现纠错编码的一种方法

FPGA的硬件电路设计教程和FPGA平台资料简介

FPGA最小系统配置电路设计与实现

FPGA_ASIC-S698MSoC芯片中EDAC模块的设计与实现

FPGA-SoC芯片中EDAC模块的设计与实现

基于FPGA实现具有自检、自纠错功能的EDAC电路设计

基于FPGA实现具有自检、自纠错功能的EDAC电路设计

评论