1 引言

按键作为普通的输入外设,在仪器仪表工业设备和家用电器中得到广泛应用。目前,按键输入电路Ⅲ主要有2种:一种是非扫描方式可以判断多键状态(允许多键同时动作),但是不适用于大量按键情况,所需I/0端口多;另一种是扫描阵列方式,适用于大量按键,但不能多键同时动作。因此,需要开发一种既适合大量按键又适合多键同时动作,并能节省单片机(MCU)的口线资源的多按键状态识别系统。这里提出一种利用FPGA的I/0端口数多和可编程的特点,采用VHDL语言的多按键状态识别系统,实现识别60个按键自由操作,并简化MCU的控制信号。

2 系统设计方案

FPGA是一种可编程逻辑器件,它具有良好性能、极高的密度和极大的灵活性,外围电路简单可靠等特性。因此,该系统设计是由MCU、FPGA、按键等部分组成。60路按键信号进入FPGA单元,以供数据采集;FPGA处理采集到的数据信号,编码后写入内部FIFO。MCU通过I/O端口提取FIFO中的数据。模块通过电源接口向各个部分供电。其系统设计原理框图如图l所示。

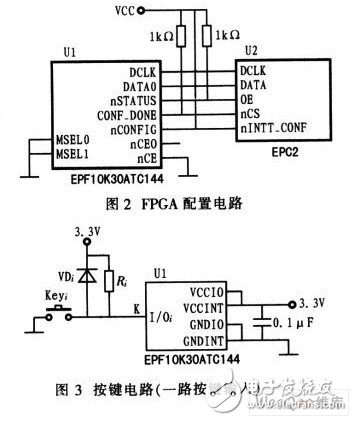

2.1 FPGA配置电路

FPGA采用Altera公司EPF10K30ATC144,该器件内核采用3.3 V供电,端口电压为3.3V可承受5 V输入高电平,其工作频率高达100 MHz;有102个可用I/0端口,每个端口输入电流最高达25 mA,输出电流达25 mA;l728个逻辑单元(Les),12 288 bit的用户Flash存储器,可满足用户小容量信息存储,完全满足系统设计要求。

由于FPGA基于RAM工艺技术,该器件丁作前需要从外部加载配置数据,需要一个外置存储器保存信息,采用可编程的串行配置器件EPC2.其供电电压为3.3 V。OE和nCS引脚具有内部用户可配置上拉电阻。FPGA的DCLK、DATA0、nCONFIG引脚信号均来自EPC2。系统上电后,首先FPGA初始化,nSTATUS、CONF_DONE置为低电平。nSTATUS置为低电平后复位,此时EPC2的nCE为低电平,因此选取EPC2,从而数据流从DATA引脚输入到FPGA的DATAO引脚。配置完成后,FPGA将CONF_DONE置为高电平,而EPC2将DATA引脚置为高阻态。其FPGA配置电路如图2所示。

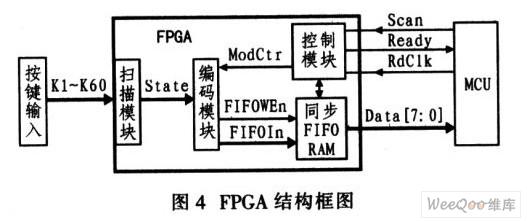

2.2 按键电路

图3为一路按键电路,共60个按键(i=1~60)。由于外界环境复杂,按键引线长达6 m,保护二极管VDi:在外界干扰信号大于VCC时导通起到保护FPGA的作用。电阻Ri上拉限流,按键未闭合状态下FPGA输入引脚始终处于高电平。

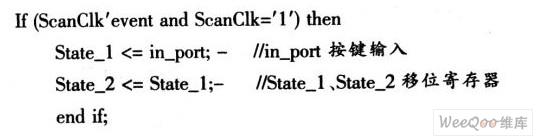

3 FPGA内部逻辑设计

FPGA内部功能分为扫描模块、编码模块、控制模块以及同步FIFO RAM模块,如图4所示。

图4中,K1~K60为60个按键的输入端,Scan为工作模式选择信号,Ready为读准备好信号,RdClk为读时钟信号,Data[7:0]为数据输出,ModCtr为编码模式控制信号,FIFOWEn为FIFO RAM写使能信号,FIFOIn为FIFO RAM数据输入,State为按键状态扫描信号。其工作原理为:扫描模块周期扫描按键状态,其结果送入编码模块;编码模块根据模式控制信号ModCtr选择编码方式编码,将其结果送入FIFO RAM;控制模块产生对FIFO RAM的读取控制信号;MCU可通过Readv、RdClk控制信号读取Data[7:0]数据线上的按键编号和状态数据。

3.1 扫描模块

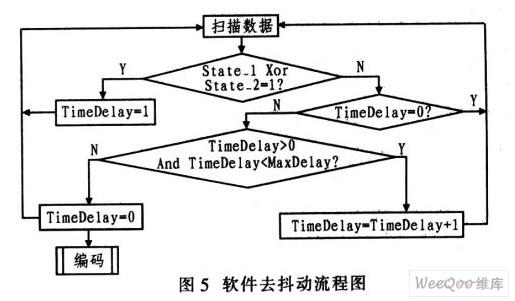

扫描模块主要完成扫描按键状态输入和按键的软件去抖动。扫描按键状态输入是以5 m8为周期扫描60个输入引脚,将其结果存入60个两位状态移位寄存器。其代码为:

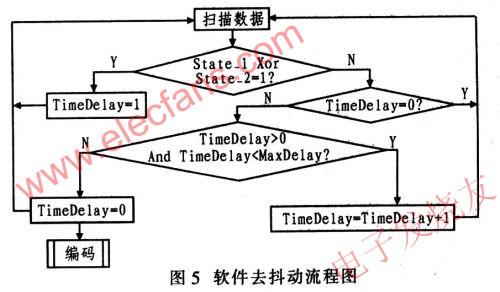

按键去抖有硬件和软件2种实现方式。为了节省成本,充分发挥FPGA器件的功能,该系统设计采用软件去抖。图5为软件去抖动流程。图中State为2位状态移位寄存器,初始值为0,TimeDelay为延时计数器。

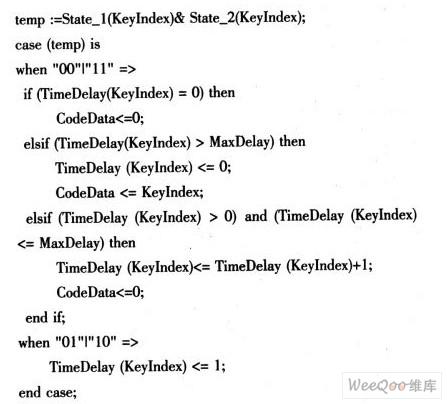

软件去抖动过程说明:对状态寄存器的2位数值做异或运算,即m=State_1 Xor State_2。若m=l,说明按键有动作,则令TimeDelay=1,启动延时计数;若m=O,表明按键处于去抖延时或者平稳状态。这时判断TimeDelay,若TimeDelay=0,则按键处于平稳状态;若0MaxDelay时说明按键已经平稳,将结果送入编码器模块。软件去抖关键代码如下:

3.2 编码模块

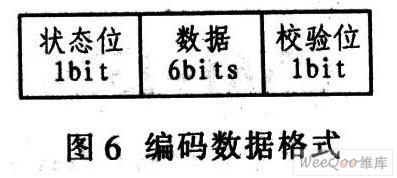

以0、l表示按键通断状态,60个按键则需要8个字节;在实际中单键动作的概率远远大于多键同时动作的概率,若只对状态发生变化的按键以8位编码方式传输按键信息,则一个按键只需传送一个字节,因此为尽可能地减少MCU的负担,提高实时性,设计为只在按键发生状态变化时才向MCU传输相应按键的编号和状态数据。其编码数据格式如图6所示。

状态位lbit,0表示按键闭合状态,1表示按键打开;数据6bits,即0X01~OX3C分别表示1~60个按键;lbit偶校验位。这样传输一次数据就可完成按键编号和状态的传输。

编码器采用连续和随机2种工作模式。连续工作模式每次扫描后对所有按键依次编码,并获取所有按键的当前状态;而随机工作模式在每次扫描后只对状态发生变化的按键编码。

3.3 控制模块

控制模块完成MCU与FPGA之间的功能控制,有2个作用:一是根据Scan信号选择编码模块的工作模式,二是产生FIFO RAM的读取操作时序。

对于模式控制,Scan上升沿触发控制模块,使编码模块进入连续工作模式,扫描完成一周,控制模块发送控制信号使编码模块进入随机工作模式。

对于读取数据,控制模块根据FIFO RAM的Data[7:0]是否有数据,置位Ready信号。有数据,Ready为低电平;无数据,Ready为高电平。RdClk为读取时钟,相当于确认信号,每读完一个数据,发送一个脉冲。

3.4 FIFORAM模块

与MCU通信的接口种类很多,可选择串口、I2C、并口等形式,应用中可根据MCU资源以及项目成本、进度等具体情况选择最合适的一种方式。该系统设计利用同步FIF0 RAM并口传输。FIF0 RAM模块采用EDA软件库中的标准模块。

4 仿真结果

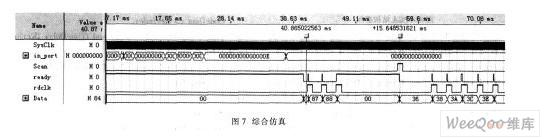

采用Altera公司提供的Quartus II仿真工具,其集成有与硬件实时操作相吻合的硬件测试工具。综合仿真结果如图7所示,系统时钟SysClk为12 kHz,其仿真结果表明系统设计达到要求。

5 结论

提出基于FPGA器件,VHDL语言描述的特殊键盘设计方案解决远距离、分散、多键动作状态识别问题,极大节省PCB面积和MCU的I/0端口资源。模块中扫描延迟、扫描间隔等参数可根据系统需求灵活改变,FPGA器件使得电路功能的扩展方便,具有极高稳定性和灵活性。这一方案已在实际项目中应用,经现场验证性能稳定可靠。

-

FPGA

+关注

关注

1629文章

21736浏览量

603290 -

vhdl

+关注

关注

30文章

817浏览量

128134 -

按键

+关注

关注

4文章

223浏览量

57601

发布评论请先 登录

相关推荐

如何利用FPGA设计多按键状态识别系统?

如何利用FPGA技术设计多按键状态识别系统?

如何利用FPGA和VHDL语言实现PCM码的解调?

关于通过FPGA中VHDL语言实现ALU的功能设计详解

采用FPGA器件EPF10K30ATC144和VHDL语言实现多按键识别系统的设计

利用FPGA与VHDL语言实现多按键状态识别系统设计

利用FPGA与VHDL语言实现多按键状态识别系统设计

评论