DDS同 DSP(数字信号处理)一样,是一项关键的数字化技术。DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。DDS在结构上由三部分构成:⑴ 累加器;⑵ 角度幅度转换器,它将数字相位值转换为数字幅度值;⑶ 数模转换器。ADI公司所有DDS的DAC都是电流输出形式。DDS频率规划是指在应用范围内提供最佳动态性能的一种尝试,对于许多应用来说,这就意味着在感兴趣的带宽内提供最大的无杂散动态范围,或者称作SFDR.为了获得最大的SFDR值,需要进行一些DDS频率规划。一个好的频率规划首先是要根据应用所给定的性能标准选择合适的DDS器件,然后规划并预算出DDS的主要杂散源

不同的应用领域,对DDS的性能有不同的要求。当把DDS用做雷达系统中的本振信号源时,对寄生信号抑制的要求可能比较高,如要求在60dB或70dB以上。当把DDS用于雷达干扰系统时,除了对寄生信号抑制有一定的要求外,更重要的是其产生宽带信号的能力。为了产生宽带信号,要求DDS的系统时钟频率要高。尽管目前FPGA的速度和规模都已经达到了相当高的水平,但与电子干扰系统对它的要求相比仍有差距。按照目前FPGA的技术水平及使用经验,系统时钟选择200MHz是一个比较合理的选择。因此,为了满足电子干扰系统更高(如400MHz系统时钟)的要求,应该采用并行处理技术。

1 并行DDS电路工作原理

并行处理(Parallel Processing)是计算机系统中能同时执行两个或更多个处理机的一种计算方法。处理机可同时工作于同一程序的不同方面。并行处理的主要目的是节省大型和复杂问题的解决时间。为使用并行处理,首先需要对程序进行并行化处理,也就是说将工作各部分分配到不同处理机中。而主要问题是并行是一个相互依靠性问题,而不能自动实现。此外,并行也不能保证加速。但是一个在 n 个处理机上执行的程序速度可能会是在单一处理机上执行的速度的 n 倍。

图1所示为并行DDS电路工作原理框图,主要包括:相位累加器、两路相位/幅度变换电路、二选一选择器、锁存器、SINC函数补偿滤波器、D/A变换器和中频滤波器。相位累加器通过对输入频率码的累加,产生A、B两路相位累加输出,其中A路信号在前,B路信号在后(两路信号合成一路信号后)。两路相位/幅度变换电路分别对两路相位累加器输出的相位进行相位/幅度变换,获得两路幅度输出。然后由二选一选择器将两路信号合并成一路信号(S=0时选A,S=1时选B)。相位累加器、相位/幅度变换电路的时钟以及选择器选择端S的信号为fck1,它是由DDS电路系统时钟fck分频得到,即fck1=fck/2.而选择器后面的锁存器以及SINC函数补偿滤波器、D/A变换器的时钟为系统时钟。为了简化电路实现,采用直接中频方法取出D/A变换器的中频信号输出,同时,为了补偿D/A变换输出信号幅度随频率增加引起的衰减,图1中增加了SINC函数补偿滤波器。图2给出了fck1、fck与数据之间时序关系的示意图。

2 并行DDS电路实现

主要介绍相位累加器电路和相位/幅度变换器电路的实现。

2.1 相位累加器电路实现

实现并行相位累加器的直接方法是:由两套结构完全相同的相位累加器电路构成,相位累加器的输入(频率码)也相同,只是两路输出要有一个固定的初始相位偏差,其数值为相位累加器输入(频率码)的1/2.

为了电路实现容易,需对上述方法进行简化。这里提供一种较为简单的方法,即利用一个相位累加器产生第一路(A路)相位累加器输出,而另一路相位累加器输出通过将第一路输出的相位与相位累加器输入(频率码)的1/2相加得到,如图3所示。在图3中,假定系统时钟为400MHz,假定输入的频率码为26位,范围为F[25:0],其中位25代表200MHz,位24代表100MHz,…,位0为最低有效位,也就是DDS的分辨率fck/226=5.96Hz.

相位累加器电路中各器件的时钟频率为fck1=200MHz.相位累加器的输入取26位频率码F[25:0]的低25位F[24:0],即得到A路相位累加器的输出为A[24:0].F[25:0]的高25位F[25:1]经右移一位(相当于乘1/2)得到C[24:0]后与A路相位累加器的输出A[24:0]相加得到B路相位累加器的输出B[24:0].

最后,为了减小后面相位/幅度变换电路的硬件量,锁存器只取出用于进行相位/幅度变换所需位数的相位(相位截断),这里取相位截断输出为10位,A路为G[9:0],B路为H[9:0].

2.2 相位/幅度变换器电路实现

相位/幅度变换电路的功能是把由相位累加器输出的相位信息转换成幅度信息。相位/幅度变换电路通常采用ROM电路实现,但也可采用数字逻辑电路实现。

并行相位/幅度变换器由两套结构完全相同的相位/幅度变换器构成,因此,下面只介绍其中的一个。相位/幅度变换的原理可以很容易由ROM构成的查找表(LUT)理解。相位/幅度变换的内容存储在ROM中,以相位值作为ROM的地址,ROM的输出作为变换后的幅度。

与相位累加器不同,相位/幅度变换器的硬件量随相位位数(ROM地址)的增加指数增加,而相位累加器硬件量随累加器位数的增加线性增加。因此,当相位位数(影响DDS的寄生信号性能)较大时,所需硬件量将急剧增加。尽管前面已经对相位进行了截断,但为了保证所需的寄生信号性能,剩下的用于进行相位/幅度变换的相位位数仍然较大,如果直接实现所需硬件量仍然较大。

下面两种方法对减小硬件量比较有效。一是根据SIN函数的对称性,只需要对一个象限进行相位/幅度变换,另外三个象限可以经变换获得,这样可节省近3/4的硬件量[3];第二种是采用分段线性化的方法,也可有效降低ROM地址的位数[4].

以一个10位相位/8位幅度的相位/幅度变换电路为例,介绍相位/幅度变换电路的具体实现方法并分析硬件量节省的情况。图4是分段线性化相位/幅度变换方法示意图。曲线1是用于进行相位/幅度变换的原始正弦信号前1/4周期(第一象限)的曲线,将它分解成下面的3条曲线(曲线2、3、4)。曲线2是粗相位/幅度变换对应的曲线。曲线3和4分别对应的是线性变化部分(只有0、1、2三个值,即2位)和校正部分(只有0、1两个值,即1位)。注意,为了清楚,曲线3和4的幅度都放大了5倍,并分别下移10和20.

根据图4的方法,图5给出了相位/幅度变换电路原理框图。相位输入10位,幅度输出8位,分析中假定忽略掉两组异或门和一个加法器所占用的硬件资源。在不采用任何措施以节省硬件资源的情况下,地址为10位,输出幅度为7位(幅度的最高有效位不需要ROM资源),所需硬件量(ROM容量)为:210×7=7168.当利用SIN函数的对称性只对第1象限进行相位/幅度变换时,地址由10位变成了8位,所需硬件量变为:28×7=1792,减小了75%.在第1象限的相位/幅度变换中进一步采用分段线性化的方法,将一个较大的ROM(地址8位,字长7位)分解成三个较小的ROM:一个粗相位/幅度变换(地址6位,字长7位),一个分段线性变化部分(它只与最高两位和最低两位地址有关,地址4位,字长2位),还有一个校正部分(地址8位,字长1位)。因此,所需硬件总容量变为:26×7+24×2+28×1=736,又减小了近59%.可见,综合采用上述两种方法,可以使相位/幅度变换所需的硬件量大幅度减小。

根据具体情况和具体要求的不同,分解方法并不局限于上面介绍的方法。以图5为例,由于线性变化部分和校正部分都较小,因此也可以将二者合并成一个地址8位、字长2位的校正部分,这时,所需硬件总容量为:26×7+28×2=960,减小的硬件量为46%。

3 实验测试结果

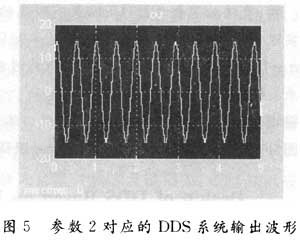

为了满足电子干扰系统对宽带信号产生的需要,按照上述方法设计并实现了一个基于FPGA的并行DDS样机,系统时钟400MHz(两路200 MHz构成),输出频率范围250MHz~350MHz,频率分辨率6Hz,相位截断10位,D/A变换器幅度分辨率8位。

为了简化外部电路,采用了直接中频输出的方法,即直接取出频率范围250MHz~350MHz的信号。由图6可以看出,由于D/A变换器输出信号幅度随频率按SINC函数衰减,在输出信号250MHz~350MHz频率范围内,幅度变化范围较大,约为(-6.5)~(-17.1)=10.6dB.因此,电路中还包含了SINC函数补偿滤波器。

根据文献[5],10位相位/8位幅度DDS的最高寄生信号抑制为-60.2dB.不过,这只是在特定条件下的理想结果,实际的DDS寄生信号性能还受到采样信号频谱折叠、D/A变换器采样脉冲不理想(不是理想的冲击脉冲)等因素的影响。特别是当输出信号频率较高时,D/A变换器非线性的影响更不能忽视。因此,实际测量结果与理论分析会有所不同。图7给出的是基于FPGA的并行DDS样机的输出信号频谱分布测量结果,输出信号约为300MHz,测量范围是在信号附近(span=1MHz),此时的最大寄生信号抑制优于50dB。

本文介绍了一种通过采用并行处理技术提高DDS系统时钟的方法,给出了一个基于FPGA的400MHz系统时钟DDS电路的实现方法和测试结果,输出信号频率范围250MHz~350MHz,频率分辨率6Hz,寄生信号抑制优于50dB,为实现雷达和电子战等领域中的宽带信号产生提供了一种可供选择的方案,具有实用性。

-

转换器

+关注

关注

27文章

9464浏览量

157211 -

频率合成器

+关注

关注

5文章

370浏览量

33984 -

雷达

+关注

关注

52文章

3429浏览量

124724 -

DDS

+关注

关注

22文章

688浏览量

156986

发布评论请先 登录

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化...

FPGA实现高速FFT处理器的设计

基于DDS原理和FPGA技术的基本信号发生器设计

如何利用现场可编程逻辑门阵列FPGA实现实现DDS技术?

基于DSP Builder的DDS设计及其FPGA实现

低成本的采用FPGA实现SDH设备时钟芯片技术

基于FPGA的振动信号采集处理系统设计并实际验证

通过FPGA与并行处理技术实现DDS系统时钟电路

通过FPGA与并行处理技术实现DDS系统时钟电路

评论