1 引言

在现代航空通讯过程中,通讯信息量比较大,传输过程中容易出现诸多问题。在现有的磁带记录仪、数字处理专用机,动态参数记录仪等设备,因技术、存储容量、记录速度、记录的准确性等方面都有很大的缺陷和不足。为对存在于航空通讯的诸多问题,诸如通讯误码、中断故障等做到及时掌握,查找原因,改进通讯质量,利用成熟的数字处理技术(DSP),基于TI 公司的TMS320F2812,设计了本通讯信息记录系统。此通讯信息记录系统主要包括信息管理、信息存储、信息下载(后续开发)等部分组成。在设计过程中,主要使用到了CCS2000 开发工具和一些辅助试验设备。DSP 是基于可编程超大规模集成电路和计算机技术发展起来的一门重要技术,可广泛应用于通信控制、信号处理、仪器仪表、医疗、家电、军事、工业检测、控制及消费类产品。DSP 芯片的快速数据采集与处理功能以及片上集成的各种功能模块为DSP 应用于各种场合提供了可能。在设计过程中,考虑到航空通讯的特殊要求,例如飞行时间,特殊的使用环境,及记录设备与外界的链接,对存储芯片都是一种特殊的要求,在以往的磁带记录仪、数字处理专用机等设备和器材中,一些体积大,存储容量受限等因素利用DSP 可以得到很好的解决。

2 C2000 系列DSP 平台及TMS320F2812 简介

在系统开发过程中,需要一整套完整的软硬件开发工具。利用TI公司推出的用于TM320系列DSP的软件集成环境(IDE)。CCS工作在Windows操作系统下,类似于VC++的集成开发环境,采用图形接口界面,提供编辑工具和管理工具。他将多种代码产生工具汇编器,链接器,C/C++编译器,建库工具等集成在一个统一的开发平台中,并且CCS具有开放式的架构,使TI和第三方能通过无缝插入附加专用工具来扩张IDE功能。CCS所集成的代码调试工具具有各种调试功能,包括原TI公司提供的C/C++源代码调试器和模拟器所具有的所有功能,他能对TMS320系列DSP进行指令级的仿真和可视化的实时数据分析。此外还提供了丰富的输入、输出库函数,从而极大的方便了TMS320系列DSP的软件开发过程。

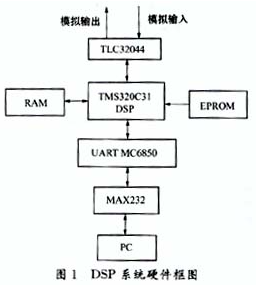

本文是基于DSP和FPGA为核心的,结合数模转换电路、缓存器、FLASH存储器等元器件,设计的通讯信息存储记录系统。TMS320F2812 是TI公司主推的一款高性能32位定点DSP 控制器。采用先进的体系结构,具有低功耗、运行速度快和片内资源丰富的特点,在数字控制领域有着广泛的应用。它的主要特点有:

(1) 工作频率高达150MHz(时钟周期6.67ns),实时处理能力强,能应用于很多复杂的控制算法。

(2) 内含高性能32 位CPU,同时包含2个16 ×16位乘累加器,可以方便地运行16×16位和32×32的乘法累加操作,可满足高精度与快速计算的要求。

(3)具有16 通道高性能12 位的带流水线的模数转换器(ADC),提供了两个采样保持电路,可以实现双通道信号的同步采样。

(4 )片上含两个事件管理器(EVA 和EVB)可设计用于自身和FPGA的对通讯信息的管理控制等。

(5) 完善的外围接口,包括1 个串行外围接口(SPI)、2个串行通信接口(SCIs)、1个标准的UART 接口、1 个eCAN 接口和多通道缓冲串行接口(McBSP)等。

3 记录系统硬件电路原理设计

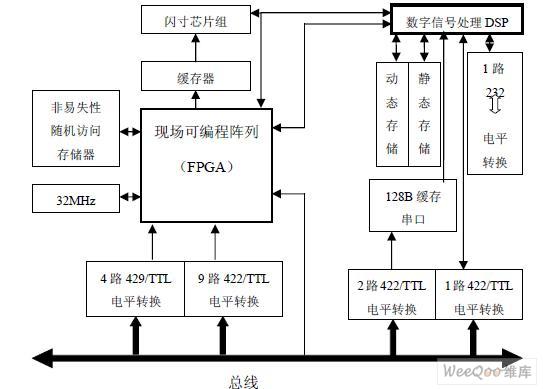

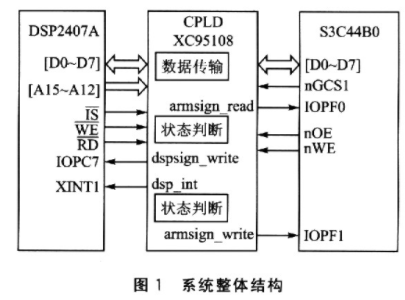

记录系统中通信管理设备与显示设备的2 路422 数据由DSP 负责接收、分析、组织并转存至FLASH 芯片(使用3 片)中,其余9 路422 数据和4 路429 数据由FPGA 负责接收、组织并转存。FPGA 共有4 个FLASH 接口,除了接口4 控制4 片FLASH 之外,每个接口控制3片FLASH。图 1 是 系统的原理框图。

图 1 系统的原理框图

当记录系统处于工作状态(GSE# = 0)时,FPGA 和DSP 接收各个通道的数据,进行缓存、组织和写入(DSP 还要对接收到的数据进行分析,仅记录控制字,如果是数据就直接丢弃)。为了能够实现循环存储并且在擦除旧数据时不丢失新的数据,每个通道的数据都组织为定长为64 字节的数据块,其中第1 个字节为通道标识(因传感器的通道比较多,设备繁杂在相应的通道加上通道标识),余下的63 字节为真实的数据和时标信息,这个定长数据块是不可分割的,所有通道的数据按顺序存储到自身所在的FLASH 接口所控制的FLASH 芯片中,假定该接口有3 片FLASH 存储器,使用第1 片存储器时检查第2 片存储器是否可用,如果不可用,则向第2 片存储器发送擦除命令;同理,使用第2 片存储器时检查第3 片存储器是否可用,如果不可用,则向第3 片存储器发送擦除命令;使用第3 片存储器时检查第1片存储器是否可用,如果不可用,则向第1 片存储器发送擦除命令;这样就实现了循环存储且保证丢掉的数据是最旧的数据。这样的存储方式要求有较大容量的缓存,在FPGA 内实现较为困难,因此使用外挂FIFO。

当记录系统处于非空中工作状态(GSE# = 1)时,DSP 通过422 接口与外围主处理系统进行通信,如果需要获取数据,DSP 首先获得各接口当前存储数据的具体空间,然后读出数据进行解析。如果需要对数据进行擦除,对于自己管理的3 片FLASH,DSP 直接执行擦除命令,对于FPGA 管理的13 片FLASH,DSP 通过与FPGA 之间的命令接口执行擦除命令。共使用了16 片FIFO,1GB 容量均分到每个芯片,单芯片的容量需达到64M(512Mbit),这样大容量的NOR 型FLASH 目前有AMD 公司的S29GL-P 系列和S70GL-N 系列,典型的写数据速率为32B*106/(240+21)s ≈ 122.6KB/s,但目前考虑到货源问题,无法做到系统设备的大批量生产,因此采用管脚兼容的AM29LV256M,总容量为512MB。

1 时钟:记录模块使用了三种时钟,其频率分别是33MHz、7.3728MHz 和30MHz,33MHz时钟提供给FPGA 内部逻辑使用,可分频产生毫秒计数时钟和429 总线用时钟。

2 复位电路:记录模块复位包括上电复位、外部复位及DSP 复位。任意复位信号有效时均能复位整个模块,除了FLASH 芯片,FIFO 芯片和DSP 之外,无其它资源需要在复位时处于特定状态,因此只需考虑对FPGA 内部逻辑和DSP、FLASH 芯片的复位。如图2 复位电路示意图。

图 2 复位电路示意图

3 模块电压:记录模块使用7 种电压,+/-12V、5V、 3.3V、1.8V、1.9V 和2.5V。

4 看门狗电路:DSP内部包含看门狗定时器,可通过软件设置超时周期,并提供了使能/禁止看门狗的功能。

5 电平转换:429电平转换芯片使用2片HOLT公司的HI-8482双通道接收器,422电平转换芯片使用3片MAXIM公司的MAX309*通道接收器和1片MAXIM公司的MAX3491四通道发送器。

其中429电平转换后的5V信号不能直接接入FPGA,需要用兼容3.3V/5V工作电压的驱动器进行隔离。

6 FIFO:用于缓存接收到的数据,选用IDT 公司的IDT72V05,单片容量为8K*8。每个FLASH 接口需要2 片,共需8 片。

7 NVSRAM:NVSRAM 用于保存FLASH 存储空间的起始地址和结束地址,保证在下电后该信息不丢失,选用SIMTEK 公司的STK14C88-3。容量为32K*8bit。

8 FPGA:FPGA 的功能是将接收到的4 路429 和9 路422 数据分别缓存,分别写入。每隔10ms 时标生成插入单元会给缓存队列插入相对时标,在软件解析时,结合GPS 通道传送的日历时间可还原出各通道各数据包的绝对时间(精度为10ms)。

9 地址空间分配:TMS320F2812 通过其外部扩展接口访问外扩RAM 和FPGA 内部寄存器及FLASH 空间,该外部接口映射到5 个独立的存储空间,当访问相应的存储空间时,会产生一个片选信号;每个空间都可以独立地设置访问建立、激活及跟踪时间。还可以使用XREADY信号来控制外设的访问。记录模块各单元所在存储空间分配依据要求进行分配。

4 记录系统软件设计

根据通讯协议、全双工通信方式、通信速率(115.2 Kbps)、传输数据格式以及数据包结构。数据包结构如下表:

其中,数据类型用以标识信令的种类;数据长度为转义前消息数据与校验和字节的总数;校验和为消息中不含开始与结束标志的其余字节的CRC 校验,占2 个字节,CRC 算法按定义;数据流向从左至右发送数据包的每个字节,每一个字节从低位至高位发送。如:C0 的发送顺序为:0,0,0,0,0,0,1,1。

通信协议:SLIP 是一个简单的面向字符的协议。在每个用户信息帧的首尾各加-个特殊的标志字节 END ,封装成为 SLIP 帧。标识字节 END 的编码为(C0H)。若用户信息帧中的某一个字节与(C0H)一样,那么将这一个字节更换成(DBH, DCH)。这里的特殊字符(DBH)称为SLIP 转义字符。若用户信息帧中的某个字节与(DBH)一样,那么将这一个字节再更换成(DBH, DDH)。严格按照应用软件的开发流程,结合信息在记录设备中的传输,开发软件,并对各种需求功能就行开发.开发的部分源程序:

5 创新点

首次采用TMS320F2812 结合AM29LV256M,采用的是现今国内最大的记录芯片,设计航空通信信息记录系统,实现了对通讯数据的实时记录,设计出的记录系统性能稳定,可靠性高,存储量更大,记录时间更长,经第三方验证,通过对容错能力的实验,错误率低于标准要求。首次完成了在航空通讯领域原始数据问题纪录的空白。在存储芯片的选择上,随着技术的发展和改善,这一系统将得到完善和发展。设计基本达到了预期要求,满足了需求,并在航空通讯装备建设中得到了批量运用,产生的经济效益巨大。

-

dsp

+关注

关注

561文章

8287浏览量

368884 -

FPGA

+关注

关注

1664文章

22545浏览量

640413 -

芯片

+关注

关注

463文章

54593浏览量

470594 -

编译器

+关注

关注

1文章

1673浏览量

52052

发布评论请先 登录

FPGA与DSP的高速通信接口设计与实现

采用CAN总线与RS-485实现DSP通信接口

FPGA与DSP的高速通信接口设计与实现

采用DSP实现网络通信接口设计

采用DSP实现网络通信接口设计

通过FPGA实现温控电路接口及其与DSP通信接口的设计

航空总线接口通信系统的设计与实现

航空图像压缩系统的DSP设计方案解析

DSP系统程序远程更新的研究与实现

基于TMS320F2812 DSP芯片的航空电源稳定性自我测试诊断方案

采用DSP芯片实现航空通信记录系统的设计

采用DSP芯片实现航空通信记录系统的设计

评论