1.引言

在信息信号处理过程中,如对信号的过滤、检测、预测等,都要使用滤波器,数字滤波器是数字信号处理(DSP,DigitalSignalProcessing)中使用最广泛的一种器件。常用的滤波器有无限长单位脉冲响应(ⅡR)滤波器和有限长单位脉冲响应(FIR)滤波器两种,其中,FIR滤波器能提供理想的线性相位响应,在整个频带上获得常数群时延从而得到零失真输出信号,同时它可以采用十分简单的算法实现,这两个优点使FIR滤波器成为明智的设计工程师的首选,在采用VHDL或VerilogHDL等硬件描述语言设计数字滤波器时,由于程序的编写往往不能达到良好优化而使滤波器性能表现一般。而采用调试好的IPCore需要向Altera公司购买。采用了一种基于DSPBuilder的FPGA设计方法,使FIR滤波器设计较为简单易行,并能满足设计要求。

2 FIR滤波器介绍

2.1 FIR滤波器设计的原理

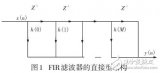

FIR滤波器的数学表达式可用差分方程(1)来表示:

其中:r是FIR的滤波器的抽头数;b(r)是第r级抽头数(单位脉冲响应);x(n-r)是延时r个抽头的输入信号。

设计滤波器的任务就是寻求一个因果,物理上可实现的系统函数H(z),使其频率响应H(ejw)满足所希望得到的频域指标。

2.2 设计要求

数字滤波器实际上是一个采用有限精度算法实现的线性非时变离散系统,它的设计步骤为先根据需要确定其性能指标,设计一个系统函数H(z)逼近所需要的技术指标,最后采用有限的精度算法实现。本系统的设计指标为;设计一个16阶的低通滤波器,对模拟信号的采样频率fs为48KHz要求信号的截止频率fc=10.8kHz输入序列位宽为9位(最宽位为符号位)。

3 DSPBuilder介绍

DSPbuilder是Altera推出的一个DSP开发工具,它在QuartusⅡFPGA设计环境中集成了Mathworks的Matlab和simulinkDSP开发软件[2]。

以往Matlab工具的使用往往作为DSP算法的建模和基于纯数学的仿真,其数学模型无法为硬件DSP应用系统直接产生实用程序代码,仿真测试的结果也仅仅是基于数学算法结构。而以往FPGA所需的传统的基于硬件描述语言(HDL)的设计由于要考虑FPGA的硬件的δ延时与VHDL的递归算法的衔接,以及补码运算和乘积结果截取等问题,相当繁杂。

对DSP是Builder而言,顶层的开发工具是MatLab/Simulink整个开发流层几乎可以在同一环境中完成,真正实现了自定向下的设计流程,包括DSP系统的建模、系统级仿真、设计模型向VHDL硬件描述语言代码的转换、RTL(逻辑综合RegisterTransferLevel)级功能仿真测试、编译适配和布局布线、时序实时仿真直至对DSP目标器件的编程配置,整个设计流程一气呵成地将系统描述和硬件实现有机地融为一体,充分显示了现代电子设计自动化开发的特点与优势。

4 FIR数字滤波器的DSPBuilder设计

4.1 FIR滤波器参数选取

用Matlab提供的滤波器设计的专门工具箱———FDATool仿真设计滤波器,满足要求的FlR滤波器幅频特性如图1,由于浮点小数FPGA中实现比较困难,且代价太大,因而需要将滤波器的系数和输入数据转化为整数,其中量化后的系数在Matlab主窗口可直接转化,对于输入数据,可乘上一定的增益用Altbus控制位宽转化为整数输入。

4.2 FIR滤波器模型建立

根据FIR滤波器原理,可以利用FPGA来实现FIR滤波电路,DSPBuilder设计流程的第一步是在Matlab/Simulink中进行设计输入,即在Matlab的Simulink环境建立一个MDL模型文件,用图形方式调用AlteraDSPBuilder和其他的Simulink库中的图形模块,构成系统级或算法级设计框图(或称Simulink建模),如图2所示。

4.3 基于DSPBuilder的滤波器仿真

输入信号分别采用频率f1=8KHz和f2=16KHz的两个正弦信号进行叠加。其中的仿真波形如图3所示,从FIR滤波电路的仿真结果看出,输入信号通过滤波器后输出基本上变成单频率的正弦信号,进一步通过频谱仪可看出f2得到了较大的抑制,与条件规定的fc=10.8kHz低通滤波器相符合,至此完成了模型仿真。

4.4 运用Modelsim进行功能仿真

在Simulink中进行的仿真是属于系统验证性质的,是对MDL文件进行的仿真,并没有对生成的VHDL代码进行过仿真。事实上,生成VHDL描述是RTL级的,是针对具体的硬件结构的,而在Matlab的Simulink中的模型仿真是算法级(系统级)的,是针对算法实现的,这二者之间有可能存在软件理解上的差异,转换后的VHDL代码实现可能与MDL模型描述的情况不完全相符,这就是需要针对生成的RTL级VHDL代码进行功能仿真。

在此,笔者利用Modelsim对生成的VHDL代码进行功能仿真。设置输入输出信号均为模拟形式,出现如图4所示的仿真波形,可以看到这与Simulink里的仿真结果基本一致,即可在QuartusⅡ环境下进行硬件设计。

4.5 在FPGA器件中实现FIR滤波器

在QuartusⅡ环境中打开DSPBuilder建立的QuartusⅡ项目文件firl.qpf。在QuartusⅡ中进行再一次仿真,由此可以看到符合要求时序波形,然后指定器件引脚并进行编译,最后下载到FPGA器件中,就可以对硬件进行测试,加上CLCOK信号和使能信号,用信号发生器产生所要求的两个不同频率的正弦信号,就可以在示波器上看到滤波以后的结果,需要设计不同的滤波器电路时,仅修改FIR滤波模型文件就可以实现,这样不仅避免了繁琐的VHDL语言编程,而且便于进行调整。

5 结束语

在利用FPGA进行数字滤波器的开发时,采用DSPBuilder作为设计工具能加快进度。当然,在实际应用中,受精度、速度和器件选择方面的影响,可以对其转化的VHDL进行进一步的优化。

-

FPGA

+关注

关注

1629文章

21748浏览量

603836 -

滤波器

+关注

关注

161文章

7833浏览量

178240 -

数字信号

+关注

关注

2文章

971浏览量

47574

发布评论请先 登录

相关推荐

使用FPGA构建的数字滤波器设计方案

基于MATLAB与QUARTUS II的FIR滤波器该怎么设计?

高效FIR滤波器的设计与仿真-基于FPGA

高阶FIR正交镜像滤波器的设计

基于优化神经网络的FIR滤波器的设计方案

FIR数字滤波器设计方案

FIR滤波器的FPGA设计与实现

FIR滤波器设计方案

FIR滤波器设计方案

评论