引言

对通信数据进行加密的方法可分为两大类:软加密和硬加密。其中硬加密具有加密强度大、可靠性高等特点。本文根据流密码发生器原理,用CPLD设计出了Gollmann流密码发生器。

原理

密码安全的伪随机序列发生器用于流密码时十分理想,这些发生器的输出与真正随机的位发生器难以区分,只需将发生器的输出与明文流异或就可以得到良好的流密码。

Gollmann流密码发生器由一串LFSR(线性反馈移位寄存器)构成,每个LFSR的时钟由前一个LFSR控制,如果t-1时刻LFSR-1的输出为1,则LFSR-2在t时刻阶跃;如果t-1时刻LFSR-2的输出为1,则LFSR-3在t时刻阶跃,以此类推,最后一个LFSR的输出为发生器的输出。如果所有LFSR的长度都为l,则n个LFSR构成的系统的线性复杂度为:

l*(2l-1) n-1

流密码发生器的设计

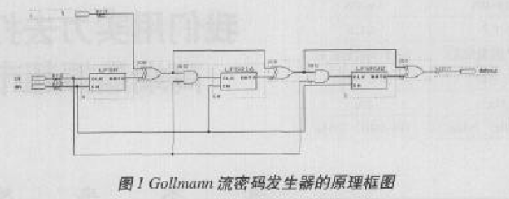

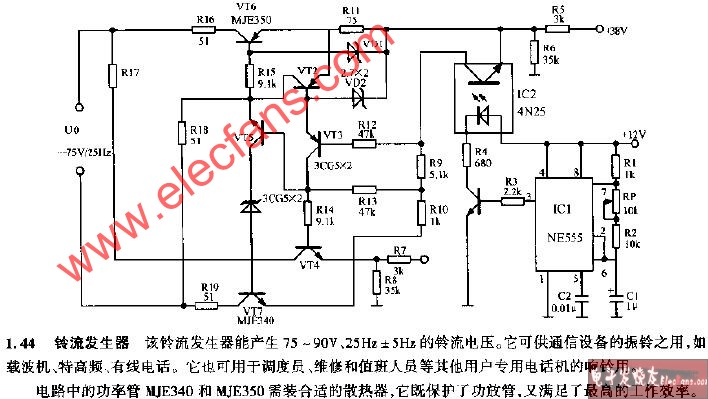

根据Gollmann流密码发生器的原理设计的发生器的原理框图可用MAX+plusII的电路图方式表示,如图1所示。

在Gollmann流密码发生器中,LFSR是其重要的组成部分。本文只采用了3级LFSR,其中LFSR长度为4比特,其生成多项式为x4+x1+1;LFSR16长度为16比特,其生成多项式为x16+x5+x3+x2+1;LFSR32长度为32比特,其生成多项式为x32+x7+x6+x2+1。

其中LFSR的VHDL程序描述如下:

entity lfsr is

port(clk,en:in std_logic;

data:out std_logic);

end entity;

architecture bev of lfsr is

signal sh:std_logic_vector(0 to 3);

begin

process(clk,en)

begin

if en=‘0’ then

sh《=“1111”;

elsif clk=‘1’ and clk‘event then

sh(3)《= sh(3) xor sh(0) ;

for i in 1 to 3 loop

sh(i-1)《=sh(i);

end loop;

data《=sh(0);

end if;

end process;

end bev;

Gollmann流密码发生器的工作流程为:在初始时刻,使能信号en为1时将所有LFSR中的寄存器赋值为1。随着时钟clk下降沿的到来,将第一个LFSR的输出信号与输入信号1异或,再将其结果和clk进行与运算作为第二个LFSR的输入,同时该异或结果还将和第二个LFSR的输出进行异或。异或后的结果既同clk做与运算后作为第三个LFSR的输入,同时又与第三个LFSR的输出做异或运算。第三次异或后的结果即为Gollmann流密码发生器的输出结果。

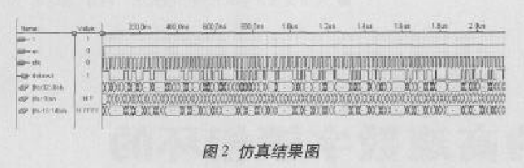

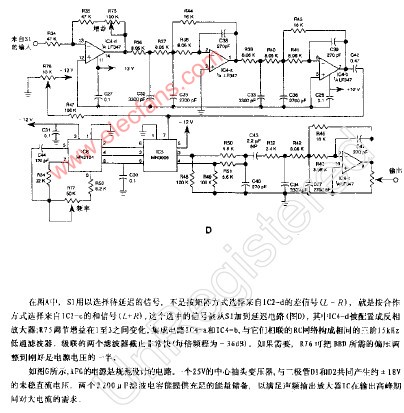

本文选用Altera公司的MAX+plus II 10 Baseline对VHDL源程序编译,这个工具支持VHDL的编译和仿真。对Gollmann流密码生成器的程序进行仿真,结果如图2所示。

图2中en为使能信号,clk为50MHz的时钟信号,dataout为输出信号。Lfsr32sh,lfsr16sh,lfsrsh为各个LFSR寄存器值的变化过程。

在所有LFSR初始值都为1时(初始值不同,输出的结果就有所不同),Gollmann流密码生成器所产生的输出类似于随机序列,如图2中dataout所示,可以满足一般的加密要求。

结语

本文设计的Gollmann流密码生成器结构简单,加密能力较强,同时还可以继续扩充多个LFSR,以增强其加密功能。

责任编辑:gt

-

cpld

+关注

关注

32文章

1248浏览量

169359 -

寄存器

+关注

关注

31文章

5343浏览量

120345 -

通信

+关注

关注

18文章

6032浏览量

135990

发布评论请先 登录

相关推荐

[求助]基于FPGA的伪随机码发生器的设计与实现

学习笔记 | 基于FPGA的伪随机数发生器(附代码)

本原LFSR序列的迹表示及其应用

LFSR在序列密码算法ABC中的应用

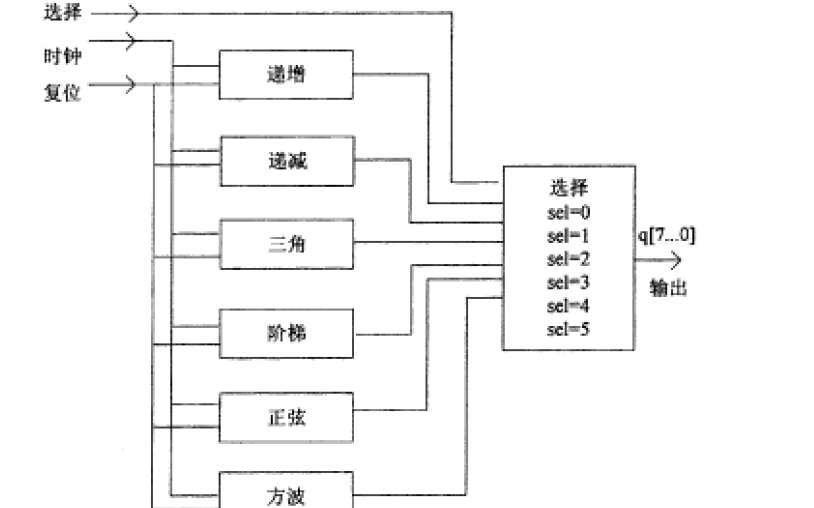

基于FPGA的DDS波形信号发生器的设计

基于FPGA的PCIe总线接口的DMA控制器的实现并进行仿真验证

直流高压发生器的使用

如何使用智能函数发生器进行VHDL的设计与仿真

采用3级LFSR实现Gollmann流密码发生器的设计并进行仿真验证

采用3级LFSR实现Gollmann流密码发生器的设计并进行仿真验证

评论