本文中的测控系统是某型号无人机电子系统中的一个重要部分。为了对测控系统的改进优化设计进行验证,需要对软件进行长期运行考核,对该分系统进行单机验收与联试,验证其与其它分系统接口的匹配性;同时还要为测控系统提供真实的物理连接接口、动态输入参数,进而提供与无人机同步的仿真运行环境。遥测解调及遥控注入测试卡是根据验证测控系统工作的需要而设计开发的,它能为其提供遥测解调、遥控数据注入、直接指令注入、触点信号和40kHz时钟等接口信号。能对原测控系统进行测试的遥测解调及遥控注入测试卡是ISA插卡,使用分离器件来实现。随着计算机硬件的发展,PCI总线已经成为当今高性能微型计算机事实上的总线标准,PCI总线的性能远远高于ISA总线,因此基于PCI的遥测解调及遥控注入测试卡更符合实际应用的需要。FPGA技术的应用日益成熟和广泛,用FPGA芯片替代分离器件将大大提高测试卡的可靠性。本文论述了基于Altera公司的Acex1K系列芯片(如ACEK1K30QC208等),采用PCI局部总线标准,设计基于PCI的遥测解调及遥控注入测试卡的一些关键技术。

1 PCI局部总线

以Intel公司为首的PCI SIG小组推出的PCI总线标准是一种高端现代局部总线,它具有符合工业标准、性能高、成本低、独立于处理器、允许灵活配置、使用寿命长、可操作性强和软件兼容性好等优点,因此在嵌入式计算机和工业控制计算机领域具有广阔的应用前景。PCI总线与传统ISA总线、现代的EISA总线的性能比较如表1所示。

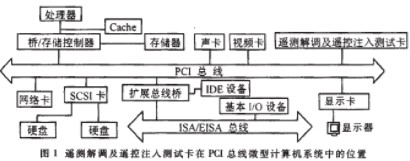

PCI局部总线是微型计算机中处理器/存储器与外围控制部件、扩展卡之间的互连接口。PCI总线规范是互连机构的协议及电气和机械配置的规范,其用途是在高度集成的外设控制器器件、扩展板和处理器之间提供一种内部联结机制。本文中的基于PCI的遥测解调及遥控注入测试卡是由PCI总线完成测试卡和处理器/存储器的连接,其在PCI总线微型计算机系统中的位置如图1所示。

2 FPGA技术

在现代电子系统领域,EDA技术已经逐渐成为电子系统的主要设计手段。FPGA(现场可编程门阵列)是EDA技术中的一种重要应用。FPGA器件在结构上由逻辑功能块排列为阵列,并由可编程的内部连线连接这些功能块,来实现一定的逻辑功能。设计遥测解调及遥控注入测试卡的数字和逻辑电路部分均由FPGA器件来完成。

考虑到遥测解调及遥控注入测试卡逻辑功能的需要,本设计采用Altera公司的FPGA芯片ACEK1K50QC208。该芯片具有5万门可编程逻辑单元,属于Sram型的FPGA芯片,逻辑信息保存在专门的静态存储器中(本设计中使用EPC1PC8芯片作为静态储存器),上电时动态加载。这种类型的器件在验证期间可以使用下载工具将逻辑加载到芯片中,验证完毕后需要将逻辑信息烧写在静态存储器中,以后系统上电时,FPGA从静态存储器中自动加载逻辑。

使用FPGA进行电路设计的步骤为:首先采用目前流行的硬件描述语言Verilog HDL设计输入,即将设计的逻辑、时序关系输入计算机;之后,使用Maxplus II软件进行前仿真、综合、布局布线和后仿真,即验证输入的硬件描述语言的逻辑关系是否正确,若正确则用抽象语言将逻辑描述分解为具体的逻辑单元,在FPGA器件中实现,并验证布局布线后仿真是否正确;最后,进行硬件验证,将计算机上布局布线之后生成的文件加载到FPGA中,以验证它的实际工作情况同设计是否一致。

3 遥测解调及遥控注入测试卡的设计

3.1 测试卡的测试接口信号要求

测试卡要根据测试的需要提供测试接口信号。这些测试接口信号共包括五类:

(1)遥测解调信号:测试卡集成了两路遥测解调器的功能。其中每一路遥测解调器都能够输出帧同步信号、路同步信号和数据时钟信号。被测系统根据解调器卡输出的上述三个信号,按照一定的时序关系输出串行的遥测数据。

(2)遥控数据注入:测试卡集成了两路遥控数据注入单元。其中每一路遥控数据注入单元都能够提供数据有效信号、时钟信号和数据信号。

(3)遥控指令:测试卡提供1套24路直接遥控指令输出。每路指令处于工作状态时,集电极开路门接通(低电平);处于非工作状态时,集电极开路门不接通(高电平)。

(4)触点信号:测试卡提供1套11路(共22根引脚)触点输出信号。每路触点信号为开关闭合有效,断开无效。

(5)时钟输出:测试卡提供1路40kHz的时钟输出信号。

3.2 测试卡硬件系统的实现

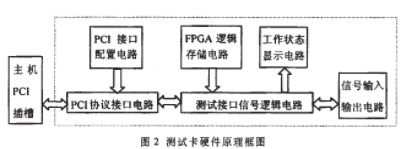

在该测试卡的电路系统中,由FPGA芯片提供测试接口信号并实现软件接口逻辑设计;由PCI接口芯片实现测试卡同计算机上PCI总线的连接;由分离器件实现测试接口信号的输入输出。测试卡的硬件原理框图如图2所示。

在图2中,PCI协议接口电路主要是使用PCI总线接口芯片9052来提供高性能的PCI总线接口,其使用需要对它的PCI配置寄存器和本地配置寄存器进行设置。在PCI接口配置电路中,采用93CS46N串行EEROM芯片对9052芯片PCI配置寄存器和本地配置寄存器进行设置。

测试接口信号逻辑电路围绕FPGA芯片ACEK1K30QC208进行设计。该芯片能够完成测试卡需要的五类测试信号的逻辑设计,还能实现可供使用人员配置的测试卡软件接口,以及和PCI总线接口进行信号传输的逻辑。ACEK1K30QC208芯片是Sram型的FPGA芯片,还需要专门的逻辑存储电路来保存上述逻辑信息。逻辑存储电路使用静态存储器芯片EPC1PC8芯片,系统上电时,FPGA从存储器中自动加载逻辑。

测试信号输入输出电路完成测试卡与被测设备的信息交换。对于测试卡提供的五类测试信息,遥控指令和触电信号需要模拟器件和电子开关进行转换,而其它信号则可以通过连接器直接输入输出。

工作状态显示电路提供测试卡的工作状态,如测试卡是否加电成功、是否逻辑下载成功、是否在进行遥控指令注入、是否在进行遥测数据接收等。工作状态显示电路的逻辑也来自于测试接口信号逻辑电路。

3.3 PCI局部总线和测试卡本地总线的连接

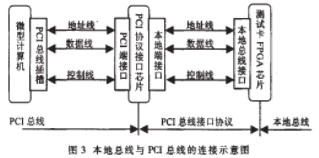

本设计采用了PLX Technology公司的PCI总线协议接口芯片9052来实现PCI 总线和本地总线之间的连接。PCI总线协议接口芯片9052为各类适配卡提供高性能的PCI总线接口,可以将PCI总线同各种传输速率低于132Mb/s的本地总线进行连接。采用PCI总线协议接口芯片9052来实现PCI总线和本地总线之间的连接,如图3所示。

由于9052是专门的PCI协议芯片,所以它的PCI端可以直接通过插卡上的引线和PCI插槽连接。二者连接时不用做任何变换,将二者的复用数据线和地址线直接连通,将9052的PCI端的控制线与PCI插槽上的作为从设备的控制线直接连通即可。

9052芯片本地端接口和FPGA芯片的连接也就是PCI总线接口和测试卡本地总线的连接,是本接口卡设计的一个关键。在FPGA芯片的逻辑设计中,根据测试卡对主机系统资源的需求,提供了一个测试卡本地总线接口。本地总线接口包括4K字节的存储器和16字节的寄存器,所以将要使用9052芯片的两个地址空间分别设置为4K字节和16字节,将存储器和寄存器空间分开。在地址线和数据线的设计上,采用地址线和数据线非复用模式,本地的地址线和数据线分别与9052本地端的地址线和数据线连接。在控制线的设计上,根据二者的读写时序,将9052芯片设置为直接读写的方式,用9052芯片的读信号和写信号直接驱动本地总线的读写信号。另外还要使用9052芯片提供的一个片选信号,来选择不同的16个字节的寄存器地址空间。9052本地端和BU-61580要采用同一个时钟信号,以保证二者读写时序的同步。

3.4 测试卡软件接口的设计

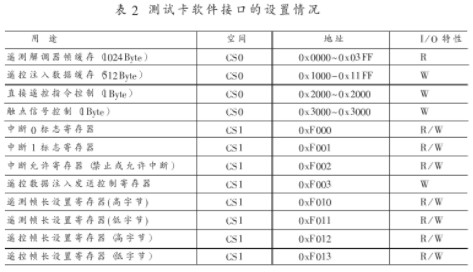

测试用户需要对测试卡进行软件设置,来实现遥控注入数据、遥测和遥控帧长、遥控数据发送等。这些软件接口是通过FPGA芯片进行逻辑设计来提供的。测试卡加电后,这些软件接口就存在于测试卡上,通过软件编程可以控制软件接口,来实现测试卡的测试工作。测试卡实现的软件接口如表2所示。

4 测试卡与其配套软件的数据流和控制流

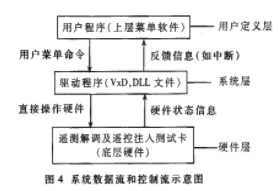

遥测解调及遥控注入测试卡要和其配套的软件接口卡驱动程序(VxD)及用户菜单应用软件共同使用。遥测解调及遥控注入测试卡作为硬件BIU同被测测控系统连接,负责接收与发送各类测试数据,并且可以由主机来配置测试卡上的寄存器。驱动程序则作为遥测解调及遥控注入测试卡和用户菜单软件的接口程序,负责接收菜单软件的命令,并依据此命令来操作硬件,或者向菜单软件报告总线适配器的工作情况(如通知中断已经产生以及告知中断原因),包括安装信息文件(INF)、虚拟设备驱动程序(VxD)、接口函数文件(DLL)三个组成部分。菜单软件作为用户界面程序接收用户的输入,并以可视的方式将结果数据反馈。遥测解调及遥控注入测试卡与处理器之间所构成系统的数据流和控制流如图4所示。

-

FPGA

+关注

关注

1629文章

21753浏览量

604143 -

芯片

+关注

关注

456文章

50917浏览量

424533 -

总线

+关注

关注

10文章

2891浏览量

88160

发布评论请先 登录

相关推荐

采用CH365芯片实现PCI总线接口卡设计

采用PCI IP核实现码流接收卡设计

采用PCI总线集成电路实现测试仪接口设计

基于PCI总线的CAN卡的设计与实现

采用中档FPGA设计面向PCI Express系统的解决方案

PCI总线ARINC429通信卡实现方法

一种PCI总线ARINC429通信卡实现方法

采用FPGA技术和PCI总线标准实现遥测解调及遥控注入测试卡的设计

采用FPGA技术和PCI总线标准实现遥测解调及遥控注入测试卡的设计

评论