无论是数据通讯或者SOC(包括FPGA或者ASIC设计)设计,跨时钟域(clock domain crossing)处理都是一件让人很头疼的事情,无论是在设计的前端或者步入设计的后端,都没有很好的工具去做保证,只能靠设计人员的经验进行最大的保证,然而这个问题如果处理不好,你的整个设计可能就完全报废,而最怕的是你的设计时好时坏,有时稳定,有时出错,这个时候你甚至很难进行定位(尤其是上了FPGA开发板或者芯片已经tapout了)。

一般而言,处理跨时钟域的方法有这么几种(大家在网上也都能找到资料,这些资料大都来自几篇经典的论文,中文方面的资料大都是翻译过着理解这几篇论文而来):少量的数据用边沿检测电路,或者脉冲检测电路,或者电平检测电路,或者两级触发器;比较多的数据时用异步FIFO。

本文侧重讲解本人对异步FIFO的深入理解,讲解两种经典的异步FIFO的设计方案,这两种方案来自一篇文章《simulation and synthesis techniques for asynchronous FIFO design》,大家可自行下载,设计思路这篇文章里面介绍的很详细,解释的也很出色,我更多的是谈谈我的部分理解。

1、异步FIFO设计的难点在哪里

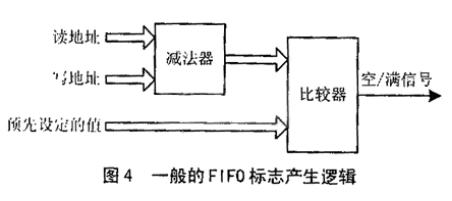

1)写地址和读地址处于不同的时钟域,如何比对写地址和读地址才能正确的产生空满信号;

2)当读写地址相同时,究竟是读空了还是写满了(因为存在你追我赶的情况,类似于一个圆环)。

2、处理思路

1)对于难点1大家自然想到采用同步处理的方式,具体为将写地址或者读地址同步(例如利用两级触发器)到对方的时钟域中,在相同的时钟域中进行地址的比对,但是由于写地址和读地址很多时候并不止1bit,同时进行同步处理会增大错误的概率(如地址按0111->1000跳变,此时4bit都在变化,DFF进行同步时就很容易出错),因而可以先将地址(二进制的)转换为格雷码(相邻数据之间只有一个bit在变化),然后再进行同步,最后进行对比,这样会大大减少错误的概率。

2)对于难点2可以在地址前面添加1bit用于标志位进行区分,例如复位时,读写地址的标志位都是0,如果写完1轮而开始新的一轮时就将写地址的标志位换为1(读也同样道理变换),这样可以通过判断标志位加上对比地址判断是空还是满,具体为当读写地址的标志位相同读写地址相同时为读空,具体为当读写地址的标志位不同读写地址相同时为写满;另外也可以利用格雷码的最高两位00->01->10->11进行相位的区分,具体参考我给出的文章或者网络资料,其实本质上和上面的是一个道理。

3、经典FIFO设计方案的解读

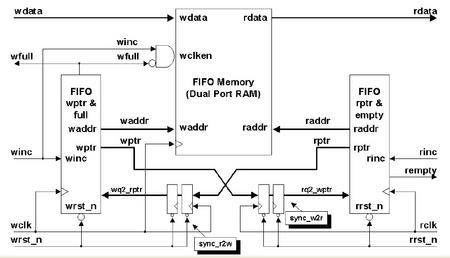

1)同步读写地址(经格雷码转换后)到对方的时钟域

相比于直接同步二信号进制地址(先用握手,然后同步二进制地址)好处是格雷码相邻数据之间只有一个bit在变化,而二进制由于写地址和读地址很多时候并不止1bit,同时进行同步处理会增大错误的概率(如地址按0111->1000跳变,此时4bit都在变化,DFF进行同步时就很容易出错);利用格雷码进行同步,即使发生同步的时出错也不会造成overrun和underrun的情况(因为同步后的数据必定小于等于同步前的数据,即只可能1被同步为0,而不可能0被同步为1),例如当前的读地址到了6,写地址到了8,地址8经过同步后出错而变成了6,这时会出现地址相同而判断为读空,不过没关系,读空则不读,至少不会出现underrun的情况,随着时间的推移地址8总会被采样到;然而格雷码也有缺点,只能连续变化递增或者递减(如果间隔变化就不符合格雷码的特点了),所以设计的深度必须是2的n次幂,如果不是的话,需要重新产生编码格雷码,否则也会出现间隔变化不符合相邻之间只有1bit变化的特点。

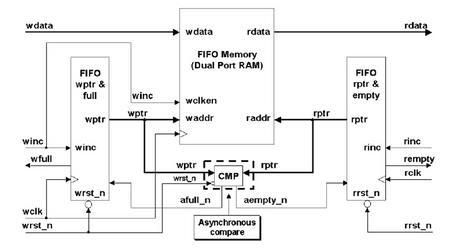

2)将读写地址(经格雷码转换后)同步到一个组合逻辑电路中(异步比较)直接比较空满,然后将空满信号同步到各自对应的模块中

虽然这种电路会给fifo带来不好的状态,例如已经满了wfull==1,但是这个时候读走一个数据,由于同步的延时性,导致这一段时间内wfull==1一直不变(如果没有同步带来的延时应该变为0的),rempty也会遇到同样的问题,但是这种电路不会出现underrun和overrun的情况。

3)2)相比1)可能会节省面积,因为1)同步wptr[n-1:0]和rptr[n-1:0],2)只需要同步afull_n,aempty_n;1)的速率可能较2)会快些,2)中存在异步且组合逻辑比较,不利于时序的优化。

-

fifo

+关注

关注

3文章

407浏览量

45898 -

数据通讯

+关注

关注

0文章

50浏览量

13441

发布评论请先 登录

基于FPGA器件实现异步FIFO读写系统的设计

异步FIFO结构及FPGA设计

高速异步FIFO的设计与实现

Camera Link接口的异步FIFO设计与实现

异步FIFO结构及FPGA设计

异步FIFO的设计分析及详细代码

基于FPGA的异步FIFO设计方法详解

基于异步FIFO结构原理

异步FIFO设计方案详解 异步FIFO设计的难点在哪里

异步FIFO设计方案详解 异步FIFO设计的难点在哪里

评论