非门(反相器)介绍

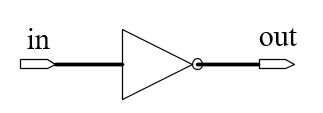

非门实现的是逻辑功能为 out = -in, 即将输入信号做一个反向,故也称为反相器。其门级示意图如下:

Verilog描述如下(“//”后面的语句为注释语句):

wire in; //wire 为线信号关键字

wire out;

assign out = ~in; //assign 为赋值语句,~表示反向;

相应的逻辑真值表如下:

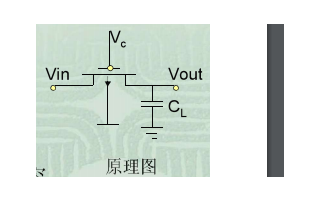

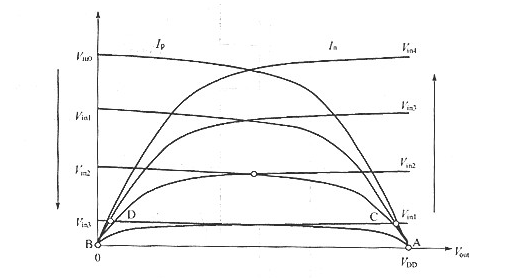

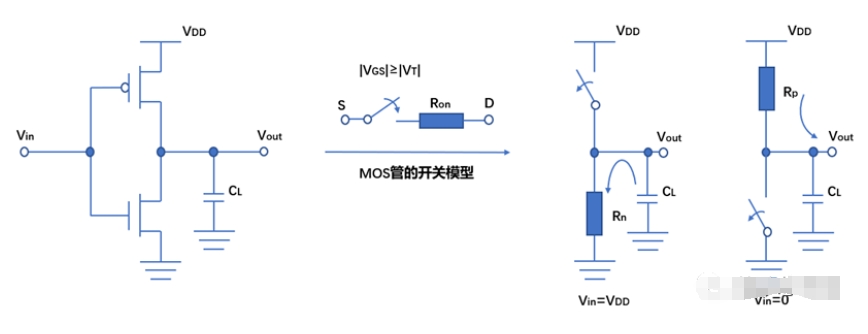

相应的CMOS结构如下:由一个PMOS和NMOS组成,PMOS做上拉,与VDD相连;NMOS做下拉,与GND相连。

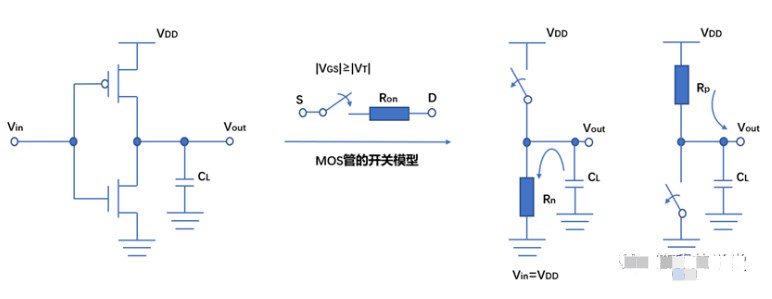

简单分析一下我们要实现的功能,无非就是当 in 为 0 (低电平)时,out输出为1(高电平),即out跟电源VDD相连;当 in 为 1(高电平)时,out输出为0(低电平),即out要跟GND(地)相连。故上面的非门CMOS电路的等效电路如下:当in 为0时开关k1闭合,k2打开,即out与VDD相连,输出为1;当in 为1时开关k1打开,k2闭合,即out与GND相连,输出为0。

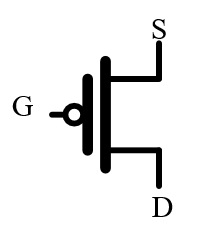

故PMOS相当于一个开关,如下当G端为低电平时,D端与S端才连通;

故NMOS相当于一个开关,如下当G端为高电平时,D端与S端才连通;

拓展:现在常见的数字集成电路其底层的基本逻辑电路都是由CMOS结构构成。上拉逻辑部分由PMOS组成,下拉逻辑部分由NMOS组成。反相器就是一个最基本的CMOS逻辑电路,上拉部分只有一个PMOS,下拉部分只有一个NMOS。后面还会讲到其它逻辑门电路,到时候大家对CMOS逻辑的了解就更深入了。

-

CMOS

+关注

关注

58文章

5680浏览量

235144 -

电路

+关注

关注

172文章

5849浏览量

171909 -

反相器

+关注

关注

6文章

310浏览量

43244

原文标题:非门(反相器)介绍

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【数字电路】关于逻辑非门电路设计的教程

MOS反相器和CMOS反相器的详细资料说明

最基本的CMOS逻辑电路:非门(反相器)

最基本的CMOS逻辑电路:非门(反相器)

评论