声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

intel

+关注

关注

19文章

3482浏览量

186092 -

代码

+关注

关注

30文章

4796浏览量

68704 -

性能

+关注

关注

0文章

271浏览量

19009

发布评论请先 登录

相关推荐

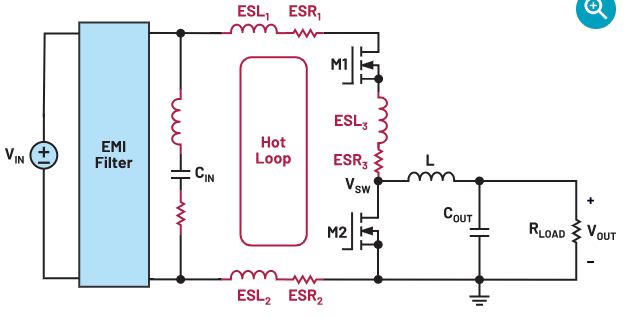

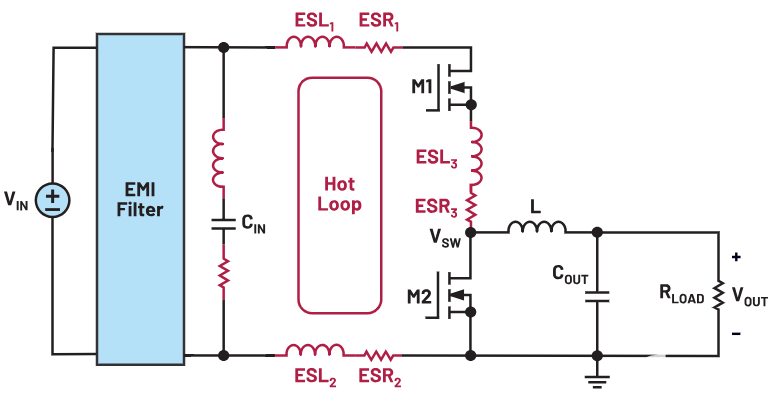

如何通过最小化热回路PCB ESR和ESL来优化开关电源布局

如何通过最小化PCB的等效串联电阻(ESR)和等效串联电感(ESL)来优化热回路布局设计。本文研究并比较了影响因素,包括解耦电容位置、功率FET尺寸和位置以及过孔布置。通过实验验证了分析结果,并总结了最小化PCB ESR和ESL

手动最小化前面板运行内存会骤降,而程序控制最小化不行

有个程序,刚打开运行时占内存140M左右,手动把前面板最小化就会降至20M左右,把前面板还原显示后内存会逐渐升到60M左右,而如果我在程序里添加一个指令,就是按

发表于 08-11 23:55

PCB布局提示和技巧:最小化去耦电感

的作者的话来说,Hubing等。声称在某些条件下电容器的位置“不重要”,尽管他们可能已经将结论扩展到“研究的有效性范围之外”。无论如何,这是电容器之间相互作用重要性的另一个例子。并且平

发表于 07-27 11:59

如何通过最小化热回路来优化开关电源布局?

)。本文讨论如何通过最小化PCB的等效串联电阻(ESR)和等效串联电感(ESL)来优化热回路布局设计。本文研究并比较了影响因素,包括解耦电容位置、功率FET尺寸和位置以及过孔布置。通过实验验证了分析结果,并总结了最小化PCB E

如何通过最小化热回路PCB ESR和ESL来优化开关电源布局

设计。本文研究并比较了影响因素,包括去耦电容位置、功率FET尺寸和位置以及过孔布局。通过实验验证了分析的有效性,总结了最小化PCB ESR和ESL的有效方法。

如何通过最小化热回路PCB ESR和ESL来优化开关电源布局

设计。本文研究并比较了影响因素,包括去耦电容位置、功率FET尺寸和位置以及过孔布局。通过实验验证了分析的有效性,总结了最小化PCB ESR和ESL的有效方法。

从“正确”到“正确和有效”:一个最小化的案例研究

从“正确”到“正确和有效”:一个最小化的案例研究

评论