寄存器以及建立保持时间,传输延迟的介绍

寄存的图标一般如下图(忽略复位端)。

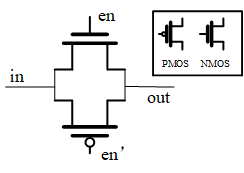

这里先介绍一下传输门。CMOS传输门如下图所示。由一个PMOS和一个NMOS组成。en接NMOS的G端,en的反向en’ 接PMOS的G端。我们知道,NMOS的G端为高电平时,NMOS管两端导通;PMOS的G端为低电平时,PMOS管两端导通。故当en为高时,PMOS和NMOS管都导通,输入in可以传输到out端;否则,传输门关闭。

问题:为什么要用两个管子,一个PMOS和一个NMOS来实现传输门,而不只用一个NMOS管,或者PMOS来实现传输门?

答案:前面讲CMOS实现与或门时已经提过。

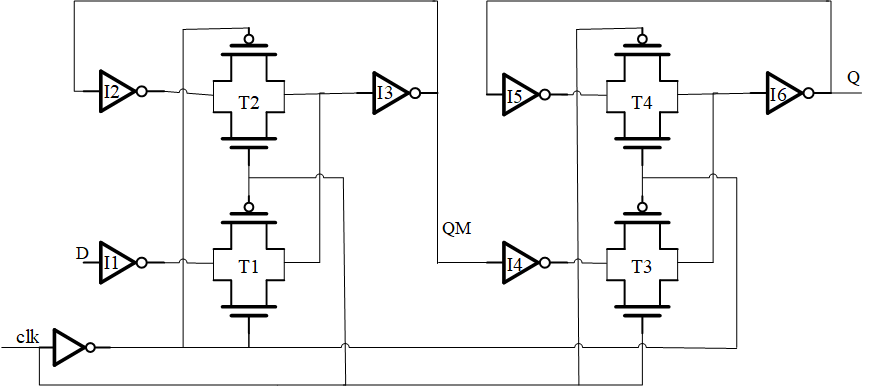

下面给出主从上升沿触发的寄存器MOS级电路图。可以看到,前后两级电路一致,就是传输门的clk接法相反,故叫主从式。

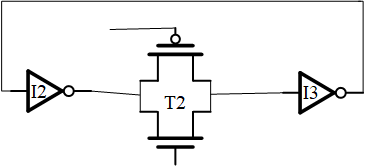

当时钟信号为低电平时,传输门T1导通,数据经过反相器I1,传输门T1,反相器I3,传到QM端。此时T2,T3传输门为关闭状态。T4为导通状态,故此时后面半部分的电路结构如下。相当于两个反相器首尾相连,这就是一个琐存结构,维持数据Q不变。

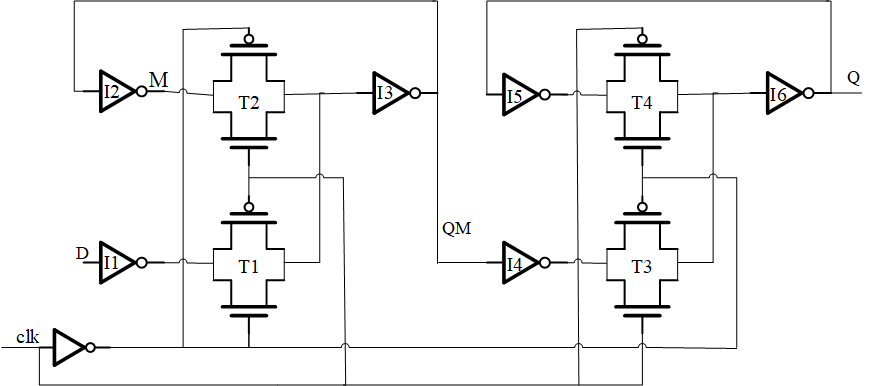

当时钟clk由低电平变成高电平之后,T3导通,原本在clk为低电平时传到QM的数据被传输到后面的Q端。此时T4是关闭的。但是前半部分电路当clk变成高电平之后传输门T1关闭,新的数据D进不来了。而此时T2导通,结构如下,也是一个琐存结构,此时维持低电平时送进来的数据不变。

由上面的分析可得,当clk为低电平时,T1导通,新的数据被送到第一级,但是T3不导通,传不到Q端,T4导通构成一个琐存结构,维持Q的输出不变;当clk由低变成高电平之后,T1关闭,新的数据不会再传进来;同时T2导通,构成一个锁存器维持数据QM不变;同时T3导通,QM传输到Q端;T4不导通,原先琐存的数据不会对Q造成影响。因此整体实现的就是当clk上升沿来到时,数据D才会被更新到Q端。

经过上面的分析我们再来看建立时间与保持时间以及传输延时。

建立时间(tsetup):既数据D至少需要提到于clk上升沿多长时间到来,数据的采集才不会出错。

从电路分析可知,在时钟上升沿到来之前数据必须要被送到第一级电路的锁存器里面,即M端。见下图。

为什么呢?

因为如果上升沿到来时,数据没有被送到M端,当时钟上升沿一来,此时T2右端与M端的信号就会不一致;M端为旧数据,T2右端为新数据,那么旧数据可能会将新数据冲掉。

故在clk上升沿到来时,数据要被传到M端,需经过I1,T1,I3, I2 。故在时钟上升沿到来前 tsetup = tI1 + tT1 + tI3 + tI2时间数据D就必须送到寄存器输入端,这个时间就是三个反相器加一个传输门的延时。

保持时间(thold):就是时钟上升沿之后,数据D还需要维持多长时间不变,才不会对输出Q造成影响。

从电路可以看到,当时钟上升沿一来,T1就关闭了,就算关闭具有延迟,上升沿一到,数据立即就变化了,还是要经过一个反相器I1才能传到T1,故不担心数据会被送进去,因此保持时间可以为零。当然这是对于这个主从式结构的寄存器而言,其他的寄存器的保持时间不一定为零。

传输延时(tcq):既时钟上升沿来了之后,数据还需要多久才能传到Q端。

从电路分析,当时钟上升沿来了之后,数据还需要经过T3,I6才能传到Q端,故这个寄存器的传输延时tcq =tI6+tT3 。

这里只是以主从式上升沿触发寄存器为例介绍深入介绍了一下为什么寄存器会有建立时间,保持时间要求,以及传输延时的概念。对于后面如果利用EDA工具做静态时序分析时,这些参数都是由器件或者工艺库直接给出的。

接下来我们会继续探讨时钟同步电路的时序问题与时序优化。

-

CMOS

+关注

关注

58文章

5725浏览量

235711 -

寄存器

+关注

关注

31文章

5357浏览量

120689 -

反相器

+关注

关注

6文章

311浏览量

43394

原文标题:寄存器以及建立保持时间,传输延迟的介绍

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

芯片设计进阶之路—从CMOS到建立时间和保持时间

FPGA实战演练逻辑篇51:建立时间和保持时间

保持时间与建立时间

数字 IC 笔试面试必考点(9)建立时间以及保持时间 精选资料分享

为什么触发器要满足建立时间和保持时间

建立时间和保持时间(setup time 和 hold time)

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量

为什么寄存器会有建立时间,保持时间要求,以及传输延时的概念

为什么寄存器会有建立时间,保持时间要求,以及传输延时的概念

评论