本文主要是关于tms320c6748的相关介绍,并着重tms320c6748的结构进行了详尽的阐述。

tms320c6748

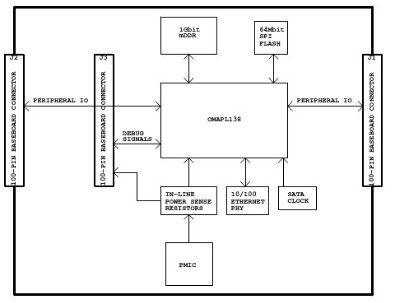

TMS320C6748是德州仪器 (TI) 推出浮点功能的全新高性能处理器 ,这款芯片也是业界功耗最低的浮点数字信号处理器 (DSP),可充分满足高能效、连通性设计对高集成度外设、更低热量耗散以及更长电池使用寿命的需求。不仅具备通用并行端口 (uPP),同时也是 TI 首批集成串行高级技术附件 (SATA)的器件。 广州创龙推出的TL6748-EVM评估套件为开发者使用TI TMS320C6748处理器提供了完善的软件开发环境,系统支持:裸机、SYS/BIOS、DSP/BIOS。提供参考底板原理图,DSP C6748入门教程、丰富的Demo程序、完整的软件开发包,以及详细的C6748系统开发文档,方便用户快速评估TMS320C6748处理器、设计系统驱动及其定制应用软件,也大大降低产品开发周期,让客户产品快速上市。主要面向电力、通信、工控、音视频处理等数据采集处理行业。 TL6748-EVM评估套件是一个功能丰富的开发板,为嵌入式设计人员提供快捷简单的实践方式来评估TMS320C674x系列处理器,是一个完整的实验评估平台。

德州仪器 (TI) 推出浮点功能的全新高性能处理器 —— TMS320C6748,这款芯片也是业界功耗最低的浮点数字信号处理器 (DSP),可充分满足高能效、连通性设计对高集成度外设、更低热量耗散以及更长电池使用寿命的需求。不仅具备通用并行端口 (uPP),同时也是 TI 首批集成串行高级技术附件 (SATA)的器件。

广州创龙推出的TL6748-EVM评估套件为开发者使用TI TMS320C6748处理器提供了完善的软件开发环境,系统支持:裸机、SYS/BIOS、DSP/BIOS。提供参考底板原理图,DSP C6748入门教程、丰富的Demo程序、完整的软件开发包,以及详细的C6748系统开发文档,方便用户快速评估TMS320C6748处理器、设计系统驱动及其定制应用软件,也大大降低产品开发周期,让客户产品快速上市。主要面向电力、通信、工控、音视频处理等数据采集处理行业。

TL6748-EVM评估套件是一个功能丰富的开发板,为嵌入式设计人员提供快捷简单的实践方式来评估TMS320C674x系列处理器,是一个完整的实验评估平台。

规格参数/TMS320C6748

处理器

TMS320C6748图册TMS320C6748,C6000系列浮点DSP处理器(Pin to Pin兼容OMAPL138,AM1808处理器)

主频:456MHz

存储器

128M/256M/512MByte 工业级NAND Flash

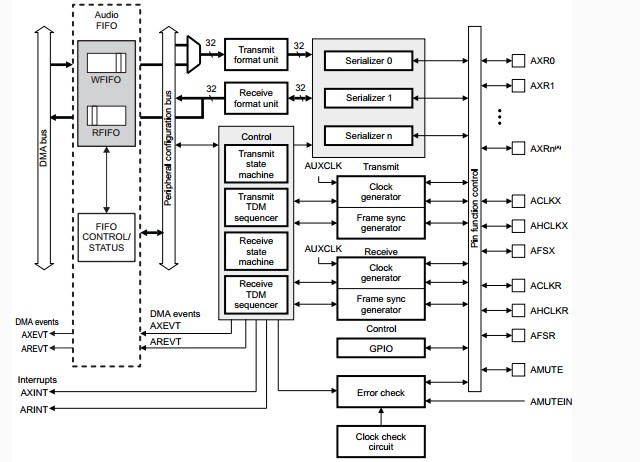

1个3.5mm Line in音频输入接口

1个3.5mm Mic in音频输入接口

1个3.5mm Line out音频输出接口

外设接口

串口、USB接口:

UART2,3线串口,RS232电平

1个RS485接口(RS485和UART1复用)

1 x USB2.0 OTG(Mini USB-B母座接口)

4 x USB1.1 HOST(2 x 双层USB Type A座)

其他外设接口:

1个标准SD卡座(SD/MMC信号,支持1.8V及3.3V逻辑电压)

1个SATA接口(7pin SATA硬盘接口)

1个RTC座(RC1220 RTC座)

1 个JTAG接口(14Pin TI Rev B JTAG接口)

扩展接口:(2x IDC3简易牛角座(2x 25pin规格))

1路SPI总线

1路IIC总线

1路UART信号

1路VPIF总线

1路uPP总线

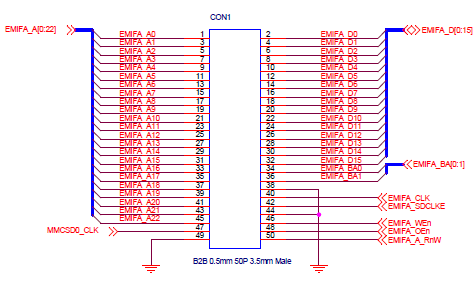

1路EMIF总线

可设置多个GPIO

输入接口

1个非屏蔽中断按键

1个可编程按键

1个复位按键

2个电源指示灯

1个系统指示灯

4个可编程指示灯

显示单元

一个VGA接口

一个24bit真彩色LCD接口(50pinFPC排座;含4电阻式线触摸屏接口,分辨率可支持1366x768)

电气参数

工作电压:3.8V~5.5V(典型值:5V)

工作温度:-45~85℃

环境湿度:20% ~ 90% ,非冷凝

开发板:180mm*130mm

核心板:55mm*33mm

电气指标:+5V@150mA

核心板功耗

电压:5V

电流:98mA

功耗:0.49W

浅谈tms320c6748最小系统设计和cache配置

处理器的cache是一块存储靠近处理器数据的高速存储区。这帮助常用的指令和数据的快速访问从而提高计算性能。Cache可以视为平坦式记忆体,即认为cache是CPU靠近的可以很快访问的存储器

存储组织结构

图1的左边的模型是一个平坦式记忆体系统架构,假设CPU和片内存储空间都运行在300 MHz,存储访问的延时只有在CPU访问外存的时候才存在,而memory stall不会在访问片内存储区时发生。如果CPU的频率是600 MHz,那么在访问这部分片内存储区的时候还是存在等待周期的。不幸的是,想在片内实现足够大的存储区能运行在600 MHz会非常昂贵的,如果仍然让片内的存储区运行在300 MHz,那么访问这些存储区的适合会有一个周期的延时。

一个解决方法是使用分层的存储架构,有一个快速的靠近CPU的存储区,访问没有stall但是size很小,往外的内存空间很大,但是离CPU较远,访问需要比较大的stall,靠近CPU的存储区可以视为cache。

访问定位的规律

当然,这种解决方案只有在CPU在大部分的访问都是只针对最靠近它的存储区时才是有效的,幸运的是,根据访问定位的规律,这一条可以保证。访问的定位规律表明程序在一个相对小的时间窗口对仅需要一个相对较小size的数据和代码。数据定位的两条规律:

•空间关联性:当一个数据被访问时,它临近的数据又很大可能会被后续的存储访问;

•时间关联性:一个存储区被访问时,在下一个临近的时间点还会被访问。

空间关联性揭示了计算机程序的创建规律:通常情况下相关的数据被编译链接到临近的连续区域。例如首先处理一个数组的第一个元素,然后处理第二个,这就是空间关联性。类似的,时间关联性主要源于程序中存在占用时间非常多的循环,通常循环的代码被连续执行非常多次,一般循环内访问的数据也相当。

图2是空间关联性的说明,一个6-tap的FIR滤波器的数据访问模式。如计算输出y[0],从输入缓冲区x[]读取6个采样点,当第一个访问发生时,cache控制器读取x[0]以及后续地址的若干个数据(取决于cache line的长度),从速度慢的存储器加载一个cache line的数据需要一定的时钟周期的CPU stall。这种加载的一个动机是x[0]后续的数据后面就要被访问到。这个对于FIR滤波器是显然的,因为后面的5个采样点(x[1]-x[5])就要被用到。后面的这5次存储访问就只需要访问高速cache就可以了。

当计算下一个输出y[1]时,5个采样点(x[1]-x[5])就可以重用了,只有一个采样点(x[6])需要重新加载。所有的采样点都在cache内了,访问时不会有CPU stall了,这也就是刚才提到的时间关联性,即上一步利用的数据在下一次处理中还是可能会被用到的。

Cache就是利用数据访问的时间和空间关联性建立的,它让对速度较慢的外存的访问次数尽可能的降低,而让大部分的数据访问都由更高层次的cache存储区来完成。

存储区的速度

Cache系统通常包含以下3级:

•第一级(L1)在CPU片内,运行在CPU时钟频率;

•第二级(L2)也在片内,但是比L1稍慢,容量较L1大;

•第三级 (L3)是外存,最慢容量也最大。

每一层次的cache有不同的数据访问性能,相对的性能比较可以参考下面的表格。

当处理器从存储区请求数据访问时,首先在最高层次的cache内查找,然后再从次高级别的存储区查找。当请求在cache内时就是cache命中,否则是一次cache miss。因而Cache系统的性能将取决于cache命中的比率。对于任意级别的cache,命中率越高性能越好。比如一个内存访问的L1 cache命中率为70%,L2 20%, 其他来自L3,那么以图3所示的性能下,平均一次内存的访问时间为

(0.7 * 4) + (0.2 * 5) + (0.05 * 30) + (0.05 * 220) = 16.30 ns 考虑图4所示的TI TMS320C64x DSP的存储架构,两级的片内cache加上片外外存。一级Cache分成程序(L1P)和数据(L1D) cache,每个容量为16 Kbytes。L1缓存数据访问不会有存储stall。L2存储区分成L2 SRAM和L2 cache,无论是哪种配置,L2存储区都需要两个CPU周期完成一次数据访问。不同的DSP,L2的容量不同,如TMS320C6454 DSP,L2的大小为1Mbytes。最后是C64x DSP最大高达2GBytes的外存,外存的访问速度取决于使用的存储器类型,但一般外存的频率在100 MHz左右。图4中的所有的cache(红色)和数据通路都由cache控制器自动维护。

Cache的更新

Cache一直是主存的一个拷贝,因而需要cache能随时反映主存的内容。如果数据在cache内被更新,而主存里没有更新,这个cache内的数据就被称为污染(dirty)数据,而数据在主存被更新但是cache内没有更新,这时cache内的数据被称为过时的(stale)数据。

Cache控制器使用一系列的技术来维护cache的一致性。侦听“Snoop”和强制更新“snarf” 是两种常用的技术。侦听是让cache决定主存内的数据的处理影响到被cache的地址的数据。强制更新是把数据从主存拷贝到cache存储器。

Cache通常比主存容量小得多,因而cache最终总会被填满,这时新进入的数据总要代替那些已经在cache内的数据了。有很多种策略决定那些已经在cache内的数据被代替更新如随机代替,先进先出(FIFO)以及最迟不用的策略(LRU),大部分的处理器都采用LRU,即把least-recently-used数据替换为最新的数据。这种策略由于考虑到数据访问的是时间相关性而非常有效。

直接映射的cache

Caches要么是直接映射的“direct-mapped”,要不就是组相关的“set-associative”。图5是C64x的L1P cache,包含了512个32字节的cache lines。每个外存地址总是映射到同一个cache line,如:

•地址0000h 到 001Fh总是映射到cache line 0

•地址0020h 到 003Fh总是映射到cache line 1

•地址3FE0h 到 3FFFh总是映射到cache line 511.

当开始访问地址4000h,cache容量被完全占用,因而地址4000h 到 401fh又映射到cache line 0.

为了保存从外存拷贝的数据信息,每个L1P的cache行包含如下信息:

•有效位,表明当前cacheline是否包含有效数据;

•标签区域,对应于外存地址的高18位,由于每个cache行的数据可以由外存若干地址拷贝而来,如line 0保存可以来自地址0000h 到 001fh的数据也可以来自地址4000h 到 401fh。

•组号,对应于地址的5到13 bit;对于直接映射的cache而言,组号对应于cache line号。这个组号对于组相关的cache是非常复杂的。

当CPU开始访问地址0020h时,假设cache已经被完全被设定无效了(invalidated),即没有cache line包含有效数据。此时cache控制器开始根据当前地址的组(即地址的第5到13比特)来看对应的哪个cache line。对于地址0020h来说是cache line 1.然后cache控制器检查line 1的标签位,确认其是否对应于地址0020h到0039h,最后检查有效位,发现其值为0,即该地址的数据并不在cache内,此时cache控制器标记一次cache miss。这次的miss让控制器从外存加载整个cacheline(0020h-0039h),同时更新标签tag位,并把有效位设置为1,同时加载的数据传递给CPU,此次数据访问结束。

当还需要继续访问地址0020h时,cache控制器会继续检查组号和标签域,并和存在标签RAM的值比较,同时有效位的值为1,意味着此次是一个cache hit。

结语

关于tms320c6748的相关介绍就到这了,如有不足之处欢迎指正。

-

Cache

+关注

关注

0文章

130浏览量

29800 -

TMS320C6748

+关注

关注

3文章

42浏览量

13596

发布评论请先 登录

TMS320C6748/C6748 DSP开发板——广州创龙

【TL6748 DSP申请】基于TMS320C6748的视频监控系统

求TMS320C6748相关资料

TMS320C6748 Fixed/Floating-Poi

TMS320C6748固定和浮点DSP硅修订2.3_2.1_2.0_1.1_1.0_英版

TMS320C6748 TMS320C6748 Fixed/Floating Point DSP

tms320c6748主要参数和原理图 tms320c6748 IO图浅析

TMS320C6748和TMS320C6747芯片对比

TMS320C6748 OMAPL138核心板连接器引脚分布图免费下载

德州仪器DSP的TMS320C6748技术手册

使用TPS650061为TMS320C6742、TMS320C6746和TMS320C6748供电

浅谈tms320c6748最小系统设计和cache配置

浅谈tms320c6748最小系统设计和cache配置

评论